一种与芯片热膨胀相匹配的覆铜陶瓷基板的制作方法

1.本实用新型属于半导体基板技术领域,具体涉及一种与芯片热膨胀相匹配的覆铜陶瓷基板。

背景技术:

2.igbt(insulated gate bipolar transistor,绝缘栅双极型晶体管)功率模块是目前性能最为优良的半导体器件之一。芯片和igbt焊接在衬板(覆铜陶瓷基板)上、衬板与基板(一般为铝板)焊接在一起,并与母排、铝线、环氧树脂、硅胶、塑料管壳共同构成一个完整的igbt模块封装结构。其中,铜瓷结构与芯片热膨胀系数的不匹配是导致封装器件在冷热循环过程中失效的主要原因。因此,铜瓷结构与芯片热膨胀系数(cte)的匹配是半导体器件可靠性设计中用于在冷热循环条件下从源头解决铜瓷结构与芯片接触面裂纹和焊点失效的方法,以显著增强器件的冷热循环可靠性。

3.铜瓷结构的工业化制造方式主要有两种,即直接覆铜陶瓷基板(dcb或称dbc)、活性金属钎焊覆铜陶瓷基板(amb)。dcb是利用铜的含氧共晶液直接将铜敷接在陶瓷上,amb是利用钎焊料将陶瓷板和金属铜箔烧结在一起,相较而言,amb覆铜板性能优异,可靠性强。随着半导体制备技术的革新和新能源汽车产业的发展,以amb覆铜板及第三代半导体芯片所制的igbt模块将会成为市场的主流产品。

4.和第一代、第二代半导体材料相比,以碳化硅(sic)、氮化镓(gan)、氮化铝(aln)等为代表的第三代半导体材料具有宽禁带,高击穿电场、高热导率、高电子饱和速率及更高抗辐射能力,因而更适合于制作高温、高频、抗辐射及大功率器件。

5.常温下,无氧铜、氮化硅瓷片的cte分别约为18.6ppm/k、2.5ppm/k;而第三代半导体芯片碳化硅、氮化镓、氮化铝的cte分别约为3.98ppm/k、3.17ppm/k、4.7ppm/k。现有技术中已知的是,采用较薄的铜片有利于使铜瓷结构cte与芯片cte相匹配,但在amb工艺中具体应该使用多厚的铜片,多厚的瓷片最为有利尚无研究,而cte的匹配对焊接后芯片与覆铜基板的冷热循环可靠性影响很大;此外,生产中采用薄铜很难满足覆铜基板工艺和产品质量的要求。因此,确定合适的铜瓷厚度比尤为重要。

技术实现要素:

6.本实用新型是为解决上述不足进行的,对现有覆铜陶瓷基板的结构进行改进,利用amb技术获得了一种与芯片热膨胀相匹配的覆铜陶瓷基板。本实用新型所采用的技术方案如下:

7.本实用新型提供的与芯片热膨胀相匹配的覆铜陶瓷基板,包括位于中间的至少两层陶瓷层、贴敷在陶瓷层上下表面的焊料结合层、以及设置在焊料层上的铜层。其中,相邻两层陶瓷层之间通过连接层连接,铜层与陶瓷层的铜瓷厚度比为0.10~0.20,焊料结合层包括贴敷陶瓷层的反应层以及贴敷铜层的应力缓冲层。

8.优选的,在本实用新型提供的与芯片热膨胀相匹配的覆铜陶瓷基板中,陶瓷层厚

度为0.2~1mm,铜层厚度为0.02~0.2mm,焊料结合层厚度为5~23μm。

9.优选的,在本实用新型提供的与芯片热膨胀相匹配的覆铜陶瓷基板中,铜层与每层陶瓷层的铜瓷厚度比为0.20。

10.优选的,在本实用新型提供的与芯片热膨胀相匹配的覆铜陶瓷基板中,陶瓷层厚度为0.2~0.5mm;连接层厚度为20~50μm,自上而下依次包括活性金属焊片层、超薄铜层、活性金属焊片层。

11.优选的,在本实用新型提供的与芯片热膨胀相匹配的覆铜陶瓷基板中,超薄铜层的厚度为10~45μm,活性金属焊片层的厚度为2~5μm。

12.优选的,在本实用新型提供的与芯片热膨胀相匹配的覆铜陶瓷基板中,反应层为氮化物层,厚度为0.05~3μm;应力缓冲层为铜与活性金属的合金层,厚度为2~20μm。

13.优选的,在本实用新型提供的与芯片热膨胀相匹配的覆铜陶瓷基板中,陶瓷层为氮化硅瓷片,铜层为铜片。

14.本实用新型的有益效果如下:

15.根据本实用新型提供的覆铜陶瓷基板,一方面,陶瓷层被设置为至少一层,相邻两层陶瓷层间通过增设的连接层连接,解决了当前单层陶瓷片过厚,导致的导热性能差、残余应力大的问题;另一方面,焊料结合层包括贴敷陶瓷层的反应层以及贴敷铜层的应力缓冲层,可有效释放覆铜陶瓷基板在冷热循环条件下产生的热应力,进而提高半导体器件冷热循环可靠性。

16.因此,本实用新型针对第三代半导体芯片,将amb工艺、第三代半导体芯片、高可靠性器件的设计等半导体领域前沿技术结合在一起,对以上技术的发展及对应产品工业化量产具有一定的推动作用。

附图说明

17.图1为现有技术中的覆铜陶瓷基板的结构示意图;

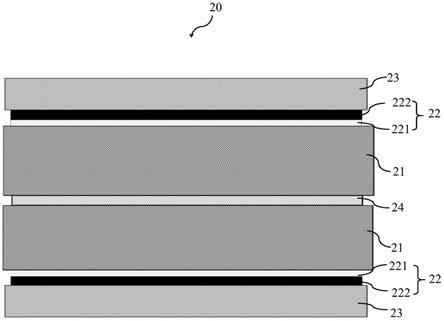

18.图2为本实用新型实施例1中的覆铜陶瓷基板的结构示意图;

19.图3为本实用新型实施例1中的连接层的结构示意图。

具体实施方式

20.下面结合本实用新型的附图和实施例对本实用新型的实施作详细说明,以下实施例是在以本实用新型技术方案为前提下进行实施,给出了详细的实施方式和具体操作过程,但本实用新型的保护范围不限于下述的实施例。

21.试验例1

22.图1显示了现有技术中覆铜陶瓷基板10的结构示意图,包括位于中间的陶瓷层11、贴敷在陶瓷层上下表面的焊料结合层12以及设置在焊料层上的铜层13。

23.陶瓷层11为氮化硅瓷片,铜层13为铜片,铜层与陶瓷层的铜瓷厚度比为0.10~0.35。本实施例中,陶瓷层厚度为0.2~1mm,铜层厚度为0.02~0.35mm,焊料结合层厚度为5~23μm。

24.芯片热膨胀系数与覆铜陶瓷基板的热膨胀系数对比情况如表1所示(计算结果未考虑焊料结合层及其影响,焊料结合层会略微降低铜瓷结构cte):

25.表1芯片热膨胀系数与覆铜陶瓷基板的热膨胀系数对比汇总

[0026][0027][0028]

由表1结果所示,铜瓷厚度比为0.2时,三代半导体芯片中sic与aln与铜瓷结构的cte良好匹配,鉴于瓷厚过厚,铜片过薄对制造工艺要求高、成本大,瓷厚0.6、铜厚0.12是覆铜基板铜瓷搭配较为合理的选择。

[0029]

实施例1

[0030]

针对试验例的结果,本实施例对现有技术中的覆铜陶瓷基板进行改进,主要进行两方面的改进:(1)将陶瓷层改进为多层结构,并在相邻两个陶瓷层间增设连接层;(2)将焊料结合层改进为反应层和应力缓冲层的组合,具体结构如图2所示:

[0031]

覆铜陶瓷基板20包括位于中间的两层陶瓷层21、贴敷在陶瓷层上下表面的焊料结合层22、以及设置在焊料层上的铜层23,相邻两层陶瓷层21之间通过连接层24连接。

[0032]

陶瓷层21优选为氮化硅瓷片,铜层23优选为铜片。本实施例中,铜层23与每层陶瓷层21的铜瓷厚度比为0.20。本实施例中,铜片厚度为0.12mm,瓷片总厚度0.6mm,具体而言,由上往下,铜片:0.12mm、焊料结合层:5μm

‑

15μm、瓷片:0.3mm、连接层:18μm

‑

25μm、瓷片:0.3mm、焊料结合层:5μm

‑

15μm、铜片:0.12mm。

[0033]

根据图3,连接层24烧结前,自上而下依次包括活性金属焊片层241、超薄铜层242、活性金属焊片层243,烧结后形成焊料结合层。超薄铜层242的厚度为10~45μm,活性金属焊片层241的厚度为2~5μm。

[0034]

焊料结合层22包括贴敷陶瓷层的反应层221以及贴敷铜层的应力缓冲层222。反应层221为氮化物层,厚度为0.05~3μm;应力缓冲层222为铜与活性金属的合金层,厚度为2~20μm。

[0035]

本实施例提供的覆铜陶瓷基板,一方面,陶瓷层被设置为至少一层,相邻两层陶瓷层间通过增设的连接层连接,解决了当前单层陶瓷片过厚,导致的导热性能差、残余应力大的问题;另一方面,焊料结合层包括贴敷陶瓷层的反应层以及贴敷铜层的应力缓冲层,可有效释放覆铜陶瓷基板在冷热循环条件下产生的热应力,进而提高半导体器件冷热循环可靠性。

[0036]

以上已对本实用新型创造的较佳实施例进行了具体说明,但本实用新型创造并不限于所述实施例,熟悉本领域的技术人员在不违背本实用新型创造精神的前提下还可作出种种的等同的变型或替换,这些等同的变型或替换均包含在本申请权利要求所限定的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1