整合型沟道分离式功率组件及其制造方法与流程

整合型沟道分离式功率组件及其制造方法

1.相关申请案的交互引用

2.此申请案主张于2019年2月25日由曾军等人提交的美国临时申请序列号为62/810,072的优先权,其通过引用并入本文。

技术领域

3.本发明提供一种沟槽功率半导体组件,例如一种金氧半场效晶体管或一种绝缘闸极双极性晶体管,且更特别地,关于一种整合型沟道分离式金氧半场效晶体管,或做为其他绝缘闸极双极性晶体管的一部分的一种整合型沟道分离式金氧半场效晶体管,或其他功率组件。

背景技术:

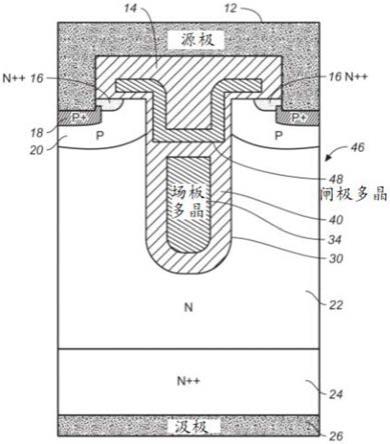

4.图1是已知技术中常见的分离式金氧半场效晶体管(split

‑

gate mosfet)10。金氧半场效晶体管也被称为屏蔽闸金氧半场效晶体管(shielded

‑

gate mosfet)。

5.金氧半场效晶体管10具有金属的源极12。金属的源极12被场氧化层14所绝缘。源极12接触高掺杂n型(n+)源区16及高掺杂p型(p+)接触区18。p型井区20在高掺杂n型源区16与低掺杂n型的漂移区22之间产生垂直通道。低掺杂n型的漂移区22形成在超高掺杂n型(n++)的基板24(汲极)的上方。金属的汲极26接触于基板24的底部。

6.闸极28(掺杂多晶硅)其形成在沟槽30中且通过薄闸极氧化物32绝缘于p型井区20。导电(掺杂多晶硅)的场板34其形成在闸极28的下面且通过场氧化物36绝缘于闸极28。相对厚的场氧化物40将场板34绝缘于低掺杂n型的漂移区22。场板34在图1之外处连接于源极12。

7.当闸极28被施加高于阈值的闸源电压时,沿p型井区20中的沟槽形成了反转层,以在高掺杂n型源区16和低掺杂n型的漂移区22之间形成导电通道,以传导源极12和汲极26之间的电流。

8.金氧半场效晶体管10被期望在用于转换常规应用时具有低转换损失(低闸极电容),并具有低导通电阻及高源极至汲极的崩溃电压。分离式闸极的设计减少转换损失,减少导通电阻及改善崩溃电压。

9.金氧半场效晶体管10将沟槽30中的多晶硅结构区隔为两个电位。闸极28用于形成在p型井区20中的通道,且场板34透过金属互连件电耦接于源电位,以在电流阻断条件下在低掺杂n型漂移区22中产生二维电荷平衡。因为场板34及场氧化物36,相较传统的金氧半场效晶体管10闸极至源极的电容已减少,因此减少转换损失。

10.理想地,对于优化的崩溃电压而言,低掺杂n型的漂移区22会恰好在源极

‑

汲极崩溃电压之前完全耗尽。此为优化的电荷平衡。使用整合型沟道分离式结构更容易实现这一点,其中漂移区22中的固定正电荷抵消了场板34上的负(电子)电荷。

11.场板34和基板24(汲极)形成一电容。此电容使得沿沟槽区域的电场更加分散以提高崩溃电压。因为场板34有效地将闸极28与汲极的电位遮蔽,场板34也降低了闸极至汲极

的电容,以减少转换损失。因为场板34连接到源电位,所以场板34周围的场氧化物40必须承受全部的汲电位。

12.整合型沟道分离技术令低掺杂n型的漂移区22可被高度掺杂或制为较薄来降低导通电阻。

13.图2至图10描绘了用于形成习知金氧半场效晶体管的基本制作流程。

14.图2描绘了热缓冲氧化物成长(通常为200埃(ang))、硬光罩沉积(通过低压化学气相沉积(lp

‑

cvd)通常为4000~8000埃)、沟槽微影蚀刻及硅蚀刻的连续制程的产物,以在磊晶成长在超高n型掺杂浓度的基板24上的低掺杂n型的漂移区22中形成u形沟槽30。

15.图3描绘厚的场氧化物40其在硅平台表面且沿着沟槽30的侧壁及沟槽底部热成长。

16.在图4中,在无任何空隙或缺口下,经掺杂的场板(fp)的多晶硅经沉积而部分地填于沟槽30中。在沉积后,将场板的多晶回蚀到一定深度以形成导电的场板34,从而在沟槽30内有足够的空间,以在稍后于场板34顶部形成隔离场氧化层和闸极结构。

17.在图5中,在无任何空隙或缺口下,隔离的场氧化物36经沉积(通常通过高密度电浆化学气相沉积(hdp

‑

cvd))而填于沟槽30中。在沉积后,场氧化物36被平面化且藉由湿蚀刻、反应离子蚀刻(rie)及/或化学机械研磨(cmp)而回蚀至一定深度,以使剩下的场氧化物36具有足够的厚度来承受闸极至源极的电压。沟槽30内应该要有足够的空间以在场氧化物36的顶部形成闸极结构。

18.在图6中,薄闸氧化物32是由热氧化、沉积或组合方法所制。在此程序后,厚的闸极多晶硅42在没有任何空隙或缺口下经沉积而完全填满沟槽30。需要相对厚的多晶硅(通常为10k埃)来填充沟槽且覆盖硅表面。

19.在图7中,闸极多晶硅42藉由化学机械研磨而移除于硅表面,且通过全面蚀刻而形成凹陷,使其略低于硅平台的表面,以形成闸极28。

20.在图8中,场氧化层14形成在闸极28及硅表面之上。然后硼被植入并活化以形成p型井区20。接着磷被植入并活化以在p型井区20内形成高掺杂n型源区16。

21.在图9中,利用接触微影蚀刻以及蚀刻来将表面的部分的场氧化物14蚀刻掉。

22.在图10中,与图1相同地,高掺杂p型接触区域18是通过在p型井区20中植入及活化硼所形成。硅层是凹陷的,且形成金属的源极12。源极12在剖视图之外接触场板34的多晶。基板24的背面被研磨,且背侧的金属化结构是用于形成汲极26。

23.如图6与图7所示的步骤,相对厚的闸极多晶硅42(通常大约10000埃)是必需的,这显著降低了制造厂(晶圆制造设施)的产能并增加了制造成本。此外,为了平坦化闸极多晶表面,需要多晶化学机械研磨,而这是高劳力的机械制程。多晶化学机械研磨昂贵,且大多数的制造厂无法取得。

24.期待一种制程技术及整合型沟道分离式金氧半场效晶体管结构,其不需要已知技术中厚的闸极多晶硅42以及图6与图7中昂贵的化学机械研磨步骤。如此一来,可增加产能并减少成本,且使更多的制造厂可生产金氧半场效晶体管。也可望减少闸极电容来减少转换损失。

技术实现要素:

25.一种整合型沟道分离式功率半导体组件,例如金氧半场效晶体管结构已被揭露。整合型沟道分离式功率半导体组件具有带顶闸部分的沟槽,当偏压高于阈值电压时,在p型井中产生导电通道。半导体材料可以例如是硅、碳化硅或其他半导体材料。

26.整合型沟道分离式也包括在沟槽中的底层场板,其耦接到源极,用于沿着沟槽散布电场以提高崩溃电压。金氧半场效晶体管可以是任何沟槽式功率组件,例如绝缘闸极双极性晶体管的一部分。

27.顶闸极最初形成为相对薄的、通常为u形的导电材料层,例如多晶硅,以便可以使用非化学机械研磨或其他平面化技术(例如干蚀刻或湿蚀刻)对其进行图案化。因此,金氧半场效晶体管的制造不需要化学机械研磨或昂贵的平面化能力。此外,由此产生的金氧半场效晶体管相较于非整合型沟道分离式金氧半场效晶体管,具有性能上的改进。

28.在一实施例中,薄u形顶闸极具有垂直和横向部分,以在p型井区中分别产生垂直导电信道与横向导电信道,从而降低导通电阻。

29.在其他实施例中,薄顶闸极仅具有沿着沟槽侧壁的垂直部分而非呈u形,以最小化表面面积及顶闸电容。

附图说明

30.图1是已知技术中常见的分离式金氧半场效晶体管的剖视图。

31.图2描绘了通过热缓冲氧化物成长、硬光罩沉积、沟槽微影蚀刻及硅蚀刻等连续制程的产物,以在超高掺杂n型基板上磊晶成长的轻掺杂n型漂移区中形成u形沟槽。

32.图3显示了厚场氧化物其在硅平台表面上、且沿着沟槽侧壁以及沟槽底部热成长。

33.图4显示了经掺杂的场板(fp)多晶硅其经沉积且被回蚀而部分地填于沟槽中。

34.图5显示了隔离场氧化物其经沉积以填于沟槽中并通过湿蚀刻、反应离子蚀刻(rie)及/或化学机械研磨(cmp)而回蚀至一定深度。

35.图6显示了通过热氧化形成的薄栅极氧化物,然后沉积厚闸极多晶硅以在没有任何空隙或缺口下完全填充沟槽。

36.图7显示了通过化学机械研磨而平坦化的闸极多晶硅,然后藉由全面蚀刻将其凹入,使其略低于硅平台面表面,以形成闸极。

37.图8显示了在闸极和硅表面上形成的场氧化层,然后在其中植入和活化硼以形成p型井区,然后植入和活化磷以在p型井区内形成n

‑

i

‑

源区。

38.图9显示了从部分表面所蚀刻的场氧化层。

39.图10是与图1相同且用于显示形成已知技术的金氧半场效晶体管的复数最终步骤。

40.图11显示了本发明的一实施例,其中相对薄的闸极多晶形成一大致u形的多晶衬层但不完全填满沟槽,令制造厂可通过能广泛取得的非化学机械研磨程序(湿或干蚀刻)来对薄闸极多晶进行图案化。

41.图12相同于图4,仅是为了对于接下来的程序作清楚说明的一个起点。

42.图13显示了闸极氧化物其形成在沟槽侧壁和顶部半导体的表面上方,然后沿着沟槽侧壁和顶部半导体表面沉积相对薄的、通常为u形的闸极多晶硅层,但与图6的已知技术

相反地,并不完全填充沟槽。

43.图14显示了闸极多晶是由已知的蚀刻显影(例如:图案化光阻)以及蚀刻(例如:反应离子蚀刻(rie),或四甲基氢氧化铵(tmah)湿蚀刻),而非已知技术的多晶化学机械研磨来形成闸极。

44.图15显示了场氧化物其在闸极及硅表面之上,接着通过植入且活化硼来形成低掺杂p型井区,接着通过植入且活化自我校准磷,以在p型井区中形成n

‑

i

‑

源区。

45.图16显示了蚀刻自部分的半导体表面的场氧化层。

46.图17相同于图11,显示了高掺杂p型接触区形成在p型井区、金属的源极、及汲极。在低掺杂p型井区中闸极形成有横向与垂直通道。

47.图18显示了另一种整合型沟道分离式金氧半场效晶体管,其中沟槽的顶角呈圆形,以增强转角处的闸极至源极的坚固性(降低电场)。

48.图19描绘了沟槽的圆形顶角的形成过程。

49.图20显示了本发明的另一种结构,其直接覆盖场板的闸极多晶部分地被移除,从而可降低闸极至源极的电容。

50.图21除了闸极的底部被完全移除以最小化闸极电容以外,相似于图20。

51.图22显示了本发明的另一实施例的结构,其低掺杂n型区形成在沟槽下方,以纾解沟槽底部附近拥挤的电场,从而改善组件的坚固度。

52.图23显示了本发明的另一实施例的结构,其低掺杂p型区形成在沟槽下方。

53.图24显示了本发明的另一实施例的结构,其复数p型区形成在沟槽下方,以在结合场板的效应时,更好地达成电荷平衡。

54.图25显示了另一结构其仅具有垂直多晶闸极。

55.图26相同于图13,且用于对接下来的程序作清楚说明的一个起点。

56.图27显示了使用无屏蔽(全面)蚀刻来去除横向部分以形成垂直闸极。

57.图28显示了闸极多晶进一步地被凹入以去除可能的多晶残留。

58.图29显示了场氧化层其形成在闸极与半导体表面的上方,接着植入硼并加以活化以形成低掺杂p型井区,接着植入磷并加以活化以在低掺杂p型井区中形成高掺杂n型源区。

59.图30显示了场氧化层蚀刻自半导体表面的复数部分。

60.图31相同于图25,显示高掺杂p型接触区其形成在p型井区中、金属的源极以及汲极。

61.图32绘示了绝缘闸极双极性晶体管其使用整合型沟道分离式金氧半场效晶体管。

62.不同图式中的相同或等效组件标示为相同的符号。

具体实施方式

63.在本发明中,相对薄的闸极多晶硅(下称闸极多晶)(通常为4000埃)使用于形成闸极,且闸极多晶可由传统的蚀刻显影而非由多晶化学机械研磨(cmp)来进行图案化。在效能上具有改善,且组件在没有化学机械研磨的制造厂进行制作,与已知技术比较下也较便宜。完成的整合型沟道分离式金氧半场效晶体管46是显示于图11。

64.任何未特别进行描述的制程步骤可相同于上述提及的习知技术步骤。

65.在图11中,相对薄的闸极多晶硅形成大致呈u形的多晶硅衬垫层,而不是完全填充

沟槽30。然后使用离子反应蚀刻(rie)或其他已知蚀刻来蚀刻薄闸极多晶硅,以形成闸极48。该制程使用薄闸极多晶硅沉积而无需化学机械研磨(cmp),有助于显著提高制造厂的产能并降低成本。此外,形成垂直和横向通道可增强设备的坚固性。

66.本发明的制程流程在沉积闸极多晶硅之前可相同于前述的已知流程。

67.本发明的关键制程流程描绘于图12至图17。

68.图12相同于图4,仅是为了对于接下来的程序作清楚说明的一个起点。

69.在图13中,薄闸极氧化物32是通过热氧化、沉积或组合方法所形成。在沟槽30中存在u形凹部。在此制程后,闸极多晶50被沉积。需要相对薄的多晶硅(通常4000埃)以在沟槽30中形成闸极多晶50,但相反于图6的已知技术,闸极多晶50并不完全填满沟槽30。

70.在图14中,闸极多晶由已知的蚀刻显影(例如图案化光阻)及蚀刻(例如反应离子蚀刻(rie)或四甲基氢氧化铵(tmah)湿蚀刻),而非已知技术的多晶化学机械研磨,来形成大致u形的闸极48。这几乎可用在任何的制造厂。

71.标准制程可用于图15至图17。

72.在图15中,场氧化层14形成于闸极48及半导体表面的上方。然后p型掺杂,例如硼被植入以形成p型井区20。n型掺杂,例如磷接着被植入以在p型井区20内形成nr

‑

源区16。闸极48的边缘会自动更正布植。

73.在图16中,接触微影蚀刻及蚀刻是用于将场氧化层14从部分的半导体表面蚀刻掉。

74.在图17中,相同于图11,高掺杂p型接触区18形成在p型井区20中,例如通过植入硼并加以活化。半导体被凹陷,且形成金属的源极12。金属的源极12是在剖视图以外的平面接触场板34。基板24的背面被研磨,且背侧的金属化是用于形成汲极26。

75.由于闸极4延伸超过了沟槽30的侧壁且覆盖半导体平台的表面,因此导电的垂直及横向通道皆可形成在p型井区20中,以增进组件的坚固度并减少导通电阻。导电通道是在当闸极48相对于源极12以高于阈值电压的正电压施加偏压时所形成。更具体地,闸极48的垂直部分产生穿过p型井区20的垂直通道,其传导大致垂直的电流来通过p型井区20。闸极48的顶部的水平部分产生横向通道,其传导大致横向的电流来通过p型井区20。两个反转层合并,因此高掺杂n型源区16与低掺杂n型的漂移区22之间的导通电阻非常低。这也允许p型井区20具有更高浓度的掺杂以改善崩溃电压。

76.图18显示了另一种整合型沟道分离式金氧半场效晶体管52,其中沟槽54的顶角呈圆形,以增强转角处的闸极至源极的坚固性(降低电场)。

77.图19描绘了沟槽54的圆形顶角的形成制程。其中在使用各向同(isotropic)干蚀刻对场氧化物36进行回蚀期间,沟槽54的顶角可被圆化。

78.图20显示了本发明的另一结构,其中覆盖在场板34上的闸极多晶硅被部分去除,从而可以减少闸极至源极的电容。在这种情况下,闸极56具有两个部分(在横截面平面外互连),其中每个部分垂直和横向地反转p型井区20。闸极56底部的去除降低了闸极电容,从而提高了转换性能。

79.图21除了闸极58的底部被完全移除以最小化闸极电容以外,相似于图20。

80.图22显示了本发明的另一实施例的结构,其中低掺杂n型区60形成在沟槽54下方,以纾解沟槽54底部附近拥挤的电场,从而改善组件的坚固度。低掺杂n型区60的净n型掺杂

浓度是低于低掺杂n型的漂移区22。就在沟槽54部分地蚀刻且局部地补偿低掺杂n型的漂

81.移区22之后,可通过例如将硼植入沟槽54底部来形成低掺杂n型区60。在图22中,由于沟槽54具有圆形的顶边缘,闸极62具有圆形的上部。这减少了场拥挤且纾解了介电需求。

82.图23显示了本发明的另一实施例的结构,其低掺杂p型区64形成在沟槽54下方。低掺杂p型区64伴随着场板34的效应,更好地使结构达成电荷平衡以优化崩溃电压性能。就在沟槽54蚀刻后,可通过将硼植入沟槽54底部以形成低掺杂p型区64。

83.可选地,也可由p型埋入制程来形成低掺杂p型区64。

84.图24显示了本发明的另一实施例的结构,其复数p型区66、68、70形成在沟槽下方,以在结合场板34的效应时,更好地达成电荷平衡。就在沟槽54蚀刻后,可通过将例如硼植入沟槽54底部以形成顶部的p型区66。而其他的p型区68、70可通过p型埋入制程来形成。可选地,p型区66、68、70都可通过p型埋入制程来形成。加入的低掺杂n型飘移区72及74可在p型埋入制程的期间形成。低掺杂n型的漂移区22、72及74的掺杂浓度可彼此相同或不同,以得到最佳的组件性能。可选地,更高掺杂的低掺杂n型缓冲层76可介于最深的p型区70以及超高掺杂n型(n++)的基板24之间。

85.全部的p型区66、68、70可垂直地互相连接或彼此断开。

86.可选地,p型区70可延展到超高掺杂n型的基板24内。

87.复数的n型及p型区可以是多于两个或更多的区。

88.图25显示了另一结构其仅具有垂直多晶的闸极78。在平台上与在沟槽30内闸极的多晶的横向部分在自我校正的行为下被完全移除的期间,可通过无屏蔽(全面)蚀刻(在图13的步骤后)来形成闸极78。只有垂直通道会沿着沟槽30的侧壁形成在p型井区20中。高掺杂n型源极16必会抵于沟槽30的侧壁。没有了横向信道,可减少单元间距。在此设计中闸极至源极的电容可大幅地减少。场板34位于多晶闸极78的下方。

89.在闸极多晶硅图案化之前,本替代实施例的制程流程可相同于图2至5、12及13。为了简洁起见,这些制程不再重复描述。

90.本替代实施例的一范例可见于图26至图31。

91.图26相同于图13,且用于对接下来的程序作清楚说明的一个起点。

92.在图27中,使用无屏蔽(全面)蚀刻来去除闸极多晶50(图26)的横向部分以形成垂直的闸极78。在半导体平台上的闸极氧化物80可做为蚀刻的停止点。

93.在图28中,闸极多晶进一步地被凹陷以去除可能的多晶残留。最终,闸极78的顶面略低于半导体平台。

94.标准的制程可用于图29至31。

95.在图29中,场氧化层14形成在闸极78与半导体表面上。接着硼被植入且被活化以形成p型井区20。磷接着被植入并被活化以在p型井区20中形成高掺杂n型源区16。

96.在图30中,接触微影蚀刻及蚀刻被用于将场氧化层14从部分的半导体表面蚀刻掉。

97.应注意的是前述制程步骤可按任意顺序执行。

98.图31相同于图25,高掺杂p型接触区18其是藉由植入并活化硼来形成在p型井区20中。半导体被凹陷,且形成一金属的源极12。源极12是在剖视图平面以外接触场氧化物40。

基板24的背面被研磨,且背侧的金属化是用于形成汲极26。

99.由于在半导体平台上没有横向的闸极的多晶,所以仅可形成垂直通道。此外,在沟槽内的闸极的多晶的横向部分可自动地被蚀刻掉,因此闸极至源极的电容可减少到最小。

100.本发明的技术也可用于任何沟槽的闸极组件,例如绝缘闸极双极性晶体管(igbt)或其他组件。在绝缘闸极双极性晶体管中,绝缘闸极双极性晶体管的金氧半场效晶体管部分是用于启动再生动作以打开垂直npn和pnp晶体管。

101.图32绘示了绝缘闸极双极性晶体管82其使用图11的整合型沟道分离式金氧半场效晶体管的设计,但也可由任何在此揭露的金氧半场效晶体管来取代。在图32中,基板84是p型以在沟槽闸极组件中形成垂直的npn及pnp双极晶体管。高掺杂p型的基板84接着作为pnp晶体管的一个收集器。源极12也可做为针对npn晶体管的一个发射器,且汲极26也可做为一个收集电极。可增加一n型缓冲层86其具有高于低掺杂的漂移区22的掺杂浓度。

102.所有图中的比例都是为了简单起见,层厚和区域大小将与以上图式中所显示的不同。最佳厚度、尺寸和掺杂浓度可透过模拟来确定。

103.任何的揭露特征可在金氧半场效晶体管、绝缘闸极双极性晶体管或其他沟槽闸极组件中以任何方式进行组合,以针对特定应用达成该特征的特定优点。

104.可以使所有层/区域的导电性相反以形成p型通道的金氧半场效晶体管而非n型通道的金氧半场效晶体管。

105.尽管在范例中假设为硅,但半导体材料可以替代地为碳化硅、硅锗或其他类似材料。

106.虽然本发明已描述及示出一些特定实施例,但对于本技术领域人士而言,在不背离本发明的更广泛方面的情况下所进行之改变及修改是显而易见的。因此,所附申请专利范围是涵盖在本发明的真正精神和范围内的所有变化及修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1