一种具有高容量电容结构的阵列基板及其制备方法与流程

1.本发明涉及阵列基板技术领域,特别涉及一种具有高容量电容结构的阵列基板及其制备方法。

背景技术:

2.随着有源矩阵有机发光二极管显示器(amoled)和高性能有源矩阵液晶显示器(amlcd)中的发展,为了得到高分辨率和高帧速的显示器,因此如何设计和制备高性能且小尺寸的阵列基板结构成为越来越需要被攻克的研究课题。

3.igzo是一种含有铟、镓和锌的非晶氧化物,载流子迁移率是非晶硅的20

‑

30倍,可以大大提高tft(英文全称为thin film transistor,薄膜场效应晶体管)对像素电极的充放电速率,提高像素的响应速度,具备更快的面板刷新频率,可实现超高分辨率显示面板。同时,现有的非晶硅生产线只需稍加改动即可兼容igzo制程,因此在成本方面较低温多晶硅(ltps)更有竞争力。

4.氧化物半导体迁移率(10

‑

30cm2/v.s)可满足amoled显示阵列基板驱动需求,且igzo tft器件相对低温多晶硅tft拥有更优越的ioff,画素tft只需要单栅极就可抑制漏电问题,有更利于tft器件的小型化,实现超高分辨率tft基板的制作。因此,搭配igzo tft驱动电路的高分辨率oled显示器市场前景很好,为目前国内外主要面板制造厂研发热点。

5.goa技术(goa:gate driver ic on array)是近年面板发展的一种新类型,其把驱动gate信号的ic直接刻蚀在面板上,省去了gate driver ic的成本和把ic绑定在面板上的工序,更重要的是由于gate driver ic与显示面板为一个整体,使得产品更薄、分辨率更高、稳定性和抗振性更好。目前,goa技术已经成为移动终端业的主流,智能手机几乎都使用这种液晶面板。

6.在阵列基板中为了使驱动电路具有更好的稳压效果,通常需要设置较大容量电容,这就造成驱动电路的占用面积较大无法进一步缩小显示面板边框尺寸,以及画素大小。

技术实现要素:

7.本发明所要解决的技术问题是:提供一种具有高容量电容结构的阵列基板。

8.为了解决上述技术问题,本发明采用的第一种技术方案为:

9.一种具有高容量电容结构的阵列基板,包括玻璃基板和设置在玻璃基板一侧面的缓冲层,所述缓冲层远离玻璃基板的一侧面的电容区域开设有至少一个的凹槽,所述凹槽中填充有第一电极层,所述第一电极层远离缓冲层的一侧面上依次层叠覆盖有第一绝缘层、第二电极层、第一蚀刻阻挡层、第三电极层和第一钝化层;

10.所述缓冲层远离玻璃基板的一侧面的tft区域上依次层叠覆盖有第一透明导电层、栅极金属层、栅极绝缘层、有源层、第二透明导电层、源漏极金属层和第二钝化层,所述第二透明导电层上开设有第一过孔,所述源漏极金属层上开设有第二过孔,所述第二过孔与第一过孔相对设置且相通,所述第一过孔和第二过孔中均填充有第二钝化层;

11.所述第一电极层的材质与第一透明导电层的材质相同;

12.所述第二电极层的材质与有源层的材质相同;

13.所述第三电极层的材质与第二透明导电层的材质相同。

14.本发明采用的第二种技术方案为:

15.一种具有高容量电容结构的阵列基板的制备方法,包括以下步骤:

16.s1、提供一玻璃基板,在所述玻璃基板表面覆盖有缓冲层;在所述缓冲层远离玻璃基板的一侧面的电容区域形成至少一个的凹槽;

17.s2、形成第一电极层和第一透明导电层,所述第一电极层填充于凹槽内,所述第一透明导电层覆盖于缓冲层远离玻璃基板的一侧面的tft区域上;

18.s3、形成栅极金属层,所述栅极金属层覆盖于第一透明导电层表面;

19.s4、形成第一绝缘层和栅极绝缘层,所述第一绝缘层覆盖于第一电极层表面,所述栅极绝缘层覆盖于栅极金属层表面;

20.s5、形成第二电极层和有源层,所述第二电极层覆盖于第一绝缘层表面,所述有源层覆盖于栅极绝缘层表面;

21.s6、形成第一蚀刻阻挡层,所述第一蚀刻阻挡层覆盖于第二电极层表面;

22.s7、形成第三电极层和第二透明导电层,所述第三电极层覆盖于第一蚀刻阻挡层表面,所述第二透明导电层覆盖于有源层表面;在所述第二透明导电层中形成第一过孔;

23.s8、形成源漏极金属层,所述源漏极金属层覆盖于第二蚀刻阻挡层表面;在源漏极金属层中形成第二过孔,所述第二过孔与第一过孔相对设置且相通;

24.s9、形成第一钝化层和第二钝化层,所述第一钝化层覆盖于第三电极层表面,所述第二钝化层覆盖于源漏极金属层表面,且所述第一过孔和第二过孔中均填充有第二钝化层。

25.本发明的有益效果在于:

26.通过在缓冲层远离玻璃基板的一侧面的电容区域开设有至少一个的凹槽,凹槽中填充有第一电极层,第一电极层远离缓冲层的一侧面上依次层叠覆盖有第一绝缘层、第二电极层、第一蚀刻阻挡层、第三电极层和第一钝化层,第一电极层、第二电极层和第三电极层分别作为电容的电极层,第一电极层、第一绝缘层和第二电极层构成一个电容,第二电极层、第一蚀刻阻挡层和第三电极层构成一个电容,以形成两个并联的电容,从而进一步增大了电容容量;在缓冲层远离玻璃基板的一侧面的tft区域上覆盖有第一透明导电层,第一透明导电层位于缓冲层和栅极金属层之间,且第一电极层的材质与第一透明导电层的材质相同,这样能够进一步提高电容容量,同时也能减小电容的占用面积,具有提高面板ppi(pixels per inch,每英寸对角线上所拥有的像素)、缩小面板边框尺寸的优势。

附图说明

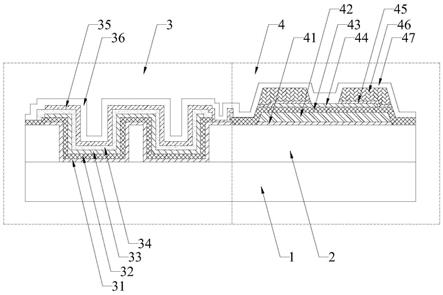

27.图1为根据本发明的一种具有高容量电容结构的阵列基板的结构示意图;

28.图2为根据本发明的一种具有高容量电容结构的阵列基板的结构示意图;

29.图3为根据本发明的一种具有高容量电容结构的阵列基板的制备方法的步骤流程图;

30.图4为根据本发明的一种具有高容量电容结构的阵列基板的制备方法的工艺流程

图;

31.图5为根据本发明的一种具有高容量电容结构的阵列基板的制备方法的第一电极层和第一透明导电层的工艺流程图;

32.图6为根据本发明的一种具有高容量电容结构的阵列基板的制备方法的第一绝缘层和第二电极层的工艺流程图;

33.标号说明:

34.1、玻璃基板;

35.2、缓冲层;

36.3、电容区域;31、第一电极层;32、第一绝缘层;33、第二电极层;34、第一蚀刻阻挡层;35、第三电极层;36、第一钝化层;37、凹槽;

37.4、tft区域;41、第一透明导电层;42、栅极金属层;43、栅极绝缘层;44、有源层;45、第二透明导电层;46、源漏极金属层;47、第二钝化层;48、第二蚀刻阻挡层。

具体实施方式

38.为详细说明本发明的技术内容、所实现目的及效果,以下结合实施方式并配合附图予以说明。

39.请参照图1,本发明提供的一种技术方案:

40.一种具有高容量电容结构的阵列基板,包括玻璃基板和设置在玻璃基板一侧面的缓冲层,所述缓冲层远离玻璃基板的一侧面的电容区域开设有至少一个的凹槽,所述凹槽中填充有第一电极层,所述第一电极层远离缓冲层的一侧面上依次层叠覆盖有第一绝缘层、第二电极层、第一蚀刻阻挡层、第三电极层和第一钝化层;

41.所述缓冲层远离玻璃基板的一侧面的tft区域上依次层叠覆盖有第一透明导电层、栅极金属层、栅极绝缘层、有源层、第二透明导电层、源漏极金属层和第二钝化层,所述第二透明导电层上开设有第一过孔,所述源漏极金属层上开设有第二过孔,所述第二过孔与第一过孔相对设置且相通,所述第一过孔和第二过孔中均填充有第二钝化层;

42.所述第一电极层的材质与第一透明导电层的材质相同;

43.所述第二电极层的材质与有源层的材质相同;

44.所述第三电极层的材质与第二透明导电层的材质相同。

45.从上述描述可知,本发明的有益效果在于:

46.通过在缓冲层远离玻璃基板的一侧面的电容区域开设有至少一个的凹槽,凹槽中填充有第一电极层,第一电极层远离缓冲层的一侧面上依次层叠覆盖有第一绝缘层、第二电极层、第一蚀刻阻挡层、第三电极层和第一钝化层,第一电极层、第二电极层和第三电极层分别作为电容的电极层,第一电极层、第一绝缘层和第二电极层构成一个电容,第二电极层、第一蚀刻阻挡层和第三电极层构成一个电容,以形成两个并联的电容,从而进一步增大了电容容量;在缓冲层远离玻璃基板的一侧面的tft区域上覆盖有第一透明导电层,第一透明导电层位于缓冲层和栅极金属层之间,且第一电极层的材质与第一透明导电层的材质相同,这样能够进一步提高电容容量,同时也能减小电容的占用面积,具有提高面板ppi、缩小面板边框尺寸的优势。

47.进一步的,所述有源层与第二透明导电层之间还设有第二蚀刻阻挡层,所述第二

蚀刻阻挡层分别与有源层、第二透明导电层和第二钝化层接触。

48.由上述描述可知,通过在有源层与第二透明导电层之间设置第二蚀刻阻挡层,能够进一步提高电容容量。

49.进一步的,所述第一电极层的材质为氧化铟锡,所述第一电极层的厚度范围为

50.由上述描述可知,第一电极层采用氧化铟锡,且第一电极层的厚度范围为能够进一步提高电容容量。

51.进一步的,所述凹槽中的第一电极层与玻璃基板接触。

52.进一步的,所述凹槽的竖直截面形状为方形。

53.请参照图3,本发明提供的另一种技术方案:

54.一种具有高容量电容结构的阵列基板的制备方法,包括以下步骤:

55.s1、提供一玻璃基板,在所述玻璃基板表面覆盖有缓冲层;在所述缓冲层远离玻璃基板的一侧面的电容区域形成至少一个的凹槽;

56.s2、形成第一电极层和第一透明导电层,所述第一电极层填充于凹槽内,所述第一透明导电层覆盖于缓冲层远离玻璃基板的一侧面的tft区域上;

57.s3、形成栅极金属层,所述栅极金属层覆盖于第一透明导电层表面;

58.s4、形成第一绝缘层和栅极绝缘层,所述第一绝缘层覆盖于第一电极层表面,所述栅极绝缘层覆盖于栅极金属层表面;

59.s5、形成第二电极层和有源层,所述第二电极层覆盖于第一绝缘层表面,所述有源层覆盖于栅极绝缘层表面;

60.s6、形成第一蚀刻阻挡层,所述第一蚀刻阻挡层覆盖于第二电极层表面;

61.s7、形成第三电极层和第二透明导电层,所述第三电极层覆盖于第一蚀刻阻挡层表面,所述第二透明导电层覆盖于有源层表面;在所述第二透明导电层中形成第一过孔;

62.s8、形成源漏极金属层,所述源漏极金属层覆盖于第二蚀刻阻挡层表面;在源漏极金属层中形成第二过孔,所述第二过孔与第一过孔相对设置且相通;

63.s9、形成第一钝化层和第二钝化层,所述第一钝化层覆盖于第三电极层表面,所述第二钝化层覆盖于源漏极金属层表面,且所述第一过孔和第二过孔中均填充有第二钝化层。

64.从上述描述可知,本发明的有益效果在于:

65.通过在缓冲层远离玻璃基板的一侧面的电容区域开设有至少一个的凹槽,凹槽中填充有第一电极层,第一电极层远离缓冲层的一侧面上依次层叠覆盖有第一绝缘层、第二电极层、第一蚀刻阻挡层、第三电极层和第一钝化层,第一电极层、第二电极层和第三电极层分别作为电容的电极层,第一电极层、第一绝缘层和第二电极层构成一个电容,第二电极层、第一蚀刻阻挡层和第三电极层构成一个电容,以形成两个并联的电容,从而进一步增大了电容容量;在缓冲层远离玻璃基板的一侧面的tft区域上覆盖有第一透明导电层,第一透明导电层位于缓冲层和栅极金属层之间,且第一电极层的材质与第一透明导电层的材质相同,这样能够进一步提高电容容量,同时也能减小电容的占用面积,具有提高面板ppi、缩小面板边框尺寸的优势。

66.进一步的,步骤s6还包括以下步骤:

67.形成第二蚀刻阻挡层,且覆盖于有源层表面,所述第二蚀刻阻挡层分别与有源层、第二透明导电层和第二钝化层接触。

68.从上述描述可知,通过在有源层与第二透明导电层之间设置第二蚀刻阻挡层,能够进一步提高电容容量。

69.进一步的,所述第一电极层的材质为氧化铟锡,所述第一电极层的厚度范围为

70.从上述描述可知,第一电极层采用氧化铟锡,且第一电极层的厚度范围为能够进一步提高电容容量。

71.进一步的,所述凹槽中的第一电极层与玻璃基板接触。

72.进一步的,所述凹槽的竖直截面形状为方形。

73.请参照图1和图2,本发明的实施例一为:

74.请参照图1,一种具有高容量电容结构的阵列基板,包括玻璃基板1和设置在玻璃基板1一侧面的缓冲层2,所述缓冲层2远离玻璃基板1的一侧面的电容区域3开设有至少一个的凹槽37,所述凹槽37中填充有第一电极层31,所述第一电极层31远离缓冲层2的一侧面上依次层叠覆盖有第一绝缘层32、第二电极层33、第一蚀刻阻挡层34、第三电极层35和第一钝化层36,形成立体栅状式电容,通过立体栅状式电容相比原有平板式电容可以有效降低电容区的占用面积,保持相同的容量情况下,缩小电容尺寸;

75.所述缓冲层2远离玻璃基板1的一侧面的tft区域4上依次层叠覆盖有第一透明导电层41、栅极金属层42、栅极绝缘层43、有源层44、第二透明导电层45、源漏极金属层46和第二钝化层47,所述第二透明导电层45上开设有第一过孔,所述源漏极金属层46上开设有第二过孔,所述第二过孔与第一过孔相对设置且相通,所述第一过孔和第二过孔中均填充有第二钝化层47;

76.所述第一电极层31的材质与第一透明导电层41的材质相同;所述第一透明导电层41的厚度范围为优选为

77.所述第二电极层33的材质与有源层44的材质相同;

78.所述第三电极层35的材质与第二透明导电层45的材质相同。

79.请参照图2,所述有源层44与第二透明导电层45之间还设有第二蚀刻阻挡层48,所述第二蚀刻阻挡层48分别与有源层44、第二透明导电层45和第二钝化层47接触。

80.所述第一电极层31的材质为氧化铟锡,所述第一电极层31的厚度范围为优选为

81.所述凹槽37中的第一电极层31与玻璃基板1接触。

82.所述凹槽37的竖直截面形状为方形或半圆柱形。

83.所述缓冲层2的厚度范围为0.2μm

‑

3μm,优选为2μm;所述缓冲层2可选的材料为有机光敏材料、pi、siox、sinx、氧化钛等一种或多种;

84.所述栅极金属层42的厚度范围为优选为所述栅极金属层42的材料可选用铝、钼、钛、镍、铜、银、铬等导电性优良金属一种或多种,以及合金;

85.所述第一绝缘层32的厚度范围为优选为所述栅极绝缘层43的厚度范围为优选为所述第一绝缘层32和栅极绝缘层43的材料相同,可选siox、sinx、氧化钛、氧化铝等;

86.所述第二电极层33的厚度范围为优选为所述有源层的厚度范围为优选为所述第二电极层33和有源层44的材料相同,可选igzo、izo、igzto等金属氧化物;

87.所述第三电极层35的厚度范围为优选为所述第三电极层35和第二透明导电层45的材料相同,可采用氧化铟锡;

88.所述第一蚀刻阻挡层34的厚度范围为优选为所述第二蚀刻阻挡层48的厚度范围为优选为所述第一蚀刻阻挡层34和第二蚀刻阻挡层48的材料相同,可选siox、sinx、氧化钛、氧化铝等;

89.所述源漏极金属层46的材料可选用铝、钼、钛、镍、铜、银、铬等导电性优良金属一种或多种,以及合金;

90.所述第一钝化层36的厚度范围为优选为所述第二钝化层47的厚度范围为优选为所述第一钝化层36和第二钝化层47的材料相同,可选siox、sinx、氧化钛、氧化铝等;

91.所述第二透明导电层45的厚度范围为优选为所述第二透明导电层45的材料采用氧化铟锡,通过以氧化铟锡作为桥接连接有源层44与源漏极金属层46可以减少欧姆接触阻值,提高tft电学性能;

92.上述提及的所有结构层,在实际工艺施作过程中,所述第一电极层31和第一透明导电层41为分布在不同区域的同一膜层,在进行蒸镀制程是同时制作形成的;

93.所述第一绝缘层32和栅极绝缘层43为分布在不同区域的同一膜层,在进行蒸镀制程是同时制作形成的;

94.所述第二电极层33和有源层44为分布在不同区域的同一膜层,在进行蒸镀制程是同时制作形成的;

95.所述第一蚀刻阻挡层34和第二蚀刻阻挡层48为分布在不同区域的同一膜层,在进行蒸镀制程是同时制作形成的;

96.所述第三电极层35和第二透明导电层45为分布在不同区域的同一膜层,在进行蒸镀制程是同时制作形成的;

97.所述第一钝化层36和第二钝化层47为分布在不同区域的同一膜层,在进行蒸镀制程是同时制作形成的;

98.本方案设计的具有高容量电容结构的阵列基板,在保持容量相等的情况下,立体栅状式电容实际占用面积较平板式电容,理论上电容面积可再进一步缩减50%。

99.请参照图3至图6,本发明的实施例二为:

100.请参照图3,一种具有高容量电容结构的阵列基板的制备方法,包括以下步骤:

101.s1、提供一玻璃基板1,在所述玻璃基板1表面覆盖有缓冲层2;在所述缓冲层2远离

玻璃基板1的一侧面的电容区域3形成至少一个的凹槽37;

102.s2、形成第一电极层31和第一透明导电层41,所述第一电极层31填充于凹槽37内,所述第一透明导电层41覆盖于缓冲层2远离玻璃基板1的一侧面的tft区域4上;

103.s3、形成栅极金属层42,所述栅极金属层42覆盖于第一透明导电层41表面;

104.s4、形成第一绝缘层32和栅极绝缘层43,所述第一绝缘层32覆盖于第一电极层31表面,所述栅极绝缘层43覆盖于栅极金属层42表面;

105.s5、形成第二电极层33和有源层44,所述第二电极层33覆盖于第一绝缘层32表面,所述有源层44覆盖于栅极绝缘层43表面;

106.s6、形成第一蚀刻阻挡层34,所述第一蚀刻阻挡层34覆盖于第二电极层33表面;

107.s7、形成第三电极层35和第二透明导电层45,所述第三电极层35覆盖于第一蚀刻阻挡层34表面,所述第二透明导电层45覆盖于有源层44表面;在所述第二透明导电层45中形成第一过孔;

108.s8、形成源漏极金属层46,所述源漏极金属层46覆盖于第二蚀刻阻挡层48表面;在源漏极金属层46中形成第二过孔,所述第二过孔与第一过孔相对设置且相通;

109.s9、形成第一钝化层36和第二钝化层47,所述第一钝化层36覆盖于第三电极层35表面,所述第二钝化层47覆盖于源漏极金属层46表面,且所述第一过孔和第二过孔中均填充有第二钝化层47。

110.步骤s6还包括以下步骤:

111.形成第二蚀刻阻挡层48,且覆盖于有源层44表面,所述第二蚀刻阻挡层48分别与有源层44、第二透明导电层45和第二钝化层47接触。

112.所述第一电极层31的材质为氧化铟锡,所述第一电极层31的厚度范围为

113.所述凹槽37中的第一电极层31与玻璃基板1接触。

114.所述凹槽37的竖直截面形状为方形或半圆柱形。

115.上述的具有高容量电容结构的阵列基板的制备方法的具体实施例为:

116.1、在玻璃基板1上制作缓冲层2,并显影出复数个条形栅状结构(请参照图4的(a));

117.2、在玻璃基板1之上成膜第一透明导电层41制作栅极驱动电路以及电容区域3的第一电极层31(请参照图4的(b));

118.3、连续成膜栅极绝缘层43以及在栅极上制作有源层44,并图案化(请参照图4的(c));

119.4、在有源层44上制作蚀刻阻挡层,保护有源层44沟道并在tft区蚀刻出过孔露出有源层44表面连接有源层44与源极/漏极(即源漏极金属层46),在电容区蚀刻出过孔露出栅极金属层42表面(请参照图4的(d));

120.5、制作源极/漏极电路与电容区域3的第二电极层33(请参照图4的(e));

121.6、在源极/漏极之上制作钝化层,保护tft以及阵列基板不受水氧破坏(请参照图4的(f))。

122.所述第一电极层31和第一透明导电层41的具体施作步骤如下:

123.1、连续成膜透明导电层以及金属膜层,透明导电层可优选ito,这里不对材料特殊

限制,金属膜层可选用铝、钼、钛、镍、铜、银、铬等导电性优良金属一种或多种,以及合金(请参照图5中的(a));

124.2、利用半色掩膜板进行曝光,电容区光线透过率为50%,栅极走线区透过率0%,其他区域100%(请参照图5中的(b));

125.3、在光阻层曝光后利用显影液显影,光罩100%透过率区光阻完全去除,50%与0%透过率区光阻仍保留,且50%透光率区光阻相较于0%透光区光阻会减薄(请参照图5中的(c));

126.4、对膜层进行蚀刻初步转印光罩图案,透明导电层以及金属膜层蚀刻根据膜质材料可以一次性蚀刻或二次蚀刻(请参照图5中的(d));

127.5、通过灰化处理去除50%透光率区光阻(请参照图5中的(e));

128.6、灰化处理后再次进行蚀刻,通过蚀刻时间控制或蚀刻药液的选择性去除50%透光率区上方金属,保留下方ito,之后除去剩余光阻完成图案转移(请参照图5中的(f));

129.所述第一绝缘层32(栅极绝缘层43)和第二电极层33(有源层44)的具体施作步骤如下:

130.1、在栅极金属层42之上连续成膜栅极绝缘层43(第一绝缘层32)和有源层44(请参照图6中的(a));

131.2、利用半色掩膜版进行曝光,电容区光线透过率为50%,栅极走线区透过率0%,其他区域100%(请参照图6中的(b));

132.3、在光阻层曝光后利用显影液显影,光罩100%透过率区光阻完全去除,50%与0%透过率区光阻仍保留,且50%透光率区光阻相较于0%透光区光阻会减薄(请参照图6中的(c));

133.4、对膜层进行蚀刻初步转印光罩图案(请参照图6中的(d));

134.5、通过灰化处理去除50%透光率区光阻,并通过氢离子注入方式使电极区氧化物膜层导体化,以及改善tft区氧化物与源漏极欧姆接触特性,减小接触电阻(请参照图6中的(e));

135.6、剩余光阻完成图案转移(请参照图6中的(f))。

136.综上所述,本发明提供的一种具有高容量电容结构的阵列基板及其制备方法,通过在缓冲层远离玻璃基板的一侧面的电容区域开设有至少一个的凹槽,凹槽中填充有第一电极层,第一电极层远离缓冲层的一侧面上依次层叠覆盖有第一绝缘层、第二电极层、第一蚀刻阻挡层、第三电极层和第一钝化层,第一电极层、第二电极层和第三电极层分别作为电容的电极层,第一电极层、第一绝缘层和第二电极层构成一个电容,第二电极层、第一蚀刻阻挡层和第三电极层构成一个电容,以形成两个并联的电容,从而进一步增大了电容容量;在缓冲层远离玻璃基板的一侧面的tft区域上覆盖有第一透明导电层,第一透明导电层位于缓冲层和栅极金属层之间,且第一电极层的材质与第一透明导电层的材质相同,这样能够进一步提高电容容量,同时也能减小电容的占用面积,具有提高面板ppi、缩小面板边框尺寸的优势。

137.以上所述仅为本发明的实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等同变换,或直接或间接运用在相关的技术领域,均同理包括在本发明的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1