形成半导体元件的方法与流程

1.本发明涉及半导体技术领域,特别是涉及一种形成半导体元件的方法。

背景技术:

2.先进的互补金属氧化物半导体(cmos)元件多已普遍地采用金属栅极,以避免“多晶硅损耗”和“硼渗透”效应。用作栅极材料的特定金属的选择受到许多因素的影响,例如,所希望的功函数和电阻率、栅极介电层类型、栅极金属预计要承受的热负荷(thermal budget)等等。在“双金属/双功函数”cmos制作方法中,通常分别使用适合p-fet的栅极金属(高功函数)和适合n-fet的栅极金属(低功函数)。

3.通常,cmos元件的金属栅极由纯金属或合金、金属或金属合金硅化物或者含有金属的导电氧化物或硅化物的一层或多层构成,这些层中的至少一层与栅极介电层接触。双层金属栅极包括,例如,薄底部“覆层”或“功函数设置”层(与下面的栅极介电层接触)以及提供良好的导电性的厚上部“填充层”。

4.例如,现有的一种作法是先形成氮化钽阻障层,然后在氮化钽阻障层上沉积氮化钛层作为p功函数层,然后以光致抗蚀剂层遮盖住pmos区域,再以蚀刻方式去除nmos区域的氮化钛层,然后进行n功函数层的沉积等步骤,然而,上述作法的缺点在于,以蚀刻方式去除nmos区域的氮化钛层时,可能会产生氮化钛残留物,此外,以蚀刻方式去除nmos区域的氮化钛层易损伤到下方的氮化钽阻障层。

技术实现要素:

5.本发明的主要目的在于提供一种半导体元件的制作方法,以解决上述现有技术的不足和缺点。

6.本发明一方面提供一种形成半导体元件的方法,包括:提供一基底,具有一第一元件区域和一第二元件区域;沉积一金属氮化物阻障层,覆盖所述第一元件区域和所述第二元件区域;沉积一钛层,在所述金属氮化物阻障层上;从所述第二元件区域中选择性地去除所述钛层,从而显露出所述第二元件区域中的所述金属氮化物阻障层;以及将所述第一元件区域中的所述钛层转变为一氮化钛层,其中,所述氮化钛层是所述第一元件区域中的一功函数层。

7.根据本发明实施例,所述的方法还包括:在所述基底上形成一介电层;以及在所述介电层中形成一沟槽。

8.根据本发明实施例,所述金属氮化物阻障层顺形地覆盖所述介电层和所述沟槽的内表面。

9.根据本发明实施例,所述的方法还包括:在沉积所述金属氮化物阻障层之前,形成一高介电常数介电层。

10.根据本发明实施例,所述第一元件区域是pmos区域,并且所述第二元件区域是nmos区域。

11.根据本发明实施例,通过使用稀释的氢氟酸溶液或过氧化氢-硫酸混合液(spm)从所述第二元件区域选择性地去除所述钛层。

12.根据本发明实施例,所述的方法还包括:在将所述第一元件区域中的所述钛层转变成所述氮化钛层之后,在所述第一元件区域和所述第二元件区域上沉积一n功函数金属层。

13.根据本发明实施例,所述n功函数金属层包括钛铝。

14.根据本发明实施例,所述的方法还包括:在所述n功函数金属层上沉积一间隙填充导电层。

15.根据本发明实施例,所述间隙填充导电层包括铝或钨。

附图说明

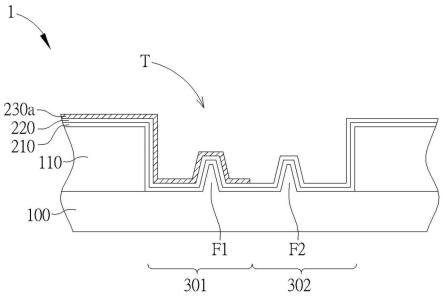

16.图1至图7为本发明实施例所绘示的一种形成半导体元件的方法示意图。

17.主要元件符号说明

18.1半导体元件

19.100基底

20.110介电层

21.210高介电常数介电层

22.220金属氮化物阻障层

23.230钛层

24.230a氮化钛层

25.250底部抗反射层

26.260光致抗蚀剂图案

27.280n功函数金属层

28.290间隙填充导电层

29.301第一元件区域

30.302第二元件区域

31.f1鳍状结构

32.f2鳍状结构

33.t沟槽

具体实施方式

34.在下文中,将参照附图说明细节,该些附图中的内容也构成说明书细节描述的一部分,并且以可实行该实施例的特例描述方式来绘示。下文实施例已描述足够的细节使该领域的一般技术人员得以具以实施。

35.当然,也可采行其他的实施例,或是在不悖离文中所述实施例的前提下作出任何结构性、逻辑性、及电性上的改变。因此,下文的细节描述不应被视为是限制,反之,其中所包含的实施例将由随附的权利要求来加以界定。

36.请参阅图1至图7,其为根据本发明实施例所绘示的一种形成半导体元件1的方法示意图。根据本发明实施例,半导体元件1可以是cmos元件。如图1所示,首先提供一基底

100,例如,硅基底,但不限于此。基底100上至少具有一第一元件区域301和一第二元件区域302。根据本发明实施例,例如,第一元件区域301是pmos区域,并且第二元件区域302是nmos区域。

37.根据本发明实施例,接着,在基底100上形成一介电层110,例如,氧化硅层,但不限于此。接着,在介电层110中形成一沟槽t。根据本发明实施例,基底100可以包含一鳍状结构f1,位于沟槽t内的第一元件区域301中,以及一鳍状结构f2,位于沟槽t内的第二元件区域302中。

38.根据本发明实施例,接着,依序以例如化学气相沉积制作工艺沉积一高介电常数介电层210和一金属氮化物阻障层220,覆盖第一元件区域301和第二元件区域302。高介电常数介电层210和金属氮化物阻障层220顺形地覆盖沟槽t的内表面和介电层110的顶面。高介电常数介电层210例如是氧化铪,金属氮化物阻障层220例如是氮化钽,但不限于此。然后,在金属氮化物阻障层220上沉积一钛层230。

39.如图2所示,接着在基底100上形成一底部抗反射层250,然后在底部抗反射层250上形成一光致抗蚀剂图案260。光致抗蚀剂图案260遮盖住第一元件区域301。

40.如图3所示,接着,去除未被光致抗蚀剂图案260遮盖住的底部抗反射层250,显露出第二元件区域302中的钛层230。

41.如图4所示,再利用蚀刻制作工艺,例如,湿蚀刻制作工艺,将钛层230从第二元件区域302中选择性地去除,从而显露出第二元件区域302中的金属氮化物阻障层220。根据本发明实施例,上述湿蚀刻制作工艺可以是通过使用稀释的氢氟酸溶液或过氧化氢-硫酸混合液(spm)从第二元件区域302选择性地去除钛层230。

42.由于钛对氮化钽的蚀刻选择比相较于氮化钛对氮化钽的蚀刻选择比要高出一些,因此,此步骤不易损伤到金属氮化物阻障层220。此外,也不容易形成残留物。

43.如图5所示,接着,去除光致抗蚀剂图案260和底部抗反射层250,显露出第一元件区域301中的钛层230。随后,可以进行清洁制作工艺。

44.如图6所示,接着,将第一元件区域301中的钛层230转变为氮化钛层230a,作为第一元件区域301中的p功函数金属层。根据本发明实施例,例如,可以利用含氮气等离子体将钛层230转变为氮化钛层230a。

45.如图7所示,接下来,在第一元件区域301和第二元件区域302上沉积一n功函数金属层280。根据本发明实施例,n功函数金属层280可以包括钛铝,但不限于此。接着,在n功函数金属层280上沉积一间隙填充导电层290。间隙填充导电层290可以填满沟槽t。根据本发明实施例,间隙填充导电层290包括铝或钨。

46.以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1