半导体器件及其制作方法与流程

本发明实施例涉及微电子,尤其涉及一种半导体器件及其制作方法。

背景技术:

1、iii族氮化物材料在实现光电器件以及高电子迁移率晶体管器件(high electronmobility transistor,hemt)方面具有独特的优势,其研究也经历了漫长的发展过程。氮化镓(gan)半导体材料具有禁带宽度大、电子饱和漂移速率高、击穿场强高、耐高温等显著优点,与第一代半导体硅和第二代半导体砷化镓相比,更适合于制作高温、高压、高频和大功率的电子器件,具有广阔的应用前景,已成为目前半导体行业研究的热点。

2、在现有技术中,为了提升gan的晶体质量,采用的技术方案一是使用成核层技术,二是选用晶格常数与gan较接近的材料作为衬底。在技术方案二中,晶格常数与gan接近的材料虽然能有效提升gan的晶体质量,但是由于生长工艺和抛光工艺的影响,衬底表面会掺杂进一些杂质。并且,这些杂质在gan会有向外延层扩散的趋势,导致gan中的杂质变多,影响了制作出的半导体器件的性能。例如,对于sic衬底,掺入sic衬底表面的杂质包括氮和氧。而在gan外延生长过程中,sic衬底中的氧杂质会扩散至gan外延层,而氧杂质在gan中以施主的形式存在,因此氧杂质的增加导致gan外延层的漏电增加,使得半导体器件的性能大幅降低。

技术实现思路

1、本发明实施例提供一种半导体器件及其制作方法,以抑制衬底中的杂质向外延层扩散,提升半导体器件的性能。

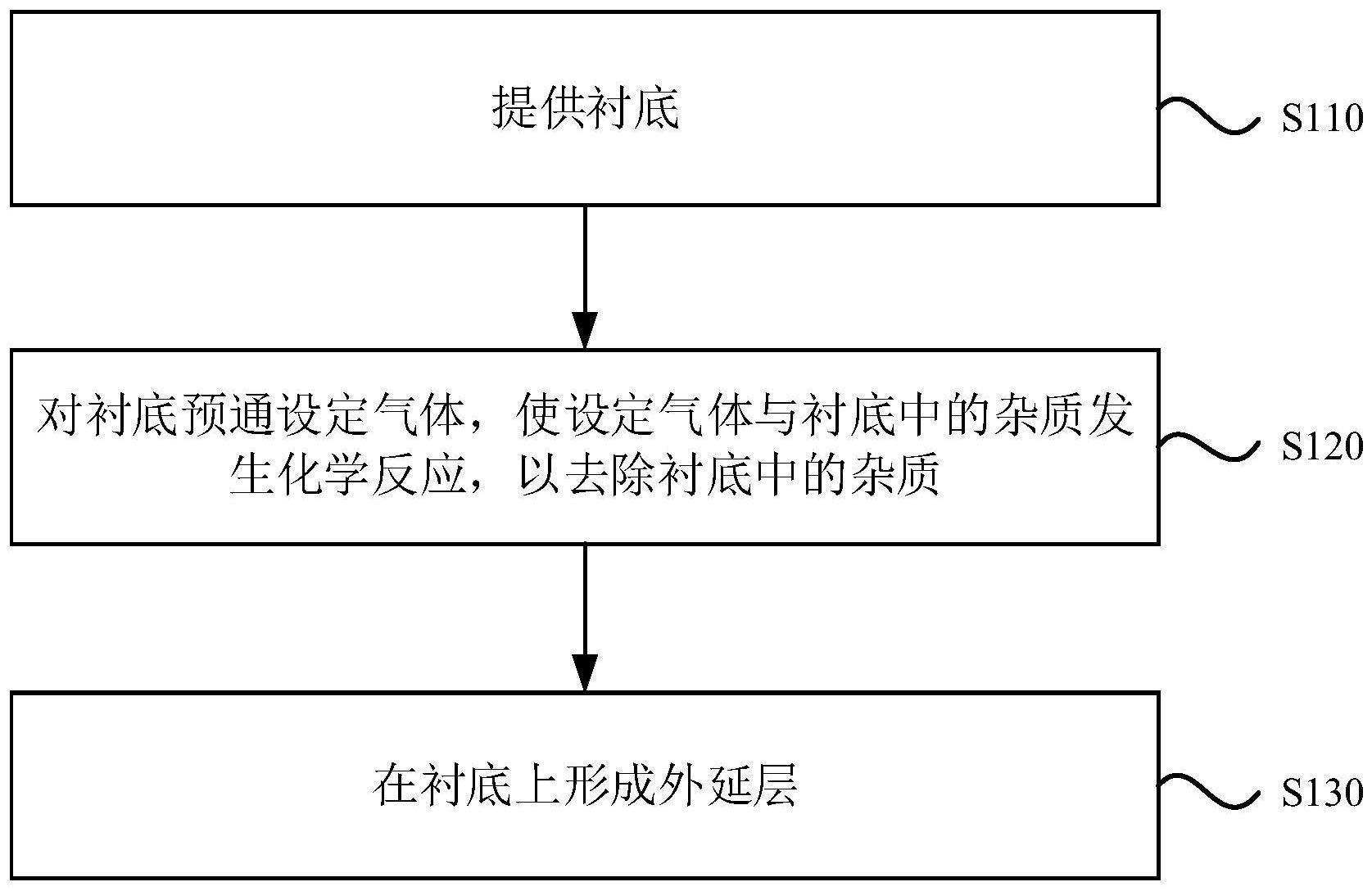

2、第一方面,本发明实施例提供了一种半导体器件的制作方法,包括:

3、提供衬底;

4、对所述衬底预通设定气体,使所述设定气体与所述衬底中的杂质发生化学反应,以去除所述衬底中的杂质;

5、在所述衬底上形成外延层。

6、可选地,所述衬底中的杂质包括氧杂质;

7、所述设定气体为在第一预设温度下与所述氧杂质发生化学反应,且在第二预设温度下进行分解的气体。

8、可选地,所述设定气体包括镓或铝中的至少一种。

9、可选地,对所述衬底预通设定气体的方式为循环预通。

10、可选地,所述循环预通中的一个循环包括:

11、提供第一预设温度条件,并向所述衬底表面通入所述设定气体,以使所述设定气体与所述衬底中的杂质发生化学反应,形成中间化合物;

12、提供第二预设温度条件和排气通道,以使所述中间化合物分解并随尾气排出。

13、可选地,所述外延层包括成核层,所述成核层与所述衬底接触;

14、所述循环预通处理的循环次数与所述成核层的厚度呈负相关。

15、可选地,所述成核层的厚度为x,循环次数为y,预设厚度为z;

16、若x>z,则y为恒定值;

17、若x≤z,则y为x的减函数。

18、可选地,所述恒定值为1或2。

19、可选地,x和y的函数关系表示为:y=round(-0.1*x+q),其中,round表示四舍五入后取整,q为整数。

20、可选地,z的取值范围为:30nm~40nm。

21、可选地,对所述衬底预通设定气体的通气方式包括:恒定流量方式、多脉冲方式和流量渐变方式中的至少一种。

22、可选地,所述流量渐变方式包括:流量递增、流量递减、流量先增后减和流量先减后增中的至少一种。

23、可选地,所述流量渐变方式包括:流量无级渐变和流量阶梯渐变中的至少一种。

24、第二方面,本发明实施例还提供了一种半导体器件,采用如本发明任意实施例所述的制作方法进行制作。

25、本发明实施例提供了一种新的半导体器件的制作方法,包括:提供衬底;对所述衬底预通设定气体,使所述设定气体与所述衬底中的杂质发生化学反应,以去除所述衬底中的杂质;在所述衬底上形成外延层。即本发明实施例通过在生长外延层之前,对衬底预通设定气体,通过设定气体与衬底中的杂质发生化学反应来减少衬底中的杂质含量,有利于抑制衬底中的杂质向外延层扩散,提升了半导体器件的性能。

技术特征:

1.一种半导体器件的制作方法,其特征在于,包括:

2.根据权利要求1所述的半导体器件的制作方法,其特征在于,所述衬底中的杂质包括氧杂质;

3.根据权利要求2所述的半导体器件的制作方法,其特征在于,所述设定气体包括镓或铝中的至少一种。

4.根据权利要求1所述的半导体器件的制作方法,其特征在于,对所述衬底预通设定气体的方式为循环预通。

5.根据权利要求4所述的半导体器件的制作方法,其特征在于,所述循环预通中的一个循环包括:

6.根据权利要求4所述的半导体器件的制作方法,其特征在于,所述外延层包括成核层,所述成核层与所述衬底接触;

7.根据权利要求6所述的半导体器件的制作方法,其特征在于,所述成核层的厚度为x,循环次数为y,预设厚度为z;

8.根据权利要求7所述的半导体器件的制作方法,其特征在于,x和y的函数关系表示为:y=round(-0.1*x+q),其中,round表示四舍五入后取整,q为整数。

9.根据权利要求7所述的半导体器件的制作方法,其特征在于,z的取值范围为:30nm~40nm。

10.一种半导体器件,其特征在于,采用如权利要求1-9任一项所述的制作方法进行制作。

技术总结

本发明实施例公开了一种半导体器件及其制作方法。半导体器件的制作方法包括:提供衬底;对所述衬底预通设定气体,使所述设定气体与所述衬底中的杂质发生化学反应,以去除所述衬底中的杂质;在所述衬底上形成外延层。与现有技术相比,本发明实施例有利于抑制衬底中的杂质向外延层扩散,提升了半导体器件的性能。

技术研发人员:李仕强,张晖

受保护的技术使用者:苏州能讯高能半导体有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!