晶圆基板电源完整性的优化方法、晶圆基板及晶上系统与流程

本技术涉及晶圆,尤其涉及一种晶圆基板电源完整性的优化方法、晶圆基板及晶上系统。

背景技术:

1、现阶段集成电路领域迅速发展,芯片制造工艺逐步逼近物理极限,摩尔定律逐步放缓,因此研究人员开始探索创新性的路径,采用晶上系统是芯片设计的主流趋势之一。cerebras公司采用晶上系统技术路线开发了晶圆级人工智能训练芯片wafer scaleengine(wse),tesla公司也采用晶上系统技术路线研制了ai(artificial intelligence,人工智能)训练芯片dojo。晶上系统技术可以采用更短的引线、在更低的功耗下实现更高的性能和带宽。随着电子器件功能的日益复杂和性能的不断提高,晶圆基板上集成芯片的密度和所使用器件的频率都不断提高,所面临的高速高密度晶圆基板设计所带来的各种挑战也不断增加。与信号完整性同等重要的,电源完整性也是高速高密度晶圆基板需要重点关注的问题。

2、输出的电源质量受电源纹波和电源噪声的影响。电源纹波由电压调节模块(vrm,voltage regulator module)的性能决定,电源噪声是指在芯片管脚处的电压的波动。其中,电源直流电压降(dc irdrop)和同步开关噪声(ssn,simultaneous switch noise)的影响最为显著。ssn是由芯片工作的瞬态大电流、电源配送网络不连续性等原因在电源平面或地平面上所产生的大量噪声现象。另外,如果芯片的全局irdrop过高,逻辑门就会有功能故障,芯片会彻底失效。当所有总线数据同步翻转时,局部irdrop比较敏感,会降低芯片速度。除了对芯片本身工作状态产生影响外,电源噪声还会对其他部分产生影响。比如电源噪声会影响晶振、pll(phase locked loop,锁相环)、dll(delay locked loop,锁相环)的抖动特性,a/d(analog to digital,模/数)转换电路的转换精度等。irdrop是由于电源分配系统存在一定的电阻值,这一问题无法避免,只能尽量通过改进设计方法减小对电路时序以及信号完整性问题的影响。在传统pcb(printed circuit board,印制电路板)领域,为了保证输出电压的稳定,需要在封装、pcb上使用去耦电容和合理的电源平面与地平面对。从目前电源完整性分析的角度看,业内普遍认为在pcb上可以处理到最高到几百兆赫兹电源完整性问题,更高频率的电源完整性问题需要在芯片和封装设计时解决。晶圆基板irdrop问题主要通过仿真加以分析,静态分析时主要考虑寄生电阻,动态分析时还要考虑寄生电容和寄生电感的影响。

3、不同于传统pcb领域,对于晶圆级芯片来说,由于流片工艺及三维封装整体设计的限制,无法引入去耦电容,且系统频率通常较高,传统的电路模型并不适合。因此,需要对晶圆基板的电源网络进行优化设计,改善信号完整性和电源完整性,以保障整个晶上系统的正常工作。

技术实现思路

1、本技术的目的在于提供一种晶圆基板电源完整性的优化方法、晶圆基板及晶上系统,能够提高电源的完整性。

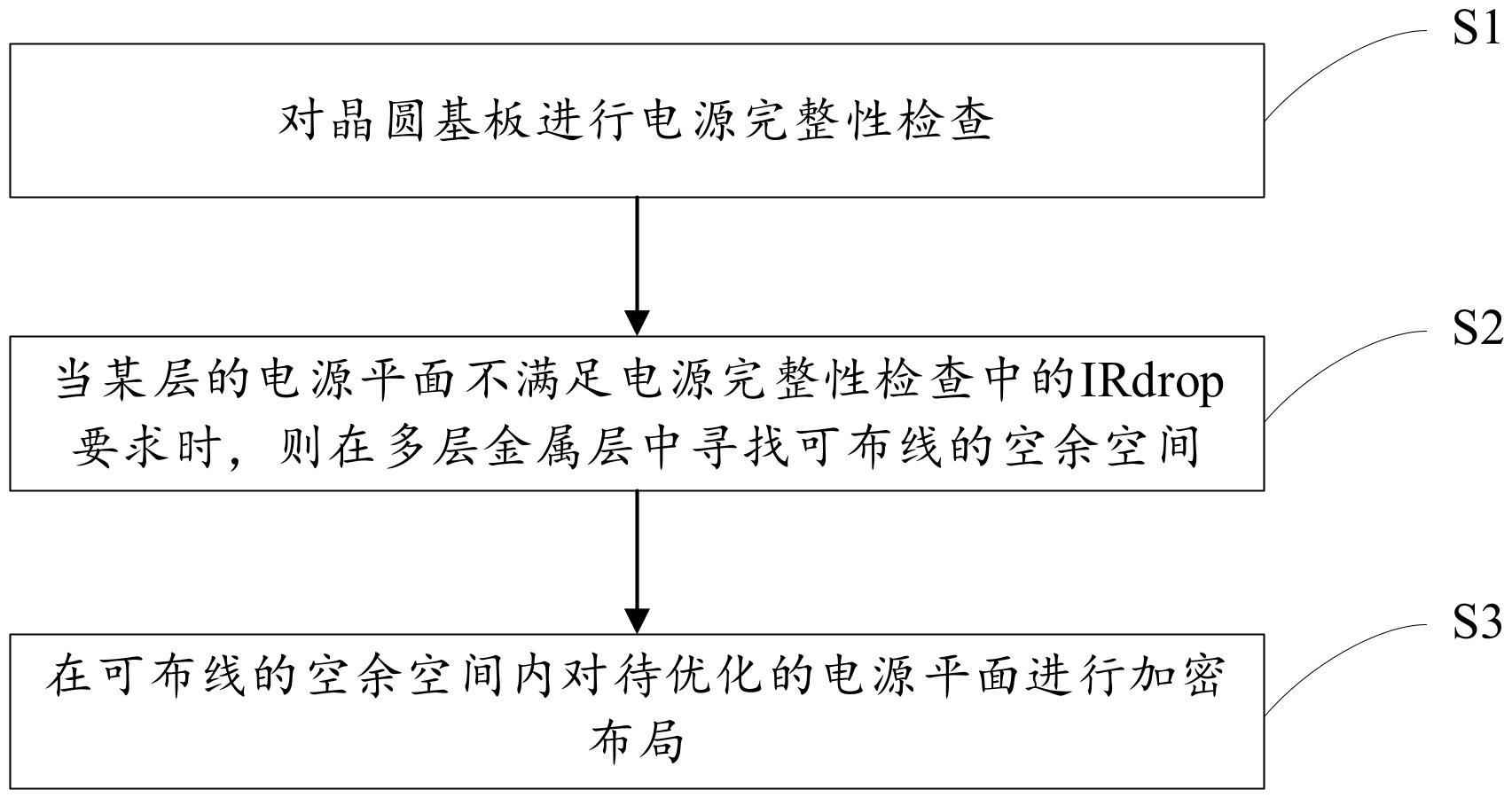

2、本技术的一个方面提供一种晶圆基板电源完整性的优化方法。所述晶圆基板包括多个单元结构,每个所述单元结构包括多层金属层,所述多层金属层包括位于顶层的微凸点阵列、位于底层的微焊盘阵列、以及位于所述顶层与所述底层之间的一层或多层中间层,所述微凸点阵列通过所述一层或多层中间层与所述微焊盘阵列按照预定关系对应连接以形成所述晶圆基板的多个分立的网络,所述多个分立的网络至少包括电源网络、地网络、信号网络及功能配置网络,所述电源网络包括位于所述多层金属层的其中一层或多层上的电源平面。所述优化方法包括:对所述晶圆基板进行电源完整性检查;当某层的电源平面不满足所述电源完整性检查中的电压降要求时,则在所述多层金属层中寻找可布线的空余空间;以及在所述可布线的空余空间内对待优化的所述电源平面进行加密布局。

3、进一步地,在所述多层金属层中寻找可布线的空余空间包括:在与待优化的所述电源平面所在层的不同层中寻找可布线的空余空间,其中,在所述可布线的空余空间内对待优化的所述电源平面进行跨层加密布局。

4、进一步地,在与待优化的所述电源平面所在层的不同层中寻找可布线的空余空间包括:在与待优化的所述电源平面所在层的相邻上层或相邻下层中来寻找可布线的空余空间。

5、进一步地,在所述可布线的空余空间内对待优化的所述电源平面进行加密布局包括:在所述可布线的空余空间内布置额外的密集金属走线;及通过过孔层将待优化的所述电源平面连接到所述密集金属走线。

6、进一步地,所述密集金属走线包括网格状金属走线。

7、进一步地,在所述多层金属层中的相邻金属层之间通过过孔层连接。

8、进一步地,所述过孔层包括独立的过孔或过孔阵列。

9、进一步地,在所述多层金属层中,所述中间层通过硅通孔层连接到底层的所述微焊盘阵列。

10、进一步地,所述电源网络包括多电压域电源网络。

11、进一步地,所述多层金属层中至少包括信号层和接地层,在所述信号层的相邻上层和相邻下层中的至少一层包括所述接地层。

12、本技术的另一个方面提供一种晶圆基板。所述晶圆基板包括多个单元结构,每个所述单元结构包括多层金属层,所述多层金属层包括位于顶层的微凸点阵列、位于底层的微焊盘阵列、以及位于所述顶层与所述底层之间的一层或多层中间层,所述微凸点阵列通过所述一层或多层中间层与所述微焊盘阵列按照预定关系对应连接以形成所述晶圆基板的多个分立的网络,所述多个分立的网络至少包括各电压域电源网络、地网络、信号网络及功能配置网络,所述各电压域电源网络中的至少一个电压域电源网络包括位于一金属层上的电源平面,所述电源平面具有被其他网络隔开的至少两块区域,所述至少一个电压域电源网络还包括布置在与所述电源平面所在层的不同层上的密集金属走线,所述密集金属走线通过过孔层将隔开的所述至少两块区域连接成整体。

13、进一步地,所述密集金属走线位于所述电源平面所在层的相邻上层或相邻下层。

14、进一步地,所述密集金属走线包括网格状金属走线。

15、进一步地,在所述多层金属层中的相邻金属层之间通过过孔层连接。

16、进一步地,所述过孔层包括独立的过孔或过孔阵列。

17、进一步地,在所述多层金属层中,所述中间层通过硅通孔层连接到底层的所述微焊盘阵列。

18、进一步地,所述多层金属层中至少包括信号层和接地层,在所述信号层的相邻上层和相邻下层中的至少一层包括所述接地层。

19、本技术的又一个方面提供一种晶上系统。所述晶上系统包括芯粒、如上所述的晶圆基板、以及驱动电路板,所述芯粒连接到所述晶圆基板顶层的所述微凸点阵列,所述驱动电路板连接所述晶圆基板底层的所述微焊盘阵列。

20、进一步地,所述芯粒包括同质同构芯粒,所述同质同构芯粒与所述微凸点阵列直接相连接。

21、进一步地,所述芯粒包括异质异构芯粒,所述晶圆基板还包括转接板,所述异质异构芯粒通过所述转接板与所述微凸点阵列相连接。

22、本技术一个或多个实施例的晶圆基板电源完整性的优化方法、晶圆基板及晶上系统通过优化电源网络布局结构,能够很好地改善电源完整性,从而具有良好的电源表现。

- 还没有人留言评论。精彩留言会获得点赞!