与CMOS兼容的短波长光电检测器的制作方法

本发明大体上涉及光电检测器,且更具体地说,涉及用于通信系统的光电检测器。

背景技术:

1、随着半导体集成电路变得更加复杂并以更高的速度运行,人们越来越希望在ic的不同部分之间,甚至在数个芯片(或小芯片)之间实现有效的信息流。这可以是简单的时钟分布,也可以是处理器和存储器之间更复杂的数据传送,或者是不同逻辑块交换数据。

2、ic内或ic之间几乎总是通过在ic上方光刻形成的多个金属层(重布层(rdl)和后段生产线(beol)层、封装中的布线、插入ic和封装之间的插入件或桥(通常由硅或有机层合物制成)的使用、附接有多个封装ic的印刷电路板的使用,或电缆在一机箱内或不同机箱中的电路板之间的使用来电气地传送信号。然而,电连接可能会受到信号完整性问题的影响,包含串扰、随频率衰减和阻抗不连续处的反射。改善信号完整性问题可能需要信号再生和均衡,增加ic的电路面积和功率要求。另外,随着每个逻辑转换对与电线相关联的潜在重要电容进行充电或放电,功耗通常随频率而缩放。

3、几十年来,人们对使用光学器件进行时钟分布或芯片内和芯片间数据分布产生了极大的兴趣。例如,同步时钟信号可以以几乎零时延的方式光学地分布到同时共同封装的芯片或芯片集合的许多部分。光信号可以通过自由空间发送,可能使用反射镜或微透镜,或者分布在并入在芯片上或封装中的波导层中。在更复杂的实施方案中,数据总线可以是光学的,用光信号连接芯片上的多个点。

4、芯片内或一组芯片之间的光通信需要适当的光源和接收器。在硅光子学中,使用异质集成激光器、共同封装激光器或外部激光器来产生光,而各种调制器结构如环、马赫-曾德尔(mach-zehnder)波导装置或其它组件将数据施加到cw信号上。检测器可以通过使用吸收锗层在硅中单片制成。通常,1.3um的较长波长用于硅光子学,因为它与其它地方发送或接收数据的光纤兼容。

5、通常,硅和其它材料中的大多数光电检测器采用p-i-n结构,其中轻掺杂的“本征”半导体夹在p掺杂和n掺杂材料之间。无论是单独的二极管内置电压还是额外的反向偏压,都会在本质掺杂的“i”区产生电场。当光子在此区中被吸收并产生电子空穴对时,电场将两个载流子分离并产生光电流。

6、通常,p-i-n结构是“竖直”的(例如,正交于ic的顶表面),例如存在顶部p型区,其下方具有本征区,顶部p型区和本征区全都在n型材料的顶部。光子必须通过顶部p型区才能被本征区吸收。这在较长波长下不是很大的问题,因为这些波长在si中的吸收长度相对较长,因此与光的吸收长度相比,顶部p型区可以变得相当薄。但在si中吸收长度更短的较短波长下,很难使顶部p型区薄到足以完全透明。在顶部p型区中吸收的所有光通常都不会产生光电流,因为没有电场来分离载流子。出现在顶部p掺杂区中的任何光生载流子通常在同一区中重新组合并且不被检测到。

7、此外,竖直光电二极管在速度和效率之间存在权衡。如果与光子波长的吸收长度相比,中间本征区太薄,那么吸收的光不多。如果制造得太厚,以至于所有的光都被吸收,那么区可能太宽,无法快速响应;任何光生载流子通常都应该被扫出本征区,甚至在饱和载流子速度下,通过宽的本征区会导致时间延迟和速度降低。

8、通常需要将光电二极管与cmos电子器件集成。然而,竖直结构通常与cmos工艺不兼容,几乎所有cmos工艺都是极薄层上的横向表面工艺。

9、典型的cmos工艺遵循以下步骤。使用具有低掺杂水平的相对绝缘的晶片,并且为pmos和nmos结构注入n阱和p阱。生长薄氧化物作为栅极氧化物。然后沉积多晶硅层并将其图案化以充当栅极。光致抗蚀剂的第二掩模阻挡p阱,同时使用p+注入物在n阱上的nmos结构上形成源极和漏极。然后移除此掩模,形成另一光致抗蚀剂掩模以保护n阱,随后使用n+注入物在p阱中形成的nmos结构上形成源极和漏极。然后移除抗蚀剂,形成硅化接触,并在具有不同互连金属层的结构中制造psg玻璃氧化物的其它激光器。

技术实现思路

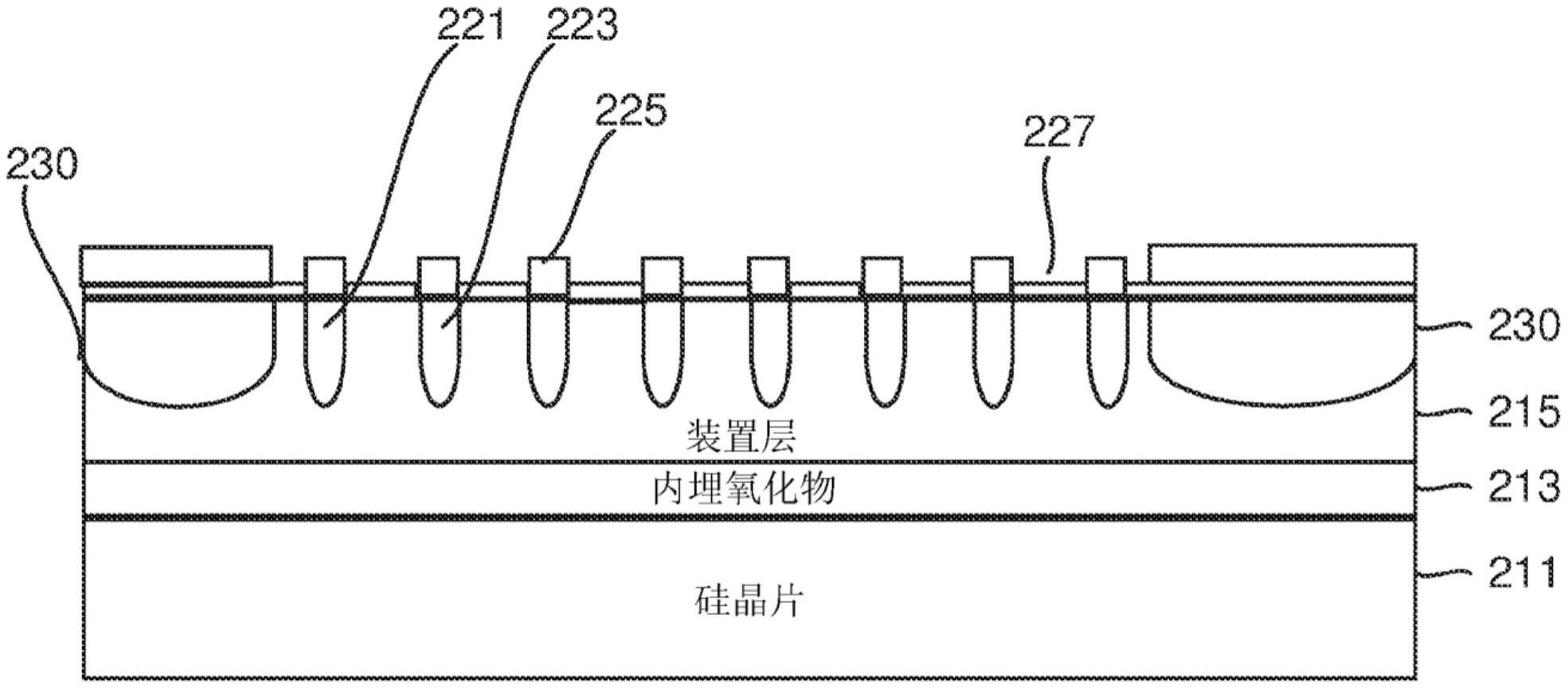

1、在一些实施例中,通过完全cmos兼容工艺制造用于短波长应用的光电检测器。在一些实施例中,所述光电检测器不包含锗或sige。在一些实施例中,所述光电检测器用于波长比1300nm短得多的光。在一些此类实施例中,所述光电检测器用于可见光谱中的蓝色光。在一些实施例中,所述光电检测器用于波长在400nm-450nm范围中的光,所述光可通过氧化物、氮化物或介电波导或光纤传输,并且可以在不使用锗的情况下容易地在硅中检测或吸收。在一些实施例中,作为形成所述光电检测器的nmos和pmos晶体管的源极和漏极区的过程的部分,形成所述光电检测器的n+和p+区。在一些实施例中,所述光电检测器的所述n+和p+区具有所述nmos和pmos晶体管的所述源极和漏极区的注入扩散深度。在一些实施例中,在所述光电检测器的所述n+和p+区的扩散深度下方设置氧化物层。

2、一些实施例提供一种包含与cmos兼容的光电检测器的装置,包括:装置层,其包含由横向p-i-n光电检测器的叉指形p指状物和n指状物构成的光电检测器区,所述p指状物连接到p触点,所述n指状物连接到n触点,所述n指状物掺杂有n型掺杂剂,所述p指状物掺杂有p型掺杂剂;以及在所述装置层下方的内埋氧化物层、在所述装置层下方的内埋掺杂层或在所述光电检测器区的至少一个边缘处的p型或n型掺杂剂注入物中的至少一个。在一些实施例中,在所述装置层下方的所述内埋氧化物层、在所述装置层下方的所述内埋掺杂层或在所述光电检测器区的至少一个边缘处的所述p型或n型掺杂剂注入物中的所述至少一个包括在所述装置层下方的所述内埋氧化物层。在一些实施例中。在一些实施例中,所述内埋氧化物层在工作波长下是反射的。在一些实施例中,所述工作波长约为450nm。在一些实施例中,所述装置层的厚度在所述工作波长下光的吸收长度的3倍到5倍之间。在一些实施例中,所述p指状物和所述n指状物的掺杂区至少延伸到所述装置层的所述厚度的一半。在一些实施例中,在所述装置层下方的内埋氧化物层或在所述光电检测器区的至少一个边缘处的p型注入物或n型注入物中的所述至少一个进一步包括在所述光电检测器区的至少一个边缘处的所述p型注入物或n型注入物。在一些实施例中,在所述光电检测器区的至少一个边缘处的所述p型注入物或n型注入物包括至少在所述光电检测器区的相对边缘处的p型注入物或n型注入物。一些实施例进一步包括在所述装置层中的至少一个pmos晶体管和至少一个nmos晶体管。在一些实施例中,在所述装置层下方的所述内埋氧化物层、在所述装置层下方的所述内埋掺杂层或在所述光电检测器区的至少一个边缘处的所述p型注入物或n型注入物中的所述至少一个包括在所述装置层下方的所述内埋掺杂层。在一些实施例中,所述内埋掺杂层包括n型掺杂层。在一些实施例中,所述内埋掺杂层包括p型掺杂层。一些实施例进一步包括在所述装置层中的跨阻抗放大器电路系统。一些实施例进一步包括定位成向所述光电检测器区提供光的波导。

3、一些实施例提供一种包含与cmos兼容的光电检测器的装置,其包括:装置层,其包含由横向p-i-n光电检测器的叉指形p指状物和n指状物构成的光电检测器区,所述p指状物连接到p触点,所述n指状物连接到n触点,所述n指状物掺杂有n型掺杂剂,所述p指状物掺杂有p型掺杂剂;以及用于所述光电检测器区的光电检测器隔离结构。在一些实施例中,所述光电检测器隔离结构包括在所述光电检测器区之下位于所述装置层下方的内埋氧化物层。在一些实施例中,所述光电检测器隔离结构包括在所述光电检测器区之下位于所述装置层下方的内埋掺杂层。在一些实施例中,所述光电检测器隔离结构包括在所述光电检测器区的相对边缘处的掺杂注入物。在一些实施例中,所述光电检测器隔离结构包括在所述光电检测器区之下位于所述装置层下方的内埋氧化物层和在所述光电检测器区的相对边缘处的掺杂注入物。

4、在检阅本公开后会更充分理解本发明的这些和其它方面。

- 还没有人留言评论。精彩留言会获得点赞!