采用顶侧接触件和背侧接触件用于FET的功率信号和逻辑信号的顶侧布线和背侧布线的场效应晶体管(FET)电路以及相关的互补金属氧化物半导体(CMOS)电路的制作方法

本公开的领域涉及采用p型fet(pfet)和n型fet(nfet)来形成逻辑电路的场效应晶体管(fet)和互补金属氧化物半导体(cmos)集成电路。

背景技术:

1、晶体管是现代电子设备中必不可少的部件。在许多现代电子设备的集成电路(ic)中采用了大量的晶体管。例如,诸如中央处理单元(cpu)、数字信号处理器(dsp)和存储器系统的部件均采用大量晶体管用于逻辑电路和存储器设备。

2、一种类型的晶体管是场效应晶体管(fet)。fet使用电场来控制源极和漏极之间的电流流动。通过向fet的栅极施加电压来控制电流的流动,这又改变了源极和漏极之间的导电性。不同类型的fet包括平面fet、鳍式fet(finfet)和全环绕栅极(gaa)fet。在采用fet的集成电路(ic)中,ic包括源极金属接触件、漏极金属接触件和栅极金属接触件,该源极金属接触件、漏极金属接触件和栅极金属接触件形成为相应与fet的源极、漏极和栅极接触以向fet提供信号布线(routing)。金属接触件然后连接到ic的互连层中的金属线,该互连层在包括fet的ic的半导体或有源层上方,用于通过源极金属接触件、漏极金属接触件和栅极金属接触件将信号布线到fet的源极、漏极和栅极。例如,如果采用fet的电路需要将功率信号耦合到fet的源极,则源极接触件被耦合到被设计成携载功率的金属线。作为另一个示例,如果采用fet的电路需要将逻辑信号耦合到fet的漏极,则漏极接触耦合到被设计成携载逻辑信号的金属线。

3、随着采用fet的电路的节点尺寸在ic中减小以节省区域和/或允许在给定的区域或芯片尺寸中制造更多的fet,相邻fet之间的栅极间距也可以减小。这可以减小ic中相邻fet的源极和漏极之间的距离,增加设置在fet上方用于提供信号布线的互连层中的布线拥塞。增加的信号布线拥塞会导致互连层中的金属线更靠近地设置在一起,从而增加布线线的寄生电容并且因此增加fet的电容。fet上电容的增加会降低fet的性能。

技术实现思路

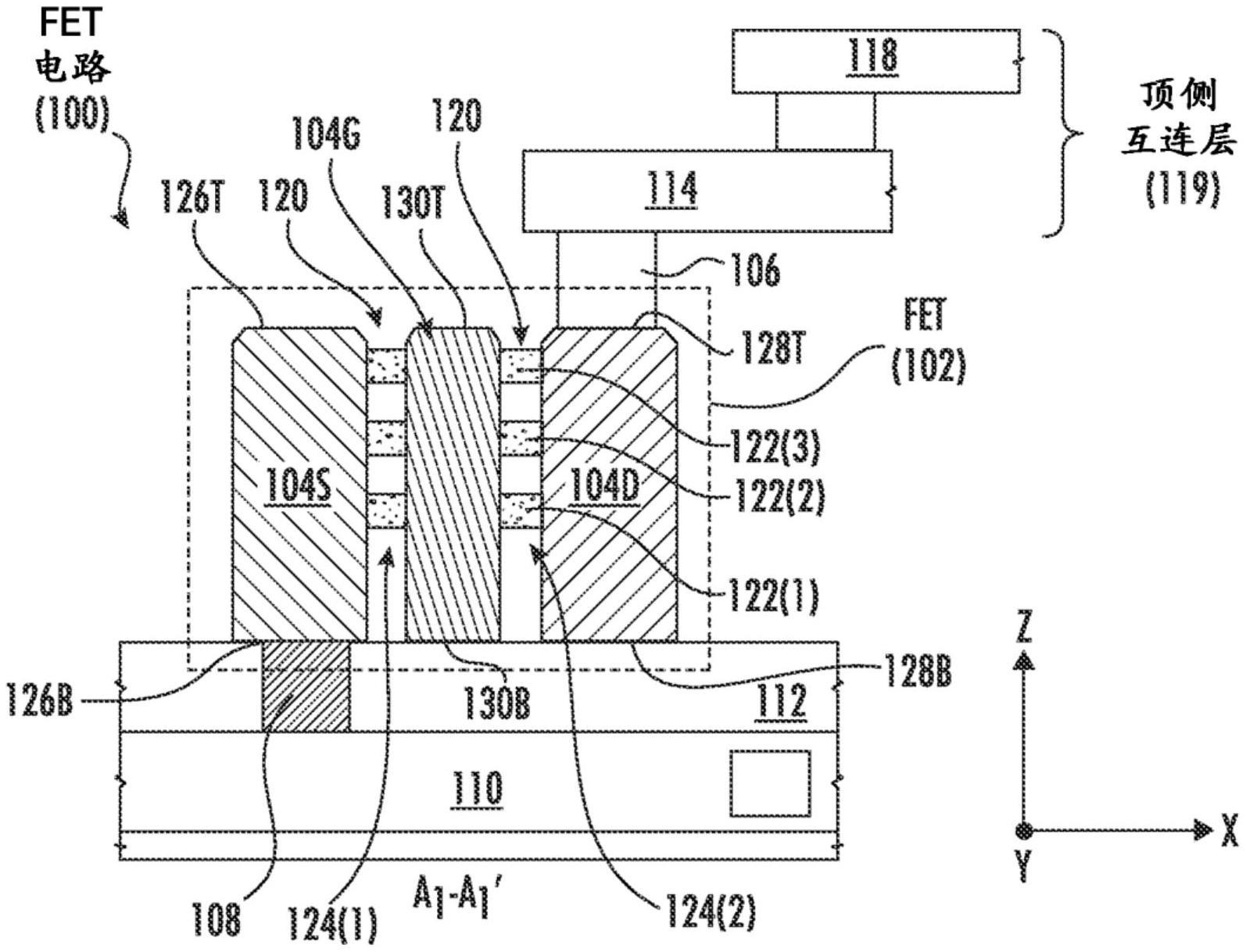

1、本文公开的各方面包括场效应晶体管(fet)电路,该场效应晶体管电路采用顶侧接触件和背侧接触件来进行fet的功率信号和逻辑信号的顶侧布线和背侧布线。还公开了采用fet的相关互补金属氧化物半导体(cmos)电路,该fet采用顶侧接触件和背侧接触件用于fet的功率信号和逻辑信号的顶侧布线和背侧布线。在此方面,在本文公开的某些示例性方面,提供了一种fet电路,其包括fet,该fet包括导电沟道、源极、漏极和栅极。导电沟道设置在衬底上方。源极被设置在导电沟道的第一端部。漏极被设置在导电沟道的第二端部。栅极被设置在导电沟道的至少一部分上方并且在导电沟道的第一端部和第二端部之间。fet电路还包括至少一个顶侧金属接触件,该至少一个顶侧金属接触件与fet的源极、漏极和栅极中的至少一者的顶表面接触。fet电路还包括至少一个背侧金属接触件,该至少一个背侧金属接触件与fet的源极、漏极和栅极中的至少一者的底表面接触。fet电路还包括顶侧金属线和背侧金属线,该顶侧金属线和背侧金属线相应电耦合到顶侧金属接触件和背侧金属接触件,以向fet提供功率布线和信号布线。顶侧金属线和背侧金属线中的至少一者电耦合到被配置为携载功率信号的功率轨,并且其他顶侧金属线和背侧金属线中的至少一者电耦合到被配置为携载逻辑信号的信号传递金属线。

2、以此类方式,fet电路上的背侧布线为信号布线和/或功率布线提供了另外的区域,作为示例,这可以有利地被采用以抵消布线区域的任何减小,诸如由于fet尺寸的减小和/或包括fet电路的电路复杂度的增加。增加的信号布线拥塞会导致互连层中的金属线更靠近地设置在一起,从而增加布线线的寄生电容并且因此增加fet的电容。fet上电容的增加会降低fet的性能。

3、在另一个示例性方面,提供了一种cmos电路,包括:衬底,包括顶表面;正(p)型扩散区,设置在衬底中;以及负(n)型扩散区,设置在衬底中。cmos电路包括邻近p型扩散区设置的第一功率轨和邻近n型扩散区设置的第二功率轨。至少一个p型fet(pfet)形成在n型扩散区中,并且至少一个n型fet(nfet)形成在p型扩散区中。cmos电路中的pfet和nfet各自包括:导电沟道,设置在衬底上方;源极,设置在其导电沟道的第一端部;漏极,设置在其导电沟道的第二端部;以及栅极,邻近其导电沟道设置。cmos电路中的至少一个pfet和至少一个nfet各自包括:源极背侧金属接触件,设置在衬底的顶表面下方并且与其源极底表面电耦合;以及漏极背侧金属接触件,设置在衬底的顶表面下方并且与其漏极底表面电耦合。至少一个pfet和至少一个nfet的源极背侧金属接触件和漏极背侧金属接触件中的一者电耦合到背侧功率金属线,该背侧功率金属线在平行于第一功率轨和第二功率轨中的功率轨的纵向轴线的纵向轴线上延伸并且耦合到功率轨。至少一个pfet和至少一个nfet的源极背侧金属接触件和漏极背侧金属接触件中的另一者电耦合到被配置为携载逻辑信号的背侧信号传递金属线。

4、在cmos电路的另一个示例性方面,背侧信号传递金属线沿着平行于背侧功率金属线的纵向轴线的纵向轴线延伸。背侧信号传递金属线和背侧功率金属线被设置在第一功率轨和第二功率轨之间。

5、在此方面,在一个示例性方面,提供了一种场效应晶体管(fet)电路。该fet电路包括:信号传递金属线,被配置为携载逻辑信号;功率轨,被配置为携载来自电源的功率信号;以及fet。fet电路还包括:导电沟道,设置在衬底上方;以及源极,设置在导电沟道的第一端部中,其中源极包括源极顶表面和源极底表面。fet电路还包括漏极,该漏极设置在与第一端部相对的导电沟道的第二端部中,其中漏极包括漏极顶表面和漏极底表面。fet电路还包括栅极,该栅极设置在导电沟道的至少一部分上方并且在导电沟道的第一端部和第二端部之间,其中栅极包括栅极顶表面和栅极底表面。fet电路还包括顶侧金属接触件,该顶侧金属接触件与源极顶表面、漏极顶表面和栅极顶表面中的一者接触。fet还包括:背侧金属接触件,与源极底表面、漏极底表面和栅极底表面中的一者接触;以及顶侧金属线,其设置在栅极上方。顶侧金属线电耦合到信号传递金属线和功率轨中的一者以及顶侧金属接触件。fet电路还包括背侧金属线,该背侧金属线设置在导电沟道下方,其中背侧金属线电耦合到功率轨和信号传递金属线中未耦合到顶侧金属线的一者以及背侧金属接触件。

6、在另一个示例性方面,fet的背侧金属接触件包括竖直互连通路(过孔),该竖直互连通路(过孔)与源极底表面、漏极底表面和栅极底表面中的一者接触。

7、在另一个示例性方面,fet包括第二背侧金属接触件,该第二背侧金属接触件与源极底表面、漏极底表面和栅极底表面中的不与背侧金属接触件接触的一者接触。第二背侧金属线设置在导电沟道下方,第二背侧金属线电耦合到第二背侧金属接触件和信号传递金属线。在该进一步示例性方面,背侧金属接触件与源极底表面接触,并且第二背侧金属接触件与漏极底表面接触。在该进一步方面的另一个示例性方面,背侧金属接触件与漏极底表面接触,并且第二背侧金属接触件与源极底表面接触。在该进一步方面的另一个示例性方面,导电沟道沿着导电沟道的第一端部和第二端部之间的第一纵向轴线延伸,背侧金属线沿着平行于第一纵向轴线的第二纵向轴线延伸,并且第二背侧金属线沿着平行于第二纵向轴线的第三纵向轴线延伸。

8、在另一个示例性方面,fet还包括:衬底,包括衬底顶表面和衬底底表面;以及掩埋氧化物(box)层,设置在衬底顶表面上,其中背侧金属线设置在衬底底表面下方,源极设置成与box层接触,并且漏极设置成与box层接触。在该进一步方面,在示例性方面,源极延伸穿过box层,使得源极底表面与衬底顶表面接触,和/或漏极延伸穿过box层,使得漏极底表面与衬底顶表面接触。在该进一步方面的另一个示例性方面,背侧金属接触件包括过孔,该过孔包括过孔顶表面,该过孔顶表面与源极底表面、漏极底表面和栅极底表面中的一者接触。

9、在另一个示例性方面,背侧金属接触件包括过孔,该过孔包括过孔顶表面,该过孔顶表面与源极底表面、漏极底表面和栅极底表面中的一者接触。在该进一步方面,在另一个示例性方面,过孔与衬底接触。

10、在另一个示例性方面,背侧金属接触件包括背侧金属接触件顶表面,该背侧金属接触件顶表面与源极底表面、漏极底表面和栅极底表面中的一者接触。背侧金属接触件还包括背侧金属接触件底表面和过孔,该过孔包括过孔顶表面,该过孔顶表面与背侧金属接触件底表面接触。在该进一步方面的另一个示例性方面,背侧金属接触件与掩埋氧化物(box)层接触,并且该过孔与衬底接触。在该进一步方面的另一个示例性方面,与背侧金属接触件的背侧金属接触件顶表面接触的源极底表面、漏极底表面和栅极底表面中的一者与box层的box层顶表面接触。

11、在另一个示例性方面,提供了一种制造fet电路的方法,该方法包括形成fet,包括:在衬底上方形成导电沟道;形成源极,该源极设置在导电沟道的第一端部中,该源极包括源极顶表面和源极底表面;形成漏极,该漏极设置在导电沟道的与第一端部相对的第二端部中,该漏极包括漏极顶表面和漏极底表面;以及形成栅极,该栅极设置在导电沟道的至少一部分上方并且在导电沟道的第一端部和第二端部之间,该栅极包括栅极顶表面和栅极底表面。该方法还包括:形成顶侧金属接触件,该顶侧金属接触件与源极顶表面、漏极顶表面和栅极顶表面中的一者接触;形成背侧金属接触件,该背侧金属接触件与源极底表面、漏极底表面和栅极底表面中的一者接触;以及形成顶侧金属线,该顶侧金属线设置在栅极上方并且与顶侧金属接触件电接触。该方法还包括形成背侧金属线,该背侧金属线设置在导电沟道下方并且与背侧金属接触件电接触。该方法还包括形成信号传递金属线,该信号传递金属线被配置为携载与顶侧金属线和背侧金属线中的一者接触的逻辑信号。该方法还包括形成功率轨,该功率轨被配置为携载来自电源的功率信号,该电源与背侧金属线和顶侧金属线中不与信号传递金属线接触的一者接触。

12、在此方法的另一个示例性方面,形成背侧金属接触件包括形成过孔,该过孔包括过孔顶表面,该过孔顶表面与源极底表面、漏极底表面和栅极底表面中的一者接触。

13、该方法的另一个示例性方面还包括形成衬底,该衬底包括衬底顶表面和衬底底表面,以及在衬底顶表面上形成掩埋氧化物(box)层,其中形成背侧金属线还包括在衬底底表面下方形成背侧金属线,其中形成源极还包括形成与box层接触的源极,并且其中形成漏极还包括形成与box层接触的漏极。在该进一步方面,在另一个示例性方面,该方法包括通过形成用以延伸穿过box层的源极来形成源极,使得源极底表面与衬底顶表面接触。在该进一步方面,在另一个示例性方面,形成漏极还包括形成用以延伸穿过box层的漏极,使得漏极底表面与衬底顶表面接触。

14、在该方法的另一个示例性方面,形成背侧金属接触件还包括形成背侧金属接触件顶表面,该背侧金属接触件顶表面与源极底表面、漏极底表面和栅极底表面中的一者接触。该方法还包括形成背侧金属接触件底表面和形成过孔,该过孔包括过孔顶表面,该过孔顶表面与背侧金属接触件底表面接触。

15、在另一个示例性方面,提供了一种互补金属氧化物半导体(cmos)电路。cmos电路包括:p型扩散区,设置在衬底中;n型扩散区,设置在衬底中;功率轨,具有设置在第一方向上的第一纵向轴线;信号传递金属线,电耦合到另一个电路;以及p型场效应晶体管(fet)(pfet),形成在n型扩散区中。pfet包括:p型导电沟道;p型源极,设置在p型导电沟道的第一端部中;p型漏极,设置在p型导电沟道的与第一端部相对的第二端部中;以及第一栅极,设置在p型导电沟道的至少一部分上方并且在p型导电沟道的第一端部和第二端部之间。cmos电路还包括形成在p型扩散区中的n型场效应晶体管(nfet)。nfet包括:n型导电沟道;n型源极,设置在n型导电沟道的第一端部中;n型漏极,设置在n型导电沟道的与第一端部相对的第二端部中;以及第二栅极,其设置在n型导电沟道的至少一部分上方并且在n型导电沟道的第一端部和第二端部之间。cmos电路还包括:第一背侧金属接触件,与p型源极、p型漏极和第一栅极中的一者接触;第二背侧金属接触件,与n型源极、n型漏极和第二栅极中的一者接触。cmos电路还包括第一背侧金属线,该第一背侧金属线设置在衬底下方,第一背侧金属线电耦合到第一背侧金属接触件。cmos电路还包括设置在衬底下方的第二背侧金属线。第二背侧金属线电耦合到第二背侧金属接触件。第一背侧金属线耦合到功率轨和信号传递金属线中的一者。第二背侧金属线耦合到信号传递金属线和功率轨中未耦合到第一背侧金属线的一者。

16、在cmos电路的另一个示例性方面,p型源极包括p型源极顶表面和p型源极底表面,p型漏极包括p型漏极顶表面和p型漏极底表面,第一栅极包括第一栅极顶表面和第一栅极底表面,n型源极包括n型源极顶表面和n型源极底表面,n型漏极包括n型漏极顶表面和n型漏极底表面,第二栅极包括第二栅极顶表面和第二栅极底表面,第一背侧金属接触件与p型源极底表面、p型漏极底表面和第一栅极底表面中的一者接触,并且第二背侧金属接触件与n型源极底表面、n型漏极底表面和第二栅极底表面中的一者接触。

17、在cmos电路的另一个示例性方面,第一背侧金属线耦合到功率轨,并且第二背侧金属线耦合到信号传递金属线。

18、在cmos电路的另一个示例性方面,第一背侧金属线耦合到信号传递金属线,并且第二背侧金属线耦合到功率轨。

19、在cmos电路的另一个示例性方面,cmos电路还包括:第二信号传递金属线,电耦合到另一个电路;顶侧金属接触件,与p型源极、p型漏极和第一栅极中的一者接触;以及顶侧金属线,其设置在第一栅极上方,该顶侧金属线电耦合到顶侧金属接触件和第二信号传递金属线。

20、在cmos电路的另一个示例性方面,cmos电路还包括:第二信号传递金属线,电耦合到另一个电路;顶侧金属接触件,与n型源极、n型漏极和第二栅极中的一者接触;以及顶侧金属线,设置在第二栅极上方,该顶侧金属线电耦合到顶侧金属接触件和第二信号传递金属线。

21、在cmos电路的另一个示例性方面,cmos电路还包括:第二功率轨,具有平行于第一纵向轴线的第二纵向轴线;第三背侧金属接触件,与n型源极、n型漏极和第二栅极中的一者接触;以及第三背侧金属线,设置在衬底下方,第三背侧金属线电耦合到第二功率轨。在该进一步方面,另一个示例性方面包括邻近n型扩散区设置功率轨,第二功率轨邻近p型扩散区设置,第一背侧金属接触件与p型源极接触,第二背侧金属接触件与n型漏极接触,第三背侧金属接触件与n型源极接触,第一背侧金属线耦合到功率轨,第二背侧金属线耦合到信号传递金属线,第三背侧金属线耦合到第二功率轨,并且信号传递金属线设置在第一功率轨和第二功率轨之间。在该进一步示例性方面,另一个示例性方面包括第二背侧金属接触件,该第二背侧金属接触件包括:第二背侧金属接触件顶表面,与n型漏极底表面接触;以及第二背侧金属接触件底表面;以及过孔,包括过孔顶表面,该过孔顶表面与第二背侧金属接触件底表面接触。

22、在cmos电路的另一个示例性方面,第一背侧金属接触件包括竖直互连通路(过孔),该竖直互连通路与p型源极、p型漏极和第一栅极中的一者接触,并且第二背侧金属接触件包括第二过孔,该第二过孔与n型源极、n型漏极和第二栅极中的一者接触。

23、在cmos电路的另一个示例性方面,cmos电路还包括:衬底,包括衬底顶表面和衬底底表面;掩埋氧化物(box)层,设置在衬底顶表面上,其中第一背侧金属线设置在衬底底表面下方,第二背侧金属线设置在衬底底表面下方,p型源极设置成与box层接触,p型漏极设置成与box层接触,n型源极设置成与box层接触,并且n型漏极设置成与box层接触。在此进一步示例性方面,在另一个示例性方面,p型源极中的至少一者延伸穿过box层,使得p型源极底表面与衬底顶表面接触,并且p型漏极延伸穿过box层,使得p型漏极底表面与衬底顶表面接触,并且n型源极中的至少一者延伸穿过box层,使得n型源极底表面与衬底顶表面接触,并且n型漏极延伸穿过box层,使得n型漏极底表面与衬底顶表面接触。在该进一步示例性方面,在另一个示例性方面,第一背侧金属接触件包括第一过孔,该第一过孔包括过孔顶表面,该过孔顶表面与p型源极底表面、p型漏极底表面和第一栅极底表面中的一者接触,并且第二背侧金属接触件包括第二过孔,该第二过孔包括第二过孔顶表面,该第二过孔顶表面与n型源极底表面、n型漏极底表面和第二栅极底表面中的一者接触。在该示例性方面的又一个示例性方面,第一过孔与衬底接触,并且第二过孔与衬底接触。

24、在cmos电路的另一个示例性方面,第一背侧金属接触件包括第一背侧金属接触件顶表面,该第一背侧金属接触件顶表面与p型源极底表面、p型漏极底表面和第一栅极底表面中的一者接触。第一背侧金属接触件还包括第一背侧金属接触件底表面和第一过孔,第一过孔包括第一过孔顶表面,该第一过孔顶表面与第一背侧金属接触件底表面接触。第二背侧金属接触件还包括:第二背侧金属接触件顶表面,与n型源极底表面、n型漏极底表面和第二栅极底表面中的一者接触;第二背侧金属接触件底表面;以及第二过孔,包括第二过孔顶表面,该第二过孔顶表面与第二背侧金属接触件底表面接触。在该进一步示例性方面,在另一个示例性方面,第一背侧金属接触件与掩埋氧化物(box)层接触,第一过孔与衬底接触,第二背侧金属接触件与box层接触,并且第二过孔与衬底接触。在该示例性方面的另一个示例性方面,与第一背侧金属接触件的第一背侧金属接触件顶表面接触的p型源极底表面、p型漏极底表面和第一栅极底表面中的一者与box层的box层顶表面接触,并且与第二背侧金属接触件的第二背侧金属接触件顶表面接触的n型源极底表面、n型漏极底表面和第二栅极底表面中的一者与box层的box层顶表面接触。

- 还没有人留言评论。精彩留言会获得点赞!