半导体器件的制作方法

本发明涉及半导体器件。

背景技术:

1、作为用于电功率控制与转换的功率半导体器件,sic沟槽mosfet(metal-oxide-semiconductor field effect transistor)已广为人知,其为了保护栅极绝缘膜免受大电流、大电压影响,通常采用在栅极沟槽的底部设置电场保护层等耐压措施。

2、例如,作为与栅极沟槽底部的电场保护层对应的结构,专利文献1公开了,在元胞区(cell area)a1的第一沟槽21的下方位置设置有p型的第一浮置区域36;专利文献2公开了,作为栅极沟槽底部的电场保护层,在元胞区的栅极沟槽21的底部设置有p浮置区域51。

3、更具体而言,专利文献1公开了一种半导体器件10,其具备划分出元胞区a1和终端区a2半导体衬底12,元胞区a1具有第一沟槽21、收纳在第一沟槽21内的栅电极31以及设置在第一沟槽21的下方位置的p型的第一浮置区域36,终端区a2具有第二沟槽22和设置在第二沟槽22的下方位置的第二浮置区域42,最内周第二沟槽22i的深度d2被设定得比第一沟槽21的深度d1浅,以使第一距离z1(上下方向上的栅电极31的底面31a与第一浮置区域36的上端36a之间的距离)与第二距离z2(上下方向上的最内周第二浮置区域42i的上端42a与主体层(body layer)25之间的距离)相同。

4、另外,专利文献2公开了一种半导体器件,在元胞区形成有栅极沟槽21和p浮置区域51,在终端区形成有终端沟槽62和p浮置区域53,在三个终端沟槽62(终端沟槽621、终端沟槽622、终端沟槽623)之中,终端沟槽621内具有与栅极沟槽21相同的结构,其他终端沟槽内具有由氧化硅等绝缘物填充的结构,p浮置区域51是通过从栅极沟槽21的底面注入杂质而形成的区域,p浮置区域53是通过从终端沟槽62的底面注入杂质而形成的区域。

5、此外,虽不是在栅极沟槽的底部设置电场保护层,但专利文献3公开了一种半导体器件,其包括半导体衬底,该半导体衬底具有设置有沟槽栅极的元件区域、位于元件区域的外侧的终端区域以及位于元件区域与终端区域之间的边界区域,在终端区域和边界区域各自设置有导电类型与半导体衬底不同的第一扩散层、在半导体衬底内具有比第一扩散层的厚度大的深度的沟槽部、以及在沟槽部的底部侧与第一扩散层接触且导电类型与第一扩散层相同的第二扩散层。

6、现有技术文献

7、专利文献

8、专利文献1:日本特开2017-107940号公报

9、专利文献2:日本特开2006-128507号公报

10、专利文献3:日本特开2019-117867号公报

技术实现思路

1、发明要解决的技术问题

2、但是,配置在有源区域的端部的栅极沟槽的电场保护层容易被施加比其他部分大的电场(等电位线的曲率比其他部分大),成为导致雪崩耐压降低的原因。因此,期望开发一种结构用于缓和配置在有源区域的端部的栅极沟槽的电场保护层处的电场。

3、在此,专利文献1、2中虽然公开了在终端区(相当于终端区域)设置浮置区域(专利文献1的第二浮置区域42、专利文献2的p浮置区域53),但如后所述存在这样的问题,即,如果不充分增大浮置区域的深度、厚度,则缓和配置在有源区域的端部的栅极沟槽的电场保护层处的电场的效果可能不充分。另外,专利文献3因为并非以存在有源区域的电场保护层为前提,所以没有公开使有源区域的电场保护层的电场得到缓和的技术。

4、本发明鉴于上述情况,其目的在于提供一种半导体器件,其容易制造,能够缓和设置在有源区域端部的栅极沟槽处的电场保护层上被施加的电场、提高雪崩耐压。

5、解决问题的技术手段

6、用于解决上述问题的本发明的一个方面提供一种半导体器件,包括有源区域和配置在有源区域的外周的终端区域,有源区域具有多个栅极沟槽、设置在栅极沟槽内的沟槽栅电极以及设置在栅极沟槽以外的部分的p主体层,其特征在于,在有源区域的栅极沟槽的底部具有电场保护层,在有源区域与终端区域之间具有电场缓和层,电场缓和层的底面比电场保护层的底面浅,且电场缓和层与p主体层电连接。

7、本发明的更具体的结构记载在要求保护的技术方案中。

8、发明效果

9、根据本发明能够提供一种半导体器件,其容易制造,能够缓和设置在有源区域端部的栅极沟槽处的电场保护层上被施加的电场、提高雪崩耐压。

10、上述以外的问题、特征和效果通过以下实施方式的说明变得明确。

技术特征:

1.一种半导体器件,包括有源区域和配置在所述有源区域的外周的终端区域,所述有源区域具有多个栅极沟槽、设置在所述栅极沟槽内的沟槽栅电极以及设置在所述栅极沟槽以外的部分的p主体层,其特征在于,

2.根据权利要求1所述的半导体器件,其特征在于,

3.根据权利要求2所述的半导体器件,其特征在于,

4.根据权利要求2所述的半导体器件,其特征在于,

5.根据权利要求1所述的半导体器件,其特征在于,

6.根据权利要求1所述的半导体器件,其特征在于,

7.根据权利要求2所述的半导体器件,其特征在于,

8.根据权利要求1所述的半导体器件,其特征在于,

9.根据权利要求1所述的半导体器件,其特征在于,

10.根据权利要求1所述的半导体器件,其特征在于,

11.根据权利要求1所述的半导体器件,其特征在于,

12.根据权利要求1所述的半导体器件,其特征在于,

13.根据权利要求1所述的半导体器件,其特征在于,

14.根据权利要求12所述的半导体器件,其特征在于,

15.根据权利要求1所述的半导体器件,其特征在于,

技术总结

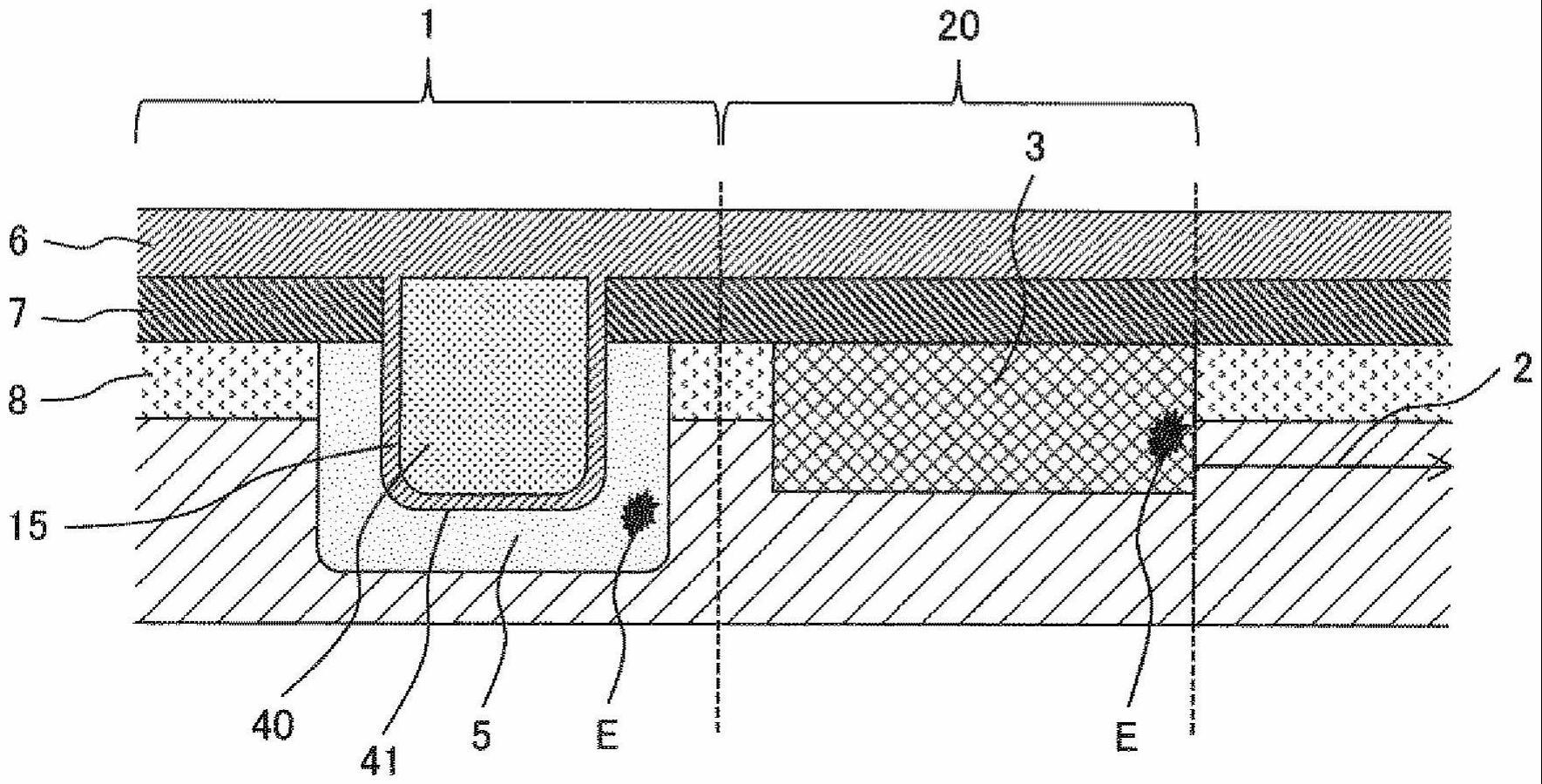

本发明提供一种半导体器件,其容易制造,能够缓和设置在有源区域端部的栅极沟槽处的电场保护层上被施加的电场、提高雪崩耐压。本发明半导体器件(10)包括有源区域(1)和配置在有源区域(1)的外周的终端区域(2),有源区域(1)具有多个栅极沟槽(41)、设置在栅极沟槽(41)内的沟槽栅电极(40)以及设置在栅极沟槽(41)以外的部分的P主体层(8),其特征在于,在有源区域(1)的栅极沟槽(41)的底部具有电场保护层(5),在有源区域(1)与终端区域(2)之间具有电场缓和层(3),电场缓和层(3)的底面比电场保护层(5)的底面浅,且电场缓和层与P主体层(8)电连接。

技术研发人员:木下昂洋,森川贵博,村田龙纪,安井感

受保护的技术使用者:株式会社日立功率半导体

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!