层叠型电感器的制作方法

1.本发明涉及层叠型电感器。

背景技术:

2.目前,已知有一种包括在素体内呈直线状延伸的贯通导体的电感器。在日本特开2020—88289号公报中公开了一种电感器,其包括具有彼此相对的一对端面的素体、遍及端面之间平坦地延伸的贯通导体、及设置于素体的两端面并且与贯通导体连接的一对外部电极。

技术实现要素:

3.上述现有技术所涉及电感器的素体是通过将层叠的多个磁性体层进行烧成而获得的烧成体(烧成素体)。贯通导体是通过将涂布于上述磁性体层上的导电性膏体与上述磁性体层一同进行烧成而获得的。一般来说,烧成时的磁性体层的收缩率与导电性膏体的收缩率不同。因此,在烧成后的素体内会产生因收缩率差引起的内部应力,在素体内可能产生因内部应力引起的裂纹。发明人们认真研究,新发现了一种能够抑制因内部应力引起的裂纹的技术。

4.根据本发明的一个方面,提供一种可抑制裂纹的层叠型电感器。

5.本发明的一个方面所涉及的层叠型电感器,包括:包含被层叠的多个层,并且具有在相对于多个层的层叠方向正交的第1方向上彼此相对的一对端面的烧成素体;设置于烧成素体内,遍及一对端面之间延伸并且在端面上两个端部露出的贯通导体;分别设置于烧成素体的端面,并且分别覆盖露出于端面的贯通导体的两个端部的一对外部电极,贯通导体包括:分别构成贯通导体的两个端部,具有从素体的端面露出的第1端部和位于素体的内侧的第2端部的一对引出导体;将一对引出导体彼此连接,具有在多个层的层叠方向上与引出导体的第2端部重叠的端部的内部导体。

6.在上述层叠型电感器中,贯通导体被构成为包括引出导体与内部导体,并且引出导体的第2端部与内部导体的端部在素体的层叠方向上重叠。烧成时的引出导体以及内部导体各自的收缩量小,能够抑制烧成后在素体内产生的内部应力。因此,在上述层叠型电感器中,能够抑制因内部应力引起的裂纹。

7.其他方面所涉及的层叠型电感器中,第1方向上的引出导体的长度比第1方向上的内部导体的长度短。

8.其他方面所涉及的层叠型电感器具有由引出导体的第2端部和与该第2端部重叠的内部导体的端部形成的阶部。

9.其他方面所涉及的层叠型电感器中,贯通导体包括多个内部导体,内部导体分别相对于第1方向平行地延伸,在第1方向上相邻的内部导体彼此在多个层的层叠方向上彼此的端部重叠。

附图说明

10.图1是表示实施方式所涉及的层叠型电感器的立体图。

11.图2是表示图1所示的素体的贯通导体的立体图。

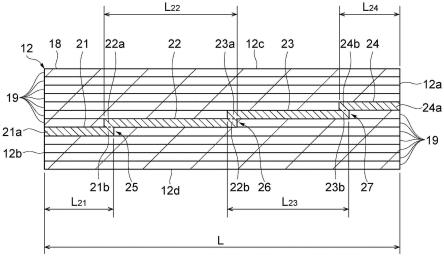

12.图3是图2所示的素体的iii-iii线截面图。

13.图4是表示制造素体时的各个工序的图。

14.图5是表示制造素体时的各个工序的图。

15.图6是表示制造素体时的各个工序的图。

具体实施方式

16.下面,参照附图,说明用于实施本发明的方式。在附图的说明中,对相同或同等的要素使用相同的符号,省略重复的说明。

17.参照图1~3,对实施方式所涉及的层叠型电感器的结构进行说明。如图1所示,实施方式所涉及的层叠型电感器10被构成为包括素体12以及一对外部电极14a、14b。

18.素体12具有大致长方体状的外形,具有在素体12的延伸方向上彼此相对的一对端面12a、12b。素体12还具有在端面12a、12b的相对方向上延伸并且将端面12a、12b彼此连结的4个侧面12c~12f。侧面12d是安装层叠型电感器10时与安装基板相对的安装面,与侧面12d相对的侧面12c在安装时成为顶面。设端面12a、12b的相对方向上的尺寸为长度、侧面12e、12f的相对方向上的尺寸为宽度、侧面12c、12d的相对方向上的尺寸为厚度时,作为一个例子,素体12的尺寸为长度2.5mm

×

宽度2mm

×

厚度0.9mm。

19.素体12具有在磁性体18的内部设置有贯通导体20的结构。如图3所示,素体12具有构成磁性体18的多个磁性体层19在侧面12c、12d的相对方向上层叠的层叠构造。在以下的说明中,将侧面12c、12d的相对方向也称为素体12的层叠方向,将相对于素体12的层叠方向正交的端面12a、12b的相对方向也称为第1方向。

20.磁性体18例如由铁氧体等磁性材料构成。通过将成为磁性体层19的未烧成的磁性体(生片或生坯膏体层)重叠多个并进行烧成而获得磁性体18。构成素体12的磁性体层19的层数作为一个例子是150层。在实际的素体12中,多个磁性体层19被一体化至无法识别其层间的边界的程度。

21.如图2及图3所示,贯通导体20遍及一对端面12a、12b之间延伸。贯通导体20由多个导体构成,在本实施方式中被构成为包含一对引出导体21、24以及一对内部导体22、23。贯通导体20由金属材料构成。在本实施方式中,贯通导体20由ag构成。

22.一对引出导体21、24分别构成贯通导体20的两个端部。更详细地,引出导体21构成位于端面12b侧的贯通导体20的端部,引出导体24构成位于端面12a侧的贯通导体20的端部。一对引出导体21、24分别具有大致矩形平板状的形状,相对于侧面12d平行地延伸。如图3所示,一对引出导体21、24位于多个磁性体层19的不同的层之间。更详细地,引出导体24位于比引出导体21更远离侧面12d的位置。

23.作为端面12a、12b的相对方向(第1方向)上的端部,引出导体21具有从端面12b露出的第1端部21a和位于素体12的内侧的第2端部21b。引出导体21呈沿第1方向延伸的带状,第1端部21a相对较宽。作为第1方向上的端部,引出导体24具有从端面12a露出的第1端部24a和位于素体12的内侧的第2端部24b。引出导体24呈沿第1方向延伸的带状,第1端部24a

相对较宽。

24.作为第1方向上的长度,一对引出导体21、24分别具有长度l

21

、l

24

。长度l

21

、l

24

均比第1方向上的素体12的长度l短。引出导体21的长度l

21

与引出导体24的长度l

24

既可以相同,也可以不同。

25.一对内部导体22、23协作而将一对引出导体21、24彼此连接。更详细地,一对内部导体22、23从引出导体21朝向引出导体24,按内部导体22、内部导体23的顺序排列。一对内部导体22、23分别具有矩形平板状的形状,相对于侧面12d平行地延伸。如图3所示,一对内部导体22、23位于多个磁性体层19的不同的层之间。更详细地,内部导体23位于比内部导体22更远离侧面12d的位置。

26.作为第1方向上的端部,内部导体22具有位于端面12b侧的第1端部22a与位于端面12a侧的第2端部22b。同样,作为第1方向上的端部,内部导体23具有位于端面12b侧的第1端部23a与位于端面12a侧的第2端部23b。

27.作为第1方向上的长度,一对内部导体22、23分别具有长度l

22

、l

23

。长度l

22

、l

23

均比第1方向上的素体12的长度l短。内部导体22的长度l

22

与内部导体23的长度l

23

既可以相同,也可以不同。也可以将内部导体22、23各自的长度l

22

、l

23

设计成比引出导体21、24的长度l

21

、l

24

长。

28.如图3所示,内部导体22的第1端部22a与引出导体21的第2端部21b在素体12的层叠方向上重叠。更详细地,内部导体22的第1端部22a从上侧(即,侧面12c侧)与引出导体21的第2端部21b重叠。由此,引出导体21与内部导体22相互接合并电连接。另外,在内部导体22的第1端部22a与引出导体21的第2端部21b的接合部位形成有阶部25。

29.另外,内部导体23的第2端部23b与引出导体24的第2端部24b在素体12的层叠方向上重叠。更详细地,内部导体23的第2端部23b从下侧(即,侧面12d侧)与引出导体24的第2端部24b重叠。由此,引出导体24与内部导体23相互接合并电连接。另外,在内部导体23的第2端部23b与引出导体24的第2端部24b的接合部位形成有阶部27。

30.再有,内部导体22的第2端部22b与内部导体23的第1端部23a在素体12的层叠方向上重叠。更详细地,内部导体22的第2端部22b从下侧(即,侧面12d侧)与内部导体23的第1端部23a重叠。由此,一对内部导体22、23相互接合并电连接。另外,在内部导体22的第2端部22b与内部导体23的第1端部23a的接合部位形成有阶部26。

31.这样,贯通导体20具有三个阶部25~27,构成贯通导体20的四个导体21~24呈阶梯状配置。四个导体21~24从引出导体21朝向引出导体24逐渐远离侧面12d。

32.一对外部电极14a、14b分别设置于素体12的端面12a、12b。外部电极14a覆盖端面12a的整个区域,与露出于端面12a的贯通导体20的端部直接接触并接合。同样,外部电极14b覆盖端面12b的整个区域,与露出于端面12b的贯通导体20的端部直接接触并接合。在本实施方式中,如图1所示,各个外部电极14a、14b一体地覆盖端面12a、12b以及与端面12a、12b相邻的区域的侧面12c~12f。各个外部电极14a、14b由一层或多层的电极层构成。构成各个外部电极14a、14b的电极材料例如可以采用ag等金属材料。

33.接着,参照图4~6,对形成包含上述的贯通导体20的素体12的步骤进行说明。

34.在形成贯通导体20时,首先,如图4(a)所示,准备成为素体12的一部分的生片18a。生片18既可以由一层构成,也可以由多层构成。接着,如图4(b)所示,在成为素体12的端面

12b的生片18a的边缘设置引出导体21。此时的引出导体21处于导电性膏体的状态,还没有被烧成。例如通过丝网印刷法来涂布导电性膏体。接下来,如图4(c)所示,在生片18a上的从引出导体21至成为素体12的端面12a的生片18a的边缘的整个矩形区域涂布形成生坯膏体层18b。

35.接着,如图5(a)所示,在生坯膏体层18b以及引出导体21的第2端部21b之上设置导电性膏体的状态的内部导体22。内部导体22以第1端部22a重叠于引出导体21的第2端部21b上的方式设置。接下来,如图5(b)所示,在生坯膏体层18b上涂布形成生坯膏体层18c。更详细地,生坯膏体层18c整体地设置于从内部导体22至成为素体12的端面12a的生片18a的边缘的矩形区域。另外,也涂布形成整体地覆盖引出导体21的生坯膏体层18d。此外,如图5(c)所示,在生坯膏体层18c以及内部导体22的第2端部22b之上设置导电性膏体的状态的内部导体23。内部导体23以第1端部23a重叠于内部导体22的第2端部22b上的方式设置。

36.接着,如图6(a)所示,在生坯膏体层18c上涂布形成生坯膏体层18e。更详细地,生坯膏体层18e整体地设置于从内部导体23至成为素体12的端面12a的生片18a的边缘的矩形区域。另外,也涂布形成一体地覆盖引出导体21与内部导体22的生坯膏体层18f。接下来,如图6(b)所示,在生坯膏体层18e以及内部导体23的第2端部23b之上设置导电性膏体的状态的引出导体24。引出导体24以第2端部24b重叠于内部导体23的第2端部23b上的方式设置。此外,如图6(c)所示,涂布形成一体地覆盖引出导体21与一对内部导体22、23的生坯膏体层18g。然后,涂布形成一体地覆盖一对引出导体21、24与一对内部导体22、23的生坯膏体层(未图示),得到未烧成的素体12。

37.然后,对未烧成状态的素体12进行烧成处理,得到上述的素体12。最后,在素体12的端面12a、12b分别设置外部电极14a、14b,完成上述层叠型电感器10。

38.如以上所说明的那样,在层叠型电感器10中,设置于烧成后的素体12(烧成素体)内的贯通导体20被构成为包括一对引出导体21、24与一对内部导体22、23,并且引出导体21、24的第2端部21b、24b与内部导体22、23的端部22a、23b在素体12的层叠方向上重叠。

39.相邻的导体21~24彼此在各自的端部上电连接,作为整体发挥作为贯通导体20的作用。另外,关于端面12a、12b的相对方向,与由一个平坦的导体构成贯通导体时的长度l相比,各个导体21~24的长度l

21

~l

24

的长度缩短。由此,可降低素体12的烧成时的各个导体21~24的收缩量,并且可抑制烧成后在素体12内产生的内部应力。因此,在层叠型电感器10中,因内部应力引起的裂纹得到抑制。

40.另外,在层叠型电感器10中,一对引出导体21、24各自的长度l

21

、l

24

被设计成比内部导体22、23的长度l

22

、l

23

短。在这种情况下,可减少素体12的烧成时的引出导体21、24的收缩量。因此,例如,可抑制引出导体21、24从端面12a、12b进入素体12的内部的情况,并且可有效地抑制引出导体21、24与外部电极14a、14b之间的连接不良。

41.以上,对本发明的实施方式进行了说明,但是,本发明并非局限于上述实施方式,在不脱离其宗旨的范围内可以进行各种更改。例如,贯通导体的内部导体的数量并不限于2个,也可以是1个或3个以上。另外,一对引出导体也可以位于多个层的同一层之间。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1