用于低噪声缩放像素的沟槽栅源极跟随器的制作方法

用于低噪声缩放像素的沟槽栅源极跟随器

1.本技术要求于2021年9月29日提交美国专利商标局、申请号为17/489,735、发明名称为“trench-gate source follower for low-noise scaled pixel”的us申请的优先权,其全部内容通过引用结合在本技术中。

技术领域

2.本发明总体上涉及互补金属氧化物半导体(complementary metal-oxide semiconductor,cmos)图像传感器。更具体地,实施例涉及用于与cmos图像传感器(cmos image sensor,cis)像素集成的沟槽栅源极跟随器晶体管设计。

背景技术:

3.许多现代电子器件应用包括集成数码相机和/或其他成像系统,这些都是基于互补金属氧化物半导体(cmos)图像传感器(cis)技术的。cis通常可以包括像素阵列,每个像素包括单个光电传感器(例如,光电二极管),或一组多个光电传感器。每个像素还可以包括支持硬件,例如源极跟随器晶体管,用于将光电传感器的光学响应转换为相应的电信号,以供其他部件使用。像素的性能可能与其尺寸有关。例如,增加像素中光电二极管面积的尺寸可以增加光电二极管的满阱容量(full-well capacity,fwc),这样往往支持更高的动态范围、更高的对比度和/或其他图像性能改进。同理,增加源极跟随器晶体管的有源面积可以提高像素的噪声性能,例如通过增加其信噪比(signal-to-noise ratio,snr)。

4.对于任何给定的像素尺寸,占用空间必须由光电传感器和源极跟随器晶体管共享。因此,一者尺寸的任何增加会迫使另一者尺寸的减小,使得像素设计通常代表图像性能(与光电传感器的尺寸和对应的fwc有关)与噪声性能(与源极跟随器晶体管的有源面积有关)之间的权衡。随着像素尺寸的不断减小,要在优化fwc的同时保持可接受的噪声性能就变得越来越困难。

技术实现要素:

5.实施例提供了用于实现与互补金属氧化物半导体(cmos)图像传感器(cis)像素集成的沟槽栅源极跟随器(trench-gate source-follower,tgsf)晶体管的电路、设备和方法。tgsf晶体管至少部分地构建在蚀刻到诸如硅晶圆衬底、cis晶圆的氧化物扩散区域等的衬底中的沟槽中。在沟槽的内壁周围植入连续掺杂区域,以形成埋沟式电流通道。形成沟槽栅,以具有填充沟槽体积的至少埋入部分。可以在沟槽栅极的埋入部分和埋沟式电流通道之间设置栅氧化层。在沟槽栅的两端形成晶体管的漏极区域和源极区域。激活沟槽栅导致电流经由沟槽栅极的埋入部分周围的埋沟式电流通道在栅极区域和源极区域之间流动。埋沟式电流通道的几何形状可以有效地增加源极跟随器晶体管的有源区域的宽度,而不增加其物理布局宽度。

6.根据一组实施例,提供了一种用于制造沟槽栅源极跟随器(tgsf)晶体管的方法。该方法包括:在半导体衬底中形成埋沟式电流通道,使得所述埋沟式电流通道为植入到沟

槽壁中的所述半导体衬底中的连续掺杂区域,所述沟槽壁围绕蚀刻到所述半导体衬底中的沟槽;沉积多晶硅以满溢所述沟槽的体积,使得所述多晶硅的第一部分与所述沟槽的体积一致,以形成沟槽栅的埋入部分,并且所述多晶硅的第二部分在所述沟槽的表面水平上延伸,所述表面水平与所述半导体衬底的表面重合;将所述多晶硅的第二部分图案化,以形成所述沟槽栅的暴露部分;在与所述沟槽栅的第一侧相邻的所述半导体衬底中植入漏极区域;以及在与所述沟槽栅的第二侧相邻的所述半导体衬底中植入源极区域,所述第二侧与所述第一侧相对。

7.根据另一组实施例,提供了一种沟槽栅源极跟随器(tgsf)晶体管。该tgsf晶体管包括:埋沟式电流通道,形成在半导体衬底中作为连续掺杂区域,所述连续掺杂区域植入到沟槽壁中的所述半导体衬底中,所述沟槽壁围绕蚀刻到所述半导体衬底中的沟槽;沟槽栅,通过沉积多晶硅以满溢所述沟槽的体积形成,使得所述沟槽栅包括:埋入部分,由所述多晶硅的填充所述沟槽的体积并与所述沟槽的体积一致的第一部分形成;和暴露部分,通过将所述多晶硅的在所述沟槽的表面水平上延伸的第二部分图案化形成,所述表面水平与所述半导体衬底的表面重合;漏极区域,植入在与所述沟槽栅的第一侧相邻的所述半导体衬底中;和源极区域,植入在与所述沟槽栅的第二侧相邻的所述半导体衬底中,所述第二侧与所述第一侧相对。

8.根据另一组实施例,提供了一种互补金属氧化物半导体(cmos)图像传感器(cis)像素物理构架。该cis像素物理架构包括:半导体衬底;具有光电二极管集合的像素块,所述光电二极管集合与半导体衬底集成;和与所述半导体衬底集成的氧化物扩散区域,所述氧化物扩散区域与所述光电二极管集合相邻并且具有至少设置在其上的沟槽栅源极跟随器(tgsf)晶体管。该tgsf晶体管包括:埋沟式电流通道,形成在所述氧化物扩散区域中作为连续掺杂区域,所述连续掺杂区域植入到沟槽壁中的所述半导体衬底中,所述沟槽壁围绕蚀刻到所述半导体衬底中的沟槽;沟槽栅,通过沉积多晶硅以满溢所述沟槽的体积形成,使得所述沟槽栅包括:埋入部分,由所述多晶硅的填充所述沟槽的体积并与所述沟槽的体积一致的第一部分形成;和暴露部分,通过将所述多晶硅的在所述沟槽的表面水平上延伸的第二部分图案化形成,所述表面水平与所述半导体衬底的表面重合;漏极区域,植入在与所述沟槽栅的第一侧相邻的所述氧化物扩散区域中;和源极区域,植入在与所述沟槽栅的第二侧相邻的所述氧化物扩散区域中,所述第二侧与所述第一侧相对。

附图说明

9.本文中提及的并构成本文一部分的附图示出了本公开的实施例。附图连同说明书一起用于解释本发明的原理。

10.图1示出了说明性数字成像系统的一部分的简化框图,作为本文中描述的各种实施例的上下文。

11.图2a和2b分别示出了实现为平面源极跟随器晶体管的常规源极跟随器块的侧截面视图和立体视图,这对于常规的cis像素设计来说是典型的。

12.图3a-3d示出了根据本文中描述的各种实施例的说明性新型沟槽栅源极跟随器(tgsf)晶体管的各种简化视图。

13.图4a-4l示出了根据本文中描述的各种实施例的说明性刻蚀优先方法的一系列阶

段的简化视图。

14.图5a-5b示出了根据本文中描述的各种实施例的说明性植入优先方法的两个阶段的简化视图。

15.图6a-6c示出了在(例如,硅晶圆的)氧化物扩散区域上tgsf晶体管在典型安装环境中的模拟实现。

16.图7示出了根据各种实施例的具有集成tgsf晶体管的说明性cis像素的简化物理布局。

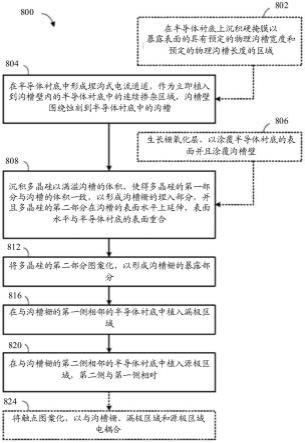

17.图8示出了根据本文中描述的各种实施例的用于制造tgsf晶体管的说明性方法的流程图。

18.在所附附图中,相似的部件和/或特征可以具有相同的附图标记。此外,相同类型的各种部件可以通过在附图标记之后跟有区分相似部件的第二标记来区分。如果说明书中仅使用第一附图标记,则该描述可应用于具有相同第一附图标记的相似部件中的任何一个部件,而不考虑第二附图标记。

具体实施方式

19.在以下描述中,为了彻底理解本发明,提供了许多具体细节。然而,本领域技术人员应当理解,本发明可以在没有这些细节中的一个或多个的情况下实现。在其他示例中,出于简洁的目的,本领域已知的特征和技术将不再描述。

20.图1示出了说明性数字成像系统100的一部分的简化框图,作为本文中描述的各种实施例的上下文。数字成像系统100围绕互补金属氧化物半导体(cmos)图像传感器(cis)技术构建。这样的cis系统通常可以包括像素105的阵列,例如以行和列布置的百万个像素105。每个像素105可以包括光电传感器块110,该光电传感器块110可以包括单个光电二极管115(例如,或任何合适的光电传感器),或一组多个光电二极管115。例如,每个像素105可以用以拜尔色彩模式(例如,一个红色光电二极管115、一个蓝色光电二极管115、两个绿色光电二极管115)或任何其他合适的模式布置的一组四个光电二极管115来实现。

21.像素105还包括附加部件,以促进光电传感器块110用于光学感应。如图所示,实施例可以包括增益块120、复位块130、源极跟随器块140和选择块150。增益块120可以控制像素105的增益,例如通过实现双转换增益(dual conversion gain,dcg)。复位块130可以选择性地复位像素105的部件。源极跟随器块140可以支持将来自光电传感器块110的输出转换成指示由光电传感器块110检测到的光学信息的电信号。选择块150可以支持从像素105的阵列中选择像素105信号,例如响应于经由总线160接收的控制信号。例如,总线160可以是列选择总线等。

22.随着技术的进步,在许多应用环境中趋向于减小像素105的尺寸。实际上,许多数字成像应用在其图像传感器芯片上寻求不断增加的像素105的数量和密度(即,推动像素105尺寸的减小),同时还要求设计继续满足或超过多个性能参数,例如与图像对比度、动态范围、捕获帧率、信噪比(snr)、功耗等相关的性能参数。然而,已经证明,像素105的某些性能参数往往通过减小像素105内部件的尺寸而受到不利影响。例如,减小光电传感器块110中光电二极管115的尺寸可以减小其满阱容量(fwc),这往往可以产生更低的动态范围、更低的对比度和/或其他图像性能降低。同理,减小源极跟随器块140的有源面积可以降低像

素105的噪声性能,例如通过降低其信噪比(snr)。例如,减小源极跟随器块140的有源面积往往可能增加其对低频噪声(有时被称为1/f噪声)和/或突发噪声(也被称为随机电报信号(random telegraph signal,rts)噪声、脉冲噪声、双稳态噪声等)的敏感度。一些常规的像素105设计试图在像素105的有限占用空间内将部件尺寸最大化,但是每个像素105的占用空间由其所有部件共享;增加一个部件(例如,光电传感器块110)的尺寸往往需要减小另一个部件(例如,源极跟随器块140)的尺寸。因此,常规的像素105设计经常被迫在图像性能(与光电传感器的尺寸和对应的fwc有关)与噪声性能(与源极跟随器晶体管的有源面积有关)之间进行权衡。

23.随着像素105尺寸的不断减小,甚至要在图像性能和噪声性能之间达到可接受的权衡就变得越来越困难。为了增加的上下文,图2a和2b分别示出了实现为平面源极跟随器晶体管200的常规源极跟随器块140的侧截面视图和立体视图,这对于常规的cis像素设计来说是典型的。如图所示,平面源极跟随器晶体管200包括漏极区域210、源极区域215和栅极区域220,均在衬底205上实现。例如,衬底205是p掺杂硅晶圆,漏极区域210和源极区域215中的每一个区域都是衬底205的相应的n掺杂区域,并且栅极区域220是在衬底205上沉积构建(例如,通过沉积)的多晶硅结构。向栅极区域220施加栅极电压可以导致在漏极区域210和源极区域215之间形成电流通道并且电流在漏极区域210和源极区域215之间以箭头225的方向流动。电流通道的长度(l)在图2a中示为尺寸230。平面源极跟随器晶体管200的有源区域宽度(w)在图2b中示为尺寸235。也如图2b所示,可以使用诸如浅沟槽隔离(shallow trench isolation,sti)区域的隔离区域240来界定(例如,与相邻设备隔离)有源区域。

24.实现cis像素性能的特定水平可以涉及实施源极跟随器块140以在阈值可接受噪声水平内产生至少阈值水平的跨导(gm)。跨导量在功能上可以对应于性能特征,例如帧率、功耗和某些类型的噪声。一般来说,广义的源极跟随器晶体管在饱和区域的跨导可以计算为:

25.gm=wc

oxvsat

26.其中,w是源极跟随器晶体管的宽度(例如,常规设计中图2b的尺寸235),cox氧化物电容,v

sat

是饱和电压。可以看出,源极跟随器晶体管的跨导往往与其宽度成正比,使得宽度的减小往往会产生跨导相关性能的相应下降。

27.此外,源极跟随器晶体管栅极处的电压噪声(s

vg

)可以计算为:

[0028][0029]

其中,m是经验参数,β是频率相关参数。源极跟随器晶体管栅极处的电压信号往往与栅极电容成正比,表示为cox*w*l,其中,l是电流通道长度(例如,常规设计中图2a的尺寸230)。根据栅极电压噪声和栅极电压信号可以得出,源极跟随器晶体管的snr在功能上与cox3*w2*l2相关。因此,可以看出,源极跟随器晶体管的snr往往与其宽度和长度成正比,使得源极跟随器晶体管尺寸的减小往往会产生噪声性能的相应降低。值得注意的是,在常规设计中,这样的噪声性能往往会在设备边缘处进一步降低,例如在隔离区域240中。例如,在电流通道中流动的电流可能会被困在sti区域中,并可能产生额外的噪声。

[0030]

许多现代数字成像应用已将像素尺寸降低到大约1.12微米的规模。即使在如此小

的规模下,基于平面源极跟随器晶体管200的一些常规设计已经在可接受噪声水平下实现了足够的跨导(gm),以提供高cis性能。然而,随着像素尺寸的不断减小,要保持所需的跨导(gm)和snr水平变得极其困难、不切实际甚至不可能。

[0031]

如上所述,在常规的平面源极跟随器晶体管200中,栅极区域220设置在衬底205的顶部。向栅极区域220施加栅极电压可以导致在衬底205的表面正下方(栅极区域220的正下方),在漏极区域210和源极区域215之间形成电流通道。因此,形成的电流通道的长度和宽度与栅极区域220的长度和宽度有关;电流通道的物理布局宽度近似于电流通道的有效有源宽度。例如,减小栅极区域220的长度或宽度往往减小电流通道的长度或宽度,从而影响源极跟随器的性能。

[0032]

本文中描述的实施例提供了一种使用沟槽栅源极跟随器(tgsf)晶体管实现的新型源极跟随器块140。通常,本文中所描述的tgsf晶体管的实施例包括蚀刻到硅衬底中的沟槽。植入围绕沟槽的壁(例如,作为与漏极区域和源极区域隔离的n掺杂区域),并且形成沟槽栅区域,以包括至少填充沟槽的多晶栅结构。向多晶栅施加栅极电压会导致在沟槽周围形成埋入的电流通道,该埋入的电流通道在多晶栅的多侧周围沿着沟槽的壁提供了平行电流路径。从而,tgsf的有源区域能够明显大于电流通道的物理布局宽度。因此,tgsf晶体管可以提供比具有相同物理布局尺寸的常规平面源极跟随器晶体管更好的性能(例如,跨导相关和/或噪声相关性能的增加)。

[0033]

图3a-3d示出了根据本文中描述的各种实施例的说明性新型沟槽栅源极跟随器(tgsf)晶体管300的各种简化视图。tgsf晶体管300可以是图1的源极跟随器块140的实现。首先转到图3a,示出了tgsf晶体管300的栅极区域的立体视图。在一些实现中,tgsf晶体管300的源极区域和漏极区域以与常规的平面型源极跟随器晶体管基本相同的方式实现。如图所示,栅极区域可以包括蚀刻到诸如硅晶圆的一部分的硅衬底205中的沟槽。植入沟槽的壁,以形成埋入的电流通道320。例如,衬底为p型衬底,埋沟式电流通道320为n掺杂区域。沟槽由形成沟槽栅340的多晶栅结构填充,该沟槽栅340通过栅氧化层330与埋沟式电流通道320隔开。当向沟槽栅340施加栅极电压时,允许电流(例如,电子)流过埋入的电流通道320。例如,电流主要在埋沟式电流通道320中沿着沟槽栅340的两侧以箭头315的方向流动。

[0034]

图3b示出了根据图3a所示的图示的轴规定的tgsf晶体管300b的与x-z平面中的切口对应的自上而下的剖视图。该视图示出了栅极区域302、漏极区域304和源极区域306。考图3a所描述的,栅极区域302包括在蚀刻到衬底205中的沟槽中形成的沟槽栅340。沟槽栅340被栅氧化层330包围,并且植入沟槽的壁,以形成埋沟式电流通道320。埋沟式电流通道320以漏极区域304和源极区域306为界。漏极区域304和源极区域306中的每一个区域可以形成为植入在较轻掺杂区域355中的相应的较高掺杂区域350,以形成掺杂梯度。例如,每个较轻掺杂区域355是所谓的轻掺杂漏极(lightly-doped drain,ldd)区域。例如,漏极区域304和源极区域306中的每一个区域都包括各自的n掺杂植入区域。如上所述,当向沟槽栅340施加栅极电压时,电流可以至少沿着沟槽栅340的两侧以箭头315的方向(例如,从漏极区域304到源极区域306)流过埋沟式电流通道320。

[0035]

图3c和3d分别示出了tgsf晶体管300c的长度向剖视图(y-z平面中的切口)和tgsf晶体管300d的宽度向剖视图(y-x平面中的切口)。图3c的视图示出了与图3b中相同的区域和部件,包括栅极区域302、漏极区域304和源极区域306。图3d的视图是通过栅极区域302被

切开的,使得仅可以看到栅极区域302的部件。从图3c和3d的视图可以看出,栅极区域302是通过在蚀刻到衬底205中的沟槽中形成沟槽栅340、植入沟槽的壁以形成埋沟式电流通道320并将埋沟式电流通道320通过栅氧化层330与沟槽栅340分离来实现的。

[0036]

图3a-3d的视图是高度简化的视图。例如,虽然各种区域和结构被示为具有方角和限定的边缘,但这样的区域和结构的实际实现通常具有有机形状。因此,这样的区域和结构的边界或边缘实际上不具有完全可定义的边界,而是倾向于以更具统计性的方式定义(例如,通过标称值、工艺角等),这是本领域技术人员理解的。因此,各种所示的区域和结构一般旨在显示结构和区域的一般相对布置、结构和区域之间的一般隔离等;但并非旨在定义特定的形状、尺寸、边界和/或其他特征。

[0037]

如本文中所述,tgsf晶体管300的实施例包括栅极区域302,该栅极区域302至少部分地形成在蚀刻的沟槽内,以提供埋沟式电流通道320。图4a-5b示出了用于制造这种tgsf晶体管300的两种方法:“蚀刻优先”方法;和“植入优先”过程。蚀刻优先方法通常在将掺杂区域植入蚀刻的沟槽的壁中之前蚀刻沟槽,以创建埋沟式电流通道320。植入优先过程通常在将沟槽蚀刻到已经掺杂的区域中之前在衬底中掺杂大区域(例如,大阱),以创建埋沟式电流通道320。

[0038]

图4a-4l示出了根据本文中描述的各种实施例的说明性刻蚀优先方法的一系列阶段400的简化视图。每个阶段400由cmos晶圆的一部分的两个视图来说明:右侧的简化的长度向剖视图(例如,类似于图3c的剖视图);和左侧的简化的宽度向剖视图(例如,类似与图3d的剖视图)。对于增加的上下文,每个简化的长度向剖视图示出了与选择晶体管区域(在图4a中示为区域404)相邻的源极跟随器晶体管区域(在图4a中示为区域402),例如,对应于cmos图像传感器像素布局中源极跟随器块140和选择块150的典型布局。

[0039]

为了上下文,图4a示出了第一阶段400a,其可以与制造常规的平面型源极跟随器晶体管的阶段类似。如图所示,为选择晶体管(在所示的选择晶体管区404中)已经植入了电流通道区域410(例如,n型阱),并且在硅衬底205的表面上形成屏蔽氧化层415(例如,以保护暴露的表面)。

[0040]

图4b示出了蚀刻优先方法的下一阶段400b,其中,在屏蔽氧化层415的顶部沉积硬掩膜420。调整硬掩膜420的尺寸适合于待蚀刻的沟槽的几何形状。如上所述,tgsf晶体管300的一些实施例被制造为具有从自上而下的布局来看与常规的平面型源极跟随器晶体管相同或相似的几何形状。具体地,可以制造这样的实施例,使得多晶栅的顶部具有与常规的平面型源极跟随器晶体管相同的长度和宽度(间距)。因此,可以使用常规图案来将阶段400b中的硬掩膜420图案化,该常规图案用于制造具有相同多晶栅尺寸的常规的平面型源极跟随器晶体管。

[0041]

例如,为了制造常规的平面型源极跟随器晶体管,使用与硬掩膜420相同(或相似)形状的n型埋入通道掩模或“nbc掩模”来在衬底205表面的正下方植入n型阱。在这样的常规方法中,所得的植入区域可以看起来类似于为选择晶体管植入的区域410。在这样的常规方法的后期阶段,可以在这些植入区域中的每一个植入区域的顶部上沉积多晶栅并将其图案化,以形成选择晶体管和平面型源极跟随器晶体管。

[0042]

相比之下,图4c示出了蚀刻优先方法的下一阶段400c,其中,基于来自阶段400b的硬掩膜420的几何形状,在衬底205中蚀刻沟槽430。硬掩膜420由基本上不受蚀刻工艺影响

的材料制成。例如,至少在晶圆表面的所示部分上施加化学蚀刻,并且硬掩膜420使得蚀刻仅被限制在未掩模区域。因此,硬掩膜420的几何形状至少部分地限定了沟槽430的几何形状。可以基于许多因素来确定沟槽430的尺寸。在一些实施例中,沟槽430的宽度小于其长度。

[0043]

图4d示出了蚀刻优先方法的下一阶段400d,其中,在沟槽430的壁上进行植入,以形成埋沟式电流通道320。为了到达沟槽430的侧壁,可以以不垂直于晶圆表面的一个或多个角度进行植入(由实线箭头440表示)。例如,为源极跟随器晶体管植入n通道阱通常在单个步骤中以大约90度进行(即,垂直于晶圆表面的指向,如虚线箭头所示,)。可以以多个步骤进行阶段400d的植入。例如,使用四个植入步骤来植入沟槽430的四个侧壁中的每一个侧壁。至少基于沟槽430的深度和开口的几何形状(即,沟槽430的长度和宽度),以对应的角度进行每个植入步骤。例如,以相对于晶圆表面偏离法线15-20度的角度进行每个植入步骤。

[0044]

图4e示出了蚀刻优先方法的下一阶段400e,其中,去除硬掩膜420,并且去除屏蔽氧化层415的剩余部分。

[0045]

图4f示出了蚀刻优先方法的下一阶段400f,其中,清洁晶圆表面,并且在晶圆表面上生长栅氧化层330。可以看出,在沟槽430的所有壁的后面植入了埋沟式电流通道320,并且沟槽430的所有壁也被栅氧化层330覆盖。

[0046]

图4g示出了蚀刻优先方法的下一阶段400g,其中,在晶圆表面上(至少在所示区域中)沉积多晶硅450,包括填充沟槽430的整个体积。随后将该多晶硅450图案化,以形成tgsf晶体管300(即,沟槽栅340)和选择晶体管的多晶栅。在一些实施例中,期望多晶栅的顶表面处于晶圆表面上方的某个栅极高度处,例如以支持进一步处理。然而,如图所示,所沉积的多晶硅450的高度在沟槽430的区域中可以低于周围区域。因此,在一些实施例中,在阶段400g中沉积多晶硅450,使得沟槽430的区域中减小的高度仍然至少是栅极高度。

[0047]

图4h示出了蚀刻优先方法的下一阶段400h,其中,将阶段400g中沉积的多晶硅450抛光至与期望一致的高度。在一些实施例中,利用多晶硅化学机械抛光(chemical-mechanical polishing,cmp)来有效地磨损和抛光多晶硅450,以具有光滑和一致的表面。可以看出,虽然多晶硅450的顶表面在阶段400h之后一致,但多晶硅450的深度适于填充沟槽430的体积。

[0048]

图4i示出了蚀刻优先方法的下一阶段400i,其中,在多晶硅450的顶部沉积硬掩膜460并将其图案化。

[0049]

图4j示出了蚀刻优先方法的下一阶段400j,其中,基于硬掩膜460的几何形状蚀刻多晶硅450,并且剥离硬掩膜460。蚀刻留下与各个多晶栅对应的几何形状的多晶硅450。具体地,蚀刻有效地形成了tgsf晶体管300的沟槽栅340和选择晶体管的选择栅极470。如上所述,从自上而下的布局来看,可以将沟槽栅340的几何形状蚀刻成看起来与常规的平面型源极跟随器晶体管的几何形状相同。然而,在晶圆表面下方,可以看出栅极区域的几何形状包括具有被栅氧化层330和埋沟式电流通道320包围的埋入壁的沟槽栅340。

[0050]

图4k示出了蚀刻优先方法的下一阶段400k,其中,为至少漏极区域304和源极区域306植入较轻掺杂区355(例如,ldd植入)。在一些实施例中,如图所示,植入较轻掺杂区域355,以形成与埋沟式电流通道320的壁相邻的沿tgsf晶体管300的长度(根据图3a-3d的规定,在z方向上)延伸的阱,并且植入较轻掺杂区域355,以在tgsf晶体管300的源极端和漏极

端处超越埋沟式电流通道320的端部。当电流流过通道时,这种超越埋沟式电流通道320的源极端和漏极端可以有助于确保埋沟式电流通道320和较轻掺杂区域355之间的良好传导。

[0051]

可以看出,阶段400j中蚀刻多晶硅450也可以支持较轻掺杂区域355的性能和/或其他传导特征。例如,可以蚀刻多晶硅450,使得沟槽栅340在x方向(根据图3a-3d的规定)上与硅重叠,但在z方向(根据图3a-3d的规定)上与沟槽430的边缘基本对齐。在x方向上沟槽栅340与硅衬底205的重叠可以利于在宽度方向上电流流动的覆盖。在z方向上沟槽栅340的边缘与沟槽430边缘对齐支持较轻掺杂区域355与埋沟式电流通道320的导电耦合。例如,制造工艺变化可能导致z方向上沟槽栅340和硅衬底205的重叠切断较轻掺杂区域355和埋沟式电流通道320之间的导电耦合的情况。

[0052]

在可替换的实施例中,不是在阶段400k中植入较轻掺杂区域355,而是可以在植入埋沟式电流通道320之前植入较轻掺杂区域355,并且以确保两者之间适当的导电耦合的方式植入埋沟式电流通道320。在一些这样的实施例中,可以在蚀刻沟槽430之前,例如在阶段400a之前、在阶段400a和400b之间或者在阶段400b和400c之间,植入较轻掺杂区域355。在其他这样的实施例中,可以在蚀刻沟槽430之后但在植入埋沟式电流通道320之前,例如在阶段400c和400d之间,植入较轻掺杂区域355。

[0053]

图4l示出了蚀刻优先方法的下一个(例如,最终)阶段400l,其中,在较轻掺杂区域355中植入较高掺杂区域350,以形成漏极区域304和源极区域306,沉积间隔物480并将其图案化,并且将触点(未示出)图案化。在一些实施例中,在阶段400l之后,从自上而下的布局来看,所形成的tgsf晶体管300可以看起来与常规的平面型源极跟随器晶体管相同。例如,所形成的tgsf晶体管300的沟槽栅340可以具有与常规的平面型源极跟随器晶体管的多晶栅相同的物理布局长度和宽度。

[0054]

图5a-5b示出了根据本文中描述的各种实施例的说明性植入优先方法的两个阶段500的简化视图。类似于图4a-4l,每个阶段500由cmos晶圆的一部分的两个视图来说明(右侧的简化的长度向剖视图,左侧的简化的宽度向剖视图),并且每个简化的长度向剖视图示出了与选择晶体管区域相邻的源极跟随器晶体管区域。两个阶段500旨在与图4a-4l的蚀刻优先方法的阶段结合,如下所述,以产生植入优先方法。例如,与蚀刻优先方法一样,植入优先方法可以在阶段400a和400b开始,如图4a和4b所示。具体地,为选择晶体管已经植入电流通道区域410,在硅衬底205的表面上形成屏蔽氧化层415,并且根据要蚀刻的沟槽的几何形状,在屏蔽氧化层415的顶部沉积硬掩膜420。

[0055]

转到图5a,示出了植入优先方法的下一阶段500a,其中,形成植入区域510。例如,通过硬掩膜420形成的开口,在衬底205表面下方植入大的n型阱,以形成大于所需沟槽430的植入区域510。植入可以涉及倾斜植入方向(例如,如上所述),使得植入延伸到硬掩膜420边缘下方的区域中。这些区域最终将成为埋沟式电流通道320。这样的植入可以涉及多个角度的植入和/或多个步骤。

[0056]

图5b示出了植入优先方法的下一阶段500b,其中,基于(例如,来自阶段400b)硬掩膜420的几何形状,在衬底205中蚀刻沟槽430。如图所示,由于已经植入了沟槽430的区域,因此蚀刻自动形成埋沟式电流通道320。例如,阶段500b的结束可能看起来与阶段400d的结束相似。因此,植入优先方法的剩余阶段可以遵循图4e-4l中所示的蚀刻优先方法的剩余阶段400e-400l。

[0057]

无论所得到的tgsf晶体管300是通过蚀刻优先方法还是通过植入优先方法形成的,所得到的tgsf晶体管300可以被形成为看起来与常规的平面型源极跟随器晶体管相同(从自上而下的布局来看)。例如,所形成的tgsf晶体管300的沟槽栅340可以具有与常规的平面型源极跟随器晶体管的多晶栅相同的物理布局长度和宽度。然而,在晶圆表面下方,埋入的沟槽栅340被埋沟式电流通道320包围,以形成具有明显不同的有效有源宽度的电流通道。

[0058]

例如,图6a-6c示出了在(例如,硅晶圆的)氧化物扩散区域上tgsf晶体管300在典型安装环境中的模拟实现。图6a示出了在共享的衬底205上与选择块150相邻的源极跟随器块140的说明性立体视图,源极跟随器块140实现为tgsf晶体管300。从图6a的视点来看,源极跟随器块140可以通过常规的平面型源极跟随器晶体管类似实现。然而,图6b示出了相同的源极跟随器块140和选择块150,去除了它们各自的多晶栅,显示出了tgsf晶体管300实现的沟槽430。

[0059]

为了更清楚,图6c示出了与图6b中定义的切口620对应的模拟视图。该视图示出了去除了沟槽栅340的沟槽430(如图6b所示)和在沟槽430周围形成埋沟式电流通道320的植入区域。该模拟视图示出了往往更重地掺杂更靠近沟槽430的壁的区域,并且掺杂水平通常随着远离沟槽壁而降低。可以看出,形成在沟槽430的壁周围的埋沟式电流通道320中的电流通道的总有效有源宽度可以明显大于电流通道的物理布局宽度610(对应于沟槽栅340的宽度)。

[0060]

图7示出了根据各种实施例的具有集成rgsf晶体管300的说明性cis像素700的简化物理布局。说明性布局可以是图1的框图的实现。所示布局的中心区域包括具有四个光电二极管115的光电传感器块110。所示布局的上部包括增益块120和复位块130,具有对应的触点。所示布局的下部包括选择块150和新型源极跟随器块140,该新型源极跟随器块140实现为具有沟槽栅340的tgsf晶体管300。可以看出,各个部件块的宽度是通过布局的设计来确定的。

[0061]

如上所述,至少由于掺杂参数和边缘隔离结构,源极跟随器块140的有源层的有源区域具有可定义的宽度(w),表示为tgsf晶体管300的物理布局宽度610。在一些实现中,宽度610至少部分地由像素设计参数和制造工艺约束来确定。例如,如上所述,像素占用空间设计平衡了光电传感器块110和包括源极跟随器块140(此处由tgsf晶体管300实现)的支持部件之间的分配的空间。分配的空间通常可以定义晶体管部件的最大(或标称)宽度。如图所示,tgsf晶体管300的实施例可以占据与常规的平面型源极跟随器晶体管基本相同的布局面积,包括占据相同的物理布局宽度610。这样的实现允许tgsf晶体管300适应在常规间距参数内(例如,在标准2

×

2cis像素布局的典型物理设计参数内),包括为光电传感器块110留出所需面积,并允许在可以符合cis像素的常规制造工艺的位置上放置漏极触点704、源极触点706和栅极触点702。根据其他cis光电传感器块设计、其他制造工艺限制等,其他实现可以使用其他合适的物理布局尺寸。

[0062]

即使在电流通道的物理布局宽度610和物理布局通道长度与常规的cis光电传感器块中使用的常规的平面源极跟随器晶体管相似的实现中,埋沟式电流通道320也可以为电流通道提供明显更大的有效有源宽度。例如,在沟槽栅340的每一侧上的埋沟式电流通道320的深度可以被有效地看作是在沟槽栅340的那一侧上的电流通道的有源宽度,并且沟槽

栅340的多侧(例如,根据图3a-3d的规定,基本上定向在z-y平面中的至少两侧)有效地形成多个这样的通道。

[0063]

因此,从操作电磁角度来看,形成具有至少物理布局宽度610(w)的深度的埋沟式电流通道320可以产生物理布局宽度610的至少两倍的有效有源电流通道宽度。可以证明,源极跟随器晶体管的跨导(gm)与w与l的比(即,w除以l)成正比。因此,l相同w的有效增加(例如,2w/l)可以产生晶体管跨导的正比例增加(例如,2*gm)。例如,源极跟随器晶体管的跨导关系可以描述如下:

[0064][0065]

如上所述,gm是跨导,w是有源区域宽度(或有效有源电流通道宽度,如在tgsf晶体管300中),l是电流通道长度(lg是栅极长度,对应于l),id是漏极电流(即,本质上是晶体管的输出)。其他参数,例如c

ox

(氧化物电容)、μ

eff

(有效增益)、m(体系数)和g

ox

(氧化物厚度)往往相对恒定,并取决于制造工艺和其他此类特性。从该关系可以看出,跨导与源极跟随器晶体管的w与l之比成正比例关系(即,无论是传统的平面源极跟随器晶体管,还是新型tgsf晶体管300)。因此,相对于l增加w(例如,标称上使w加倍)提供了许多特征。

[0066]

一项这样的特征与帧率有关。上述关系表明g

m2

与(w/lg*g

ox

)项在恒定电流下成线性比例。至少由于这种关系,跨导往往有助于cis中的像素支持的最大帧率。因此,通过用tgsf晶体管300构建cis像素来增加w/l比通常可以支持更高帧率的图像采集。另一项这样的特征与功耗有关。上述关系表明g

m2

与漏极电流和w/l比的乘积成线性比例。因此,通过增加w/l比,可以用更低电流实现相同的跨导,从而用更低的功耗实现相同的跨导。例如,如果w/l在上述关系中翻倍(即,为2w/l),则可以用一半的漏极电流实现相同的g

m2

。有效有源电流通道宽度的增加可以产生许多其他特征,例如与噪声性能相关的特征。

[0067]

图8示出了根据本文中描述的各种实施例的用于制造tgsf晶体管300的说明性方法800的流程图。方法800的实施例开始于阶段804,在半导体衬底中形成埋沟式电流通道。埋沟式电流通道形成为植入到沟槽壁中的半导体衬底中的连续掺杂区域,沟槽壁围绕蚀刻到半导体衬底中的沟槽。短语“连续掺杂区域”旨在表示埋沟式电流通道在电气上充当围绕沟槽的单个掺杂区域,即使植入埋沟式电流通道可能涉及在多个方向上和/或以多个角度植入的多个步骤。

[0068]

如本文所述,一些实施例使用蚀刻优先方法。例如,实施例可以通过以下步骤在阶段804中形成埋沟式电流通道:根据预定的沟槽几何形状,在半导体衬底的表面中刻蚀沟槽,以形成沟槽壁;以及在刻蚀之后,在沟槽壁中植入一个或多个掺杂区域,以形成连续掺杂区域,从而形成埋沟式电流通道。其他实施例可以使用植入优先方法。例如,实施例可以通过以下步骤形成埋沟式电流通道:在半导体衬底的表面下方植入掺杂阱,以占据包含沟槽的体积和连续掺杂区域的体积;以及在半导体衬底的表面中和掺杂阱中刻蚀沟槽,使得围绕沟槽形成的沟槽壁将掺杂阱的一部分限定为植入在沟槽壁中的连续掺杂区域,从而形成埋沟式电流通道。

[0069]

一些实施例开始于阶段802,在半导体衬底上沉积硬掩膜。硬掩膜暴露了表面的具有预定的物理沟槽宽度和预定的物理沟槽长度的区域。在这样的实施例中,沟槽通过硬掩

膜刻蚀到半导体衬底中(例如,在植入连续掺杂区域之前或之后),使得沟槽壁和表面水平与预定的物理沟槽宽度、预定的物理沟槽长度和预定的物理沟槽深度基本一致。

[0070]

在阶段808,实施例可以沉积多晶硅以满溢沟槽的体积,使得多晶硅的第一部分与沟槽的体积一致,以形成沟槽栅的埋入部分,并且多晶硅的第二部分在沟槽的表面水平上延伸,表面水平与半导体衬底的表面重合。在阶段812,实施例可以将多晶硅的第二部分图案化,以形成沟槽栅的暴露部分。一些实施例包括在阶段808的沉积所述多晶硅之前,在阶段806生长栅氧化层,以涂覆半导体衬底的表面并且涂覆沟槽壁。在这样的实施例中,在阶段808中被多晶硅填满的沟槽的体积为与涂覆沟槽壁的栅氧化层的厚度有关的涂覆的体积。

[0071]

在一些实施例中,多晶硅的第二部分在沟槽的表面水平上延伸了超过预定的栅极高度的量。例如,多晶硅层沉积在半导体衬底的表面(例如,或表面的区域)上,包括沉积入沟槽中。因为沟槽的底表面低于半导体衬底的周围表面,所以沟槽正上方的多晶硅层的上表面自然可以低于沟槽的周围区域(例如,低了对应于沟槽深度的量)。为了确保沟槽正上方的多晶硅层的高度处于至少预定的栅极高度(相对于沟槽的表面水平,这也是半导体衬底的周围表面的水平),多晶硅层可能必须沉积到至少沟槽深度加上预定的栅极高度的厚度。这可以在图4g中看到。在一些这样的实施例中,阶段812处的将第二部分图案化包括对多晶硅的第二部分进行抛光,以在沟槽的表面水平上的预定的栅极高度处基本形成沟槽栅的顶表面。这可以在图4h中看到。在一些这样的实施例中,阶段812处的将第二部分图案化还包括:在顶表面上沉积栅极掩模,以遮掩与沟槽栅的布局宽度和布局长度对应的区域;以及在栅极掩模周围刻蚀多晶硅的第二部分,以将沟槽栅的暴露部分图案化。这可以在图4i和4j中看到。在一些实施例中,沟槽被刻蚀为具有沟槽长度和沟槽宽度;以及阶段812处的图案化形成沟槽栅的暴露部分,以具有与沟槽长度重合的栅极布局长度和超过沟槽宽度的栅极布局宽度。这可以在图4j中看到。

[0072]

在阶段816,实施例可以在与沟槽栅的第一侧相邻的半导体衬底中植入漏极区域。在阶段820,实施例可以在与沟槽栅的第二侧相邻的半导体衬底中植入源极区域,第二侧与第一侧相对。在一些实施例中,植入漏极区域包括:植入第一较轻掺杂区域,以与埋沟式电流通道的在沟槽栅的第一侧处的一部分电耦合;以及在第一较轻掺杂区域内植入第一较高掺杂区域。在一些实施例中,植入源极区域包括:植入第二较轻掺杂区域,以与埋沟式电流通道的在沟槽栅的第二侧处的一部分电耦合;以及在第二较轻掺杂区域内植入第二较高掺杂区域。

[0073]

在一些实施例中,在阶段824处,方法800可以包括:将栅极触点图案化以与沟槽栅电耦合,将漏极触点图案化以与漏极区域电耦合,并且将源极触点图像化以与源极区域电耦合。如本文所述,电激活栅极触点激活埋沟式电流通道,以在沟槽栅的埋入部分周围提供漏极触点和源极触点之间的电流流动。例如,当通道有源时,电流主要在沟槽栅的埋入部分的两个长度向侧周围流动。围绕沟槽栅的多个平行电流路径和沟槽的深度尺寸可以增加电流通道的有效有源宽度。

[0074]

应理解,当元件或组件在本文中被称为“连接到”或“耦合到”另一元件或组件时,其可以连接或耦合到另一元件或组件,或者也可以存在介于中间的元件或组件。相反,当元件或组件被称为“直接连接到”或“直接耦合到”另一元件或组件时,它们之间不存在介于中

间的元件或组件。应理解,尽管可以使用本文中的术语“第一”、“第二”、“第三”等描述各种元件、组件,但是这些元件、组件、区域不应受这些术语的限制。这些术语仅用于将一个元件,组件与另一个元件,组件区分开。因此,在不脱离本发明的教导的情况下,以下讨论的第一元件,组件可以被称为第二元件,组件。如本文中使用的,术语“逻辑低”、“低状态”、“低电平”、“逻辑低电平”、“低”或“0”可互换使用。术语“逻辑高”、“高状态”、“高电平”、“逻辑高电平”、“高”或“1”可互换使用。

[0075]

如本文中使用的,术语“一”、“一个”和“该”可以包括单数和复数引用。将进一步理解,当本说明书中使用术语“包括”、“包含”、“具有”及其变型时,说明存在所述特征、步骤、操作、元件和/或组件,但不排除存在或添加一个或多个其他特征、步骤、操作、元件、组件和/或其组合。相反,当本说明书中使用术语“由......组成”时,说明所述特征、步骤、操作、元件和/或组件,并且排除附加特征、步骤、操作、元件和/或组件。此外,如本文中使用的,词语“和/或”可以指代并涵盖相关联的所列项目中的一个或多个项目的任何可能的组合。

[0076]

虽然本文中参考说明性实施例描述了本发明,但是该描述并不旨在以限制意义来解释。相反,说明性实施例的目的是使本发明的精神更好地被本领域技术人员理解。为了不模糊本发明的范围,省略了众所周知的过程和制造技术的许多细节。参考该描述,说明性实施例的各种修改以及其他实施例对本领域技术人员来说是显而易见的。因此,所附权利要求旨在涵盖任何这样的修改。

[0077]

此外,可以有利地使用本发明的优选实施例的一些特征而无需相应地使用其他特征。因此,前述描述应该被认为仅仅是对本发明原理的说明,而不是对其的限制。本领域技术人员将理解落入本发明范围内的上述实施例的变型。因此,本发明不限于以上讨论的特定实施例和图示,而是由所附权利要求及其等同物限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1