电感器和包括电感器的半导体封装件的制作方法

电感器和包括电感器的半导体封装件

1.本技术基于2021年8月24日在韩国知识产权局提交的第10-2021-0111867号韩国专利申请并要求其优先权,该韩国专利申请的公开内容通过引用被完全包含于此。

技术领域

2.发明构思涉及一种电感器和包括电感器的半导体封装件,更具体地,涉及一种具有螺旋引线的电感器和包括该电感器的半导体封装件。

背景技术:

3.近来,随着半导体封装件制造技术和无线通信技术的改进,在半导体封装件中应用了构造通信电路的技术。例如,正在开发将具有不同特性的半导体芯片组成一个封装件的系统级封装(system in package,sip)技术。当实施这种封装件时,电感器被视为非常重要的组件。特别地,为了构造通信电路,期望一种能够表现高质量的螺旋电感器(spiral inductor)。

技术实现要素:

4.发明构思涉及一种使用简单制造工艺实施并具有高可靠性的牢固的螺旋电感器。

5.发明构思涉及一种包括使用简单制造工艺实施并具有高可靠性的牢固的螺旋电感器的半导体封装件。

6.发明构思将要解决的问题不限于上述一种,并且本领域技术人员将从下面的描述中清楚地理解其它目的。

7.根据本发明的实施例,一种电感器包括:半导体基底,设置有包括第一布线层和第二布线层的多个布线层;直导线,位于半导体基底的第一布线层处,具有第一端;螺旋图案的导电线圈,在第一布线层上方位于第二布线层处,具有第二端;以及导电过孔,将直导线的第一端竖直连接到导电线圈的第二端。当在平面图中观看时,多个虚设图案布置在由螺旋图案的最内匝限定的第一区域中。

8.根据本发明的实施例,一种半导体封装件包括:封装基底;中介体,布置在封装基底上;第一半导体芯片和第二半导体芯片,布置在中介体上;第一电感器,形成在第一半导体芯片中;以及第二电感器,形成在中介体中。第一电感器和第二电感器中的每个包括:直导线,位于第一布线层处,具有第一端;方形螺旋图案的导电线圈,位于与第一布线层竖直间隔开的第二布线层处,具有第二端;以及导电过孔,将直导线的第一端竖直连接到导电线圈的第二端。当在平面图中观看时,多个岛状虚设图案布置在由方形螺旋图案的最内匝限定的第一区域中。

9.根据本发明的实施例,一种半导体封装件包括:封装基底;中介体,布置在封装基底上;第一半导体芯片和第二半导体芯片,布置在中介体上;电感器,形成在第一半导体芯片中;模制构件,围绕第一半导体芯片和第二半导体芯片;散热构件,布置在模制构件上;以及封装件,围绕中介体、模制构件和散热构件。电感器包括:直导线,位于第一布线层处,具

有第一端;方形螺旋图案的导电线圈,位于与第一布线层竖直间隔开的第二布线层处,具有第二端;以及导电过孔,将直导线的第一端竖直连接到导电线圈的第二端。当在平面图中观看时,具有不同形状的多个虚设图案布置在由方形螺旋图案的最内匝限定的第一区域中。

附图说明

10.根据下面结合附图的详细描述,将更清楚地理解发明构思的实施例,在附图中:

11.图1a是示出根据发明构思的实施例的半导体封装件的剖视图;

12.图1b是示出图1a的半导体封装件的平面图;

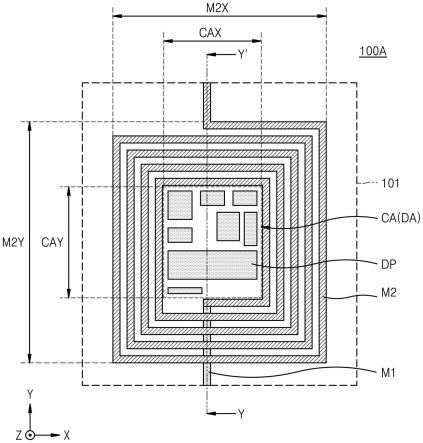

13.图1c是示出根据发明构思的实施例的图1b中的电感器的放大的平面图;

14.图1d是示出沿着图1c的线y-y'截取的电感器的剖视图;

15.图2a和图2b以及图3a和图3b是示出根据发明构思的实施例的电感器的视图;

16.图4a是示出根据发明构思的实施例的半导体封装件的剖视图;

17.图4b是示出根据发明构思的实施例的图4a中的第一电感器和第二电感器的放大的平面图;

18.图4c是示出沿着图4b的线y-y'截取的第一电感器的剖视图;

19.图4d是示出沿着图4b的线y-y'截取的第二电感器的剖视图;

20.图5是示出根据发明构思的实施例的制造电感器的方法的流程图;

21.图6a、图7a、图8a、图9a和图10a是根据发明构思的实施例的按工艺顺序示出的制造电感器的方法的平面图;

22.图6b、图7b、图8b、图9b和图10b是沿着图6a、图7a、图8a、图9a和图10a的线y-y'截取的剖视图;

23.图11是示出根据发明构思的实施例的包括半导体封装件的电子装置的框图;以及

24.图12是示出根据发明构思的实施例的半导体封装件的构造的框图。

具体实施方式

25.在下文中,将参照附图详细地描述发明构思的实施例。

26.图1a是示出根据发明构思的实施例的半导体封装件10的剖视图。图1b是示出图1a的半导体封装件10的平面图。图1c是示出根据发明构思的实施例的图1b中的电感器的放大的平面图。图1d是示出沿着图1c的线y-y'截取的电感器的剖视图。

27.在当前说明书中,与x轴平行的方向和与y轴平行方向分别被称为第一水平方向和第二水平方向,与z轴平行的方向被称为竖直方向。

28.通过沿x轴延伸的线和沿y轴延伸的线限定的表面可以被称为平面,相对于另一组件在+z方向上布置的组件可以被称为在所述组件上面,而相对于另一组件在-z方向上布置的组件可以被称为在所述组件下面。

29.组件的区域可以指在与所述平面平行的表面中被所述组件占据的尺寸。将理解的是,当元件被称为“连接”或“结合”到另一元件或者“在”另一元件“上”时,它可以直接连接或结合到所述另一元件或者在所述另一元件上,或者可以存在中间元件(居间元件)。相反,当元件被称为“直接连接”或“直接结合”到另一元件或者被称为“接触”或“触及”另一元件时,在接触点处不存在中间元件。

30.在当前说明书的附图中,为了方便,可以仅示出部分层。包括导电材料的图案(诸如金属层的图案)可以被称为导电图案,或者可以被简单地称为图案。

31.参照图1a至图1d,示出了包括第一半导体芯片100、第二半导体芯片200、中介体300和封装基底400的半导体封装件10。

32.第一半导体芯片100可以包括逻辑芯片。逻辑芯片可以包括多个逻辑元件(即,逻辑单元)(未示出)。此外,逻辑芯片可以包括pci express接口。逻辑元件可以包括例如逻辑电路(诸如and逻辑、or逻辑、not逻辑)和触发器,并且可以执行各种信号处理。在一些实施例中,逻辑元件可以执行信号处理,诸如模拟信号处理和模数(a/d)转换控制。如这里使用的,术语“逻辑单元”可以指被配置为执行单个逻辑运算并且由多个互连mosfet组成的单位电路。逻辑单元的示例包括nand门、nor门、反相器和锁存器。此外,将清楚的是,发明不限于一个或多个逻辑单元,而是可以结合一个或更多个晶体管、晶体管的一部分、集成电路(例如,包括多个互连逻辑单元的集成电路)、半导体芯片、多个半导体芯片(例如,堆叠在封装件中的多个半导体芯片)等来实施。

33.逻辑芯片可以根据其功能通过微处理器、图形处理器、信号处理器、网络处理器、芯片组、音频编解码器、视频编解码器、应用处理器或者片上系统(soc)来实施。如稍后详细地描述的,第一半导体芯片100可以包括其中布置有通信装置的通信电路101,并且电感器100a可以布置在通信电路101中。

34.第二半导体芯片200可以包括易失性存储器芯片和/或非易失性存储器芯片。易失性存储器芯片可以是例如动态随机存取存储器(dram)、静态ram(sram)或晶闸管ram(tram)。非易失性存储器芯片可以是例如闪存、磁ram(mram)、自旋转移力矩mram(stt-mram)、铁电ram(fram)、相变ram(pram)或电阻ram(rram)。在一些实施例中,第二半导体芯片200可以包括存储器芯片组,该存储器芯片组包括其数据项可以彼此合并的多个存储器芯片。第二半导体芯片200可以包括高带宽存储器(hbm)。

35.中介体300可以布置在第一半导体芯片100和第二半导体芯片200下方,并且可以通过第一凸块结构150和第二凸块结构250将第一半导体芯片100和第二半导体芯片200彼此电连接。在一些实施例中,中介体300可以是或者包括硅(si)基底,并且可以包括布置在si基底下方的再分布结构300r。中介体300可以包括布置在再分布结构300r下方的内部连接端子350以及电连接到再分布结构300r并穿过si基底的贯穿电极330。

36.封装基底400可以布置在中介体300下方,并且可以基于印刷电路板(pcb)、晶圆基底、陶瓷基底或玻璃基底来形成。在根据发明构思的半导体封装件10中,封装基底400可以是pcb。封装基底400可以包括布置在其底表面中的凸块焊盘410以及连接到凸块焊盘410的底部的外部连接端子450。半导体封装件10可以通过外部连接端子450电连接到电子产品的模块基底或系统板并且安装在电子产品的模块基底或系统板上。

37.第一半导体芯片100和第二半导体芯片200可以在第一水平方向(x方向)上并排地安装在中介体300上。根据发明构思的半导体封装件10可以包括围绕第一半导体芯片100和第二半导体芯片200的模制构件420以及在模制构件420上接触第一半导体芯片100和第二半导体芯片200的散热构件430。根据发明构思的半导体封装件10可以包括在封装基底400上围绕中介体300、模制构件420和散热构件430的封装件440。

38.如上面描述的,在根据发明构思的半导体封装件10中,电感器100a可以布置在第

一半导体芯片100的通信电路101中。例如,通信电路101可以包括pci express接口。然而,发明构思不限于此。这里,下面详细描述在第一半导体芯片100的其中布置有电感器100a的部分中的组件。

39.作为晶圆的半导体基底110可以包括彼此面对的有效表面和无效表面。半导体基底110可以是例如包括晶体硅、多晶硅或非晶硅的si晶圆。可选地,半导体基底110可以包括诸如锗(ge)的半导体元素或诸如碳化硅(sic)、砷化镓(gaas)、砷化铟(inas)和磷化铟(inp)的化合物半导体,或者可以由诸如锗(ge)的半导体元素或诸如碳化硅(sic)、砷化镓(gaas)、砷化铟(inas)和磷化铟(inp)的化合物半导体形成。

40.另一方面,半导体基底110可以具有绝缘体上硅(soi)结构。例如,半导体基底110可以包括掩埋氧化物(box)层。在一些实施例中,半导体基底110可以包括导电区域(例如,掺杂有杂质的阱或掺杂有杂质的结构)。半导体基底110可以具有各种隔离结构中的一种,诸如浅沟槽隔离(sti)结构。

41.金属间电介质(imd)层111可以布置在半导体基底110的有效表面上。imd层111可以包括例如氧化硅、氮化硅、氮氧化硅、低介电常数材料、超低介电常数材料或上述材料的组合或者可以由例如氧化硅、氮化硅、氮氧化硅、低介电常数材料、超低介电常数材料或上述材料的组合形成。然而,发明构思不限于此。

42.多个虚设电容器图案cp可以布置在imd层111上。在一些实施例中,逻辑芯片可以包括使用金属作为电极层的金属-绝缘体-金属(mim)电容器(未示出)。mim电容器具有其中电介质层布置在上金属电极层与下金属电极层之间的结构。在除了其中布置有mim电容器的区域之外的部分区域中,可以布置多个虚设电容器图案cp。

43.下绝缘层113可以布置在imd层111上,以覆盖多个虚设电容器图案cp。下绝缘层113可以是例如磷硅酸盐玻璃(psg)、硼磷硅酸盐玻璃(bpsg)、未掺杂硅酸盐玻璃(usg)、原硅酸四乙酯(teos)、等离子体增强teos(pe-teos)、高密度等离子体化学气相沉积(hdp-cvd)氧化物或者诸如用于后段制程(back-end of line,beol)的低介电常数材料和超低介电常数材料的氧化物。

44.导线m1和多个虚设图案dp可以布置在下绝缘层113上。其处布置有导线m1和多个虚设图案dp的层可以被称为第一布线层lv1。导线m1的厚度可以等于多个虚设图案dp的厚度。导线m1和多个虚设图案dp可以包括彼此相同的材料或者可以由彼此相同的材料形成。导线m1和多个虚设图案dp可以包括例如钛(ti)、氮化钛(tin)、钽(ta)、tan、钨(w)、铜(cu)、铝(al)、上述材料的混合物或上述材料的化合物或者由例如钛(ti)、氮化钛(tin)、钽(ta)、tan、钨(w)、铜(cu)、铝(al)、上述材料的混合物或上述材料的化合物形成。然而,发明构思不限于此。在根据发明构思的电感器100a中,导线m1和多个虚设图案dp可以包括cu或者可以由cu形成。

45.层间电介质(ild)115可以布置在下绝缘层113上以围绕导线m1和多个虚设图案dp。ild 115的顶表面可以在与导线m1的顶表面和多个虚设图案dp的顶表面相同的平面上。ild 115可以是例如psg、bpsg、usg、teos、pe-teos、hdp-cvd氧化物或者诸如用于beol的低介电常数材料和超低介电常数材料的氧化物。然而,发明构思不限于此。

46.多层绝缘层120可以布置为覆盖导线m1的顶表面、多个虚设图案dp的顶表面和ild 115的顶表面。多层绝缘层120可以包括下第一绝缘层121和上第二绝缘层123。下第一绝缘

层121可以包括sicn或者可以由sicn形成,上第二绝缘层123可以包括sin或者可以由sin形成。在一些实施例中,下第一绝缘层121的绝缘材料可以不同于下绝缘层113的绝缘材料。

47.上绝缘层131可以布置为覆盖多层绝缘层120。上绝缘层131可以是例如psg、bpsg、usg、teos、pe-teos、hdp-cvd氧化物或者诸如用于beol的低介电常数材料和超低介电常数材料的氧化物。然而,发明构思不限于此。

48.导电过孔v1可以布置为穿过上绝缘层131和多层绝缘层120并且接触导线m1的第一端m1e。在图1d中,导电过孔v1被示出为单个。然而,导电过孔v1可以设置为多个。由于首先干法蚀刻其中将布置导电过孔v1的开口的图案化工艺的特性,导电过孔v1不会具有竖直侧壁而可以是锥形的倒梯形形状,使得导电过孔v1的宽度在竖直方向(z方向)上向下减小。

49.导电过孔v1可以包括导电材料或者可以由导电材料形成,例如,ti、tin、ta、tan、w、cu、al、上述材料的混合物或上述材料的化合物。然而,发明构思不限于此。在一些实施例中,导电过孔v1和导线m1可以包括彼此不同的材料或者可以由彼此不同的材料形成。在根据发明构思的电感器100a中,导电过孔v1可以包括al或者可以由al形成。

50.导电线圈m2可以布置在上绝缘层131上。其处布置导电线圈m2的层可以被称为第二布线层lv2。导电线圈m2的第二端m2e可以布置为接触导电过孔v1。由于首先形成金属布线并干法蚀刻所述金属布线的图案化工艺的特性,导电线圈m2不会具有竖直侧壁而可以是锥形的梯形形状,使得导电线圈m2的宽度在竖直方向(z方向)上向下增大。

51.导电线圈m2可以包括导电材料或者可以由导电材料形成,例如,ti、tin、ta、tan、w、cu、al、上述材料的混合物或上述材料的化合物。然而,发明构思不限于此。在一些实施例中,导电线圈m2和导电过孔v1可以包括彼此相同的材料或者可以由彼此相同的材料形成。在根据发明构思的电感器100a中,导电线圈m2可以包括al或者可以由al形成。

52.覆盖绝缘层133可以布置在上绝缘层131上以覆盖导电线圈m2。覆盖绝缘层133可以沿着导电线圈m2的弯曲顶表面共形地布置。覆盖绝缘层133可以是例如psg、bpsg、usg、teos、pe-teos、hdp-cvd氧化物或者诸如用于beol的低介电常数材料和超低介电常数材料的氧化物。然而,发明构思不限于此。

53.如上面描述的,根据发明构思的电感器100a可以位于两个布线层lv1和lv2处。例如,在包括多个布线层的半导体基底110上,可以设置布置在第一布线层lv1处的导线m1、在第一布线层lv1上方布置在第二布线层lv2处的导电线圈m2以及在竖直方向(z方向)上将导线m1连接到导电线圈m2的导电过孔v1。

54.导线m1可以是直线形状的,导电过孔v1可以接触直线形状的第一端m1e。导电线圈m2可以具有方形螺旋图案,并且可以包括作为方形螺旋图案的最内起始部分的螺旋引线。在一些实施例中,导电过孔v1可以接触螺旋引线(即,导电线圈m2)的第二端m2e。然而,本发明不限于此。在一些实施例中,导电线圈m2可以具有任意螺旋图案,诸如圆形螺旋图案。螺旋图案可以包括多个螺旋匝。最内螺旋匝可以限定第一区域,第一区域可以被称为中心区域ca,这将在后面描述。两个相邻的螺旋匝可以以预定距离彼此间隔开。在一些实施例中,两个相邻的螺旋匝之间的距离在整个螺旋图案中可以是恒定的。在一些实施例中,两个相邻的螺旋匝之间的距离可以不同于另外两个相邻的螺旋匝之间的距离。

55.在一些实施例中,导电线圈m2的方形螺旋图案可以布置为围绕中心区域ca,该中心区域ca的中心为空的空间。在中心区域ca中,可以不设置方形螺旋图案。第一布线层lv1

的与第二布线层lv2的中心区域ca对应的区域可以被称为虚设区域da。

56.在根据发明构思的电感器100a中,多个虚设图案dp可以布置在虚设区域da中。中心区域ca和多个虚设图案dp可以在竖直方向(z方向)上叠置,而导电线圈m2和多个虚设图案dp在竖直方向(z方向)上可以不叠置。

57.当在平面图中观看时,多个虚设图案dp的面积与虚设区域da的面积的比率为约40%至约90%。虚设区域da中的被多个虚设图案dp占据的区域可以使得应力不会集中在一个位置(例如,导线m1)上而是可以分散到多个虚设图案dp中。诸如“约(大约)”或“近似”的术语可以反映仅以小的相对方式并且/或者以不显著改变某些元件的操作、功能或结构的方式变化的量、尺寸、取向或布局。例如,“约0.1至约1”的范围可以涵盖诸如0.1周围的0%至5%偏差以及1周围的0%至5%偏差的范围,特别是在这种偏差与所列出的范围保持相同效果时。

58.多个虚设图案dp中的每个可以是被作为绝缘材料的下绝缘层113、ild115和多层绝缘层120围绕的同时浮置(即,电浮置)的岛的形式。在一些实施例中,每个虚设图案可以被至少两种不同的绝缘材料围绕。例如,ild 115可以是例如psg、bpsg、usg、teos、pe-teos、hdp-cvd氧化物或者诸如用于beol的低介电常数材料和超低介电常数材料的氧化物;下绝缘层113可以是例如磷硅酸盐玻璃(psg)、硼磷硅酸盐玻璃(bpsg)、未掺杂硅酸盐玻璃(usg)、原硅酸四乙酯(teos)、等离子体增强teos(pe-teos)、高密度等离子体化学气相沉积(hdp-cvd)氧化物或者诸如用于后段制程(beol)的低介电常数材料和超低介电常数材料的氧化物;下第一绝缘层121可以包括碳氮化硅(sicn)或者可以由碳氮化硅(sicn)形成,而上第二绝缘层123可以包括氮化硅(sin)或者可以由氮化硅(sin)形成。多个虚设图案dp可以具有至少两种不同的形状。然而,发明构思不限于此。多个虚设图案dp中的至少一些可以具有彼此相同的形状。在一些实施例中,多个虚设图案dp在面积上可以具有至少两种不同的尺寸。然而,发明构思不限于此。

59.在根据发明构思的电感器100a中,导电线圈m2在第一水平方向(x方向)上的长度m2x可以为约45μm至约55μm,而导电线圈m2在第二水平方向(y方向)上的长度m2y可以为约65μm至约75μm。例如,导电线圈m2可以是矩形的。中心区域ca在第一水平方向(x方向)上的长度cax可以为约15μm至约20μm,而中心区域ca在第二水平方向(y方向)上的长度cay可以为约30μm至约40μm。然而,根据发明构思的电感器100a不限于上述数值。虚设区域da的长度可以等于中心区域ca的长度。

60.近来,随着半导体封装件制造技术和无线通信技术的改进,在半导体封装件中应用了构造通信电路的技术。例如,正在开发将具有不同特性的半导体芯片组成一个封装件的sip技术。当实施这种封装件时,电感器被视为非常重要的组件。针对通信电路,期望一种能够表现高质量的螺旋电感器。

61.使用了通过将电感器100a构造为包括在竖直方向(z方向)上将第一布线层lv1处的导线m1连接到第二布线层lv2处的导电线圈m2的导电过孔v1来减小半导体基底110中的电感器100a的面积的技术。应力会集中在第一布线层lv1处的导线m1上,并且由于分层现象(delamination phenomenon)而会在布置在导线m1上的多层绝缘层120中产生裂纹。

62.为了解决这种问题,包括在根据发明构思的半导体封装件10中的电感器100a可以包括布置在导线m1周围的多个虚设图案dp。集中在导线m1上的应力分散到多个虚设图案dp

中,使得可以有效地抑制裂缝的产生。因为多个虚设图案dp可以在形成导线m1的工艺中形成而无需附加工艺,所以可以原样使用现有工艺。在一些实施例中,可以使用相同的工艺形成导线m1和多个虚设图案dp。

63.结果,根据发明构思的半导体封装件10具有高可靠性和高生产效率以及以较低制造成本的简单且牢固的制造工艺。

64.图2a至图3b是示出根据发明构思的实施例的电感器100b和电感器100c的视图。

65.构造下文中描述的电感器100b和电感器100c的大多数组件以及形成所述组件的材料与参照图1a至图1d描述的那些相同或相似。主要基于电感器100a与电感器100b和电感器100c之间的差异给出描述。

66.参照图2a和图2b,电感器100b包括在第一布线层lv1处的导线m1和两个虚设图案dp2、在第二布线层lv2处的导电线圈m2以及在竖直方向(z方向)上将导线m1连接到导电线圈m2的导电过孔v1。

67.在根据发明构思的电感器100b中,两个虚设图案dp2可以布置在虚设区域da中。中心区域ca和两个虚设图案dp2在竖直方向(z方向)上叠置,并且导电线圈m2和两个虚设图案dp2在竖直方向(z方向)上可以不叠置。

68.当在平面图中观看时,两个虚设图案dp2的面积与虚设区域da的面积的比率可以不小于约50%。占据在虚设区域da中的两个虚设图案dp2的区域可以使得应力在虚设区域da中不会集中在一个位置上而是可以分散到两个虚设图案dp2中。

69.两个虚设图案dp2中的每个可以是被作为绝缘材料的下绝缘层113、ild115和多层绝缘层120围绕的同时浮置的岛的形式。两个虚设图案dp2可以具有彼此相同的形状。然而,发明构思不限于此。在一些实施例中,两个虚设图案dp2可以具有彼此不同的形状。

70.参照图3a和图3b,电感器100c包括在第一布线层lv1处的延伸导线m1'、在第二布线层lv2处的导电线圈m2以及在竖直方向(z方向)上将延伸导线m1'连接到导电线圈m2的导电过孔v1。

71.在根据发明构思的电感器100c中,延伸导线m1'可以是直线形状的并且导电过孔v1可以接触不是直线的端部的部分。在一些实施例中,延伸导线m1'可以在第二水平方向(y方向)上延伸到虚设区域da。

72.在一些实施例中,多个虚设图案dp以及延伸导线m1'的一部分可以布置在虚设区域da中。中心区域ca、多个虚设图案dp以及延伸导线m1'的一部分可以在竖直方向(z方向)上叠置。导电线圈m2和多个虚设图案dp在竖直方向(z方向)上可以不叠置。

73.当在平面图中观看时,多个虚设图案dp以及延伸导线m1'的一部分的面积与虚设区da的面积的比率可以为约40%至约90%。多个虚设图案dp以及延伸导线m1'的一部分可以布置在虚设区域da的显著部分中。在虚设区域da中,应力不会集中在一个位置上而是可以分散到多个虚设图案dp和延伸导线m1'中。

74.图4a是示出根据发明构思的实施例的半导体封装件20的剖视图。图4b是示出根据发明构思的实施例的图4a中的第一电感器100d和第二电感器100e的放大的平面图。图4c是示出沿着图4b的线y-y'截取的第一电感器100d的剖视图。图4d是示出沿着图4b的线y-y'截取的第二电感器100e的剖视图。

75.在图4b中,一起示出了第一电感器100d和第二电感器100e。在一些实施例中,第一

电感器100d和第二电感器100e可以在构造和尺寸上彼此相同。在图4c中,第一电感器100d被示出为面对中介体301。在图4d中,第二电感器100e被示出为面对第一半导体芯片100。

76.构成后文中描述的半导体封装件20的大多数组件和形成所述组件的材料与参照图1a至图1d描述的那些相同或相似。主要基于半导体封装件10与半导体封装件20之间的差异给出描述。

77.参照图4a至图4d,半导体封装件20包括第一半导体芯片100、第二半导体芯片200、中介体301和封装基底400。

78.在根据发明构思的半导体封装件20中,中介体301可以布置在第一半导体芯片100和第二半导体芯片200下方,并且可以将第一半导体芯片100和第二半导体芯片200彼此电连接。在一些实施例中,中介体301可以是或者包括si基底,并且可以包括布置在si基底下方的第一再分布结构301r1以及布置在si基底上的第二再分布结构301r2。中介体301可以包括布置在第一再分布结构301r1下方的内部连接端子350以及贯穿si基底将第一再分布结构301r1连接到第二再分布结构301r2的贯穿电极330。

79.在根据发明构思的半导体封装件20中,第一半导体芯片100可以包括其中布置有通信装置的通信电路101,并且第一电感器100d可以形成在通信电路101中。如上面描述的,中介体301可以在其上包括第二再分布结构301r2,并且第二电感器100e可以形成在第二再分布结构301r2中或者形成在与第二再分布结构301r2相邻的区域中。

80.第一电感器100d包括上述电感器100a(参照图1d)的所有组件。此外,第一电感器100d可以包括覆盖覆盖绝缘层133的保护层141。保护层141可以填充覆盖绝缘层133的弯曲部分并且可以具有平坦表面。保护层141可以包括例如氧化硅、氮化硅、氮氧化硅和聚合物材料中的一种或者可以由例如氧化硅、氮化硅、氮氧化硅和聚合物材料中的一种形成。在一些实施例中,聚合物材料可以是硅酮、环氧树脂、苯并环丁烯(bcb)、聚酰亚胺(pi)或聚苯并噁唑(pbo)。然而,发明构思不限于此。

81.第二电感器100e仅包括上述电感器100a(参照图1d)的一些组件。硅(si)基底310对应于半导体基底110(参照图1d),第一绝缘材料层311对应于imd层111(参照图1d),第二绝缘材料层315对应于ild 115(参照图1d),多层绝缘层320对应于多层绝缘层120(参照图1d),第三绝缘材料层331对应于上绝缘层131(参照图1d),覆盖绝缘层333对应于覆盖绝缘层133(参照图1d)。诸如“第一”、“第二”、“第三”等的序数可以简单地用作一些元件、步骤等的标签,以将这些元件、步骤等彼此区分开。在说明书中未使用“第一”、“第二”等描述的术语在权利要求中仍可以被称为“第一”或“第二”。此外,用特定序数(例如,具体的权利要求中的“第一”)指代的术语可以在其它地方用不同的序数(例如,说明书或另一权利要求中的“第二”)来描述。

82.在第二电感器100e中,可以省略多个虚设电容器图案cp(参照图1d)以及覆盖多个虚设电容器图案cp的下绝缘层113(参照图1d)。第二电感器100e可以包括覆盖覆盖绝缘层333的保护层341。保护层341可以填充覆盖绝缘层333的弯曲部分并且可以具有平坦表面。保护层341可以包括例如氧化硅、氮化硅、氮氧化硅和聚合物材料中的一种或者可以由例如氧化硅、氮化硅、氮氧化硅和聚合物材料中的一种形成。在一些实施例中,聚合物材料可以是硅树脂、环氧树脂、bcb、pi或pbo。然而,发明构思不限于此。

83.在一些实施例中,第二电感器100e可以布置在第二再分布结构301r2中。然而,第

二电感器100e可以布置在第二再分布结构301r2下方。

84.在根据发明构思的半导体封装件20中,因为第一电感器100d可以布置在第一半导体芯片100中并且第二电感器100e可以布置在中介体301中,所以与其中电感器仅布置在第一半导体芯片100中的情况相比,所述电感器的电容可以显著增大。

85.根据发明构思的半导体封装件20具有高可靠性和高生产效率以及以较低制造成本的简单且牢固的制造工艺。

86.图5是示出根据发明构思的实施例的制造电感器的方法的流程图。

87.参照图5,电感器制造方法s10可以包括第一操作s110至第七操作s170。

88.当特定实施例可以以其它方式实施时,具体工艺顺序可以与所描述的顺序不同。例如,可以同时执行或者可以与所描述的顺序相反的顺序执行两个连续工艺。

89.根据发明构思的电感器制造方法s10包括:操作s110,设置包括多个逻辑元件的半导体基底;操作s120,顺序形成imd层、多个虚设电容器图案和下绝缘层;操作s130,在下绝缘层上形成层间绝缘层以围绕导线和多个虚设图案;操作s140,顺序形成多层绝缘层和上绝缘层;操作s150,形成导电过孔以穿过上绝缘层和多层绝缘层来接触导线的端部;操作s160,在上绝缘层上形成具有方形螺旋图案的导电线圈;以及操作s170,在上绝缘层上形成覆盖绝缘层以覆盖导电线圈。

90.下面参照图6a至图10b详细地描述操作s110至操作s170的技术特征。

91.图6a、图7a、图8a、图9a和图10a是根据发明构思的实施例的按工艺顺序示出的制造电感器的方法的平面图。图6b、图7b、图8b、图9b和图10b是沿着图6a、图7a、图8a、图9a和图10a的线y-y'截取的剖视图。

92.参照图6a和图6b,设置包括多个逻辑元件的半导体基底110。

93.作为晶圆的半导体基底110可以包括彼此面对的有效表面和无效表面。可以在有效表面上形成多个逻辑元件。

94.接下来,可以在半导体基底110的有效表面上形成imd层111以覆盖多个逻辑元件。

95.接下来,可以在imd层111上形成多个虚设电容器图案cp。可以在imd层111上的除了其中布置mim电容器的区域之外的部分区域中形成多个虚设电容器图案cp。

96.接下来,可以在imd层111上形成下绝缘层113以覆盖多个虚设电容器图案cp。

97.参照图7a和图7b,在下绝缘层113上形成ild 115以围绕导线m1和多个虚设图案dp。

98.在一些实施例中,可以首先在下绝缘层113上形成ild 115,并且可以稍后通过使用镶嵌工艺(damascene)来形成导线m1和多个虚设图案dp。在其它实施例中,可以首先在下绝缘层113上形成导线m1和多个虚设图案dp并且可以稍后形成ild 115。

99.当在平面图中观看时,多个虚设图案dp的面积与虚设区域da的面积的比率为约40%至约90%。

100.参照图8a和图8b,形成多层绝缘层120以覆盖导线m1的顶表面、多个虚设图案dp的顶表面和ild 115的顶表面。

101.多层绝缘层120可以包括下第一绝缘层121和上第二绝缘层123。在一些实施例中,下第一绝缘层121可以包括碳氮化硅(sicn)或者可以由碳氮化硅(sicn)形成,而上第二绝缘层123可以包括氮化硅(sin)或者可以由氮化硅(sin)形成。

102.接下来,可以形成上绝缘层131以覆盖多层绝缘层120。

103.参照图9a和图9b,可以形成导电过孔v1以穿过上绝缘层131和多层绝缘层120来接触导线m1的第一端m1e。

104.通过光刻工艺和蚀刻工艺在上绝缘层131和多层绝缘层120中形成其中将形成导电过孔v1的开口。由于干法蚀刻的特性,开口不会具有竖直侧壁而可以是锥形的倒梯形形状,使得开口的宽度在竖直方向(z方向)上向下减小。

105.接下来,通过填充开口来形成接触导线m1的第一端m1e的导电过孔v1。在图9a和图9b中,导电过孔v1被示出为单个。然而,可以设置多个导电过孔v1。

106.参照图10a和图10b,在上绝缘层131上形成导电线圈m2。

107.导电线圈m2可以具有方形螺旋图案,同时导电线圈m2的第二端m2e接触导电过孔v1。形成金属布线,然后对金属布线进行干法蚀刻以使其图案化成导电线圈m2。由于干法蚀刻的特性,导电线圈m2不会具有竖直侧壁而可以是锥形的梯形形状,使得导电线圈m2的宽度在竖直方向(z方向)上向下增大。

108.参照图1c和图1d,可以在上绝缘层131上形成覆盖绝缘层133以覆盖导电线圈m2。可以沿着导电线圈m2的弯曲顶表面共形地布置覆盖绝缘层133。

109.通过上述方法,可以制造根据发明构思的电感器100a。根据发明构思的半导体封装件10(包括如上面描述制造的电感器100a)具有高可靠性和高生产效率以及以较低制造成本的简单且牢固的制造工艺。

110.图11是示出根据发明构思的实施例的包括半导体封装件的电子装置1000的框图。

111.参照图11,电子装置1000容纳主板1010。芯片相关组件1020(或称为芯片组)、网络相关组件1030和其它组件1040可以物理和/或电性连接到主板1010。它们与下面将描述的其它电子组件组合(结合)并且形成各种信号线1090。

112.芯片相关组件1020可以包括存储器芯片(诸如易失性存储器、非易失性存储器和闪存)、应用处理器芯片(诸如中央处理器、图形处理器、数字信号处理器、加密处理器、微处理器和微控制器)以及逻辑芯片(诸如模数转换器(adc)和专用集成芯片(asic))。其它芯片相关电子组件可以包括在芯片相关组件1020中。芯片相关组件1020可以彼此组合。

113.网络相关组件1030(或称为网络)可以包括wifi(ieee802.11族)、wimax(ieee802.16族)、ieee802.20、长期演进(lte)、ev-do、hspa+、hsdpa+、hsupa+、edge、gsm、gps、gprs、cdma、tdma、dect、蓝牙、3g、4g、5g以及被指定为遵循上述协议的其它任意有线和无线协议。多个其它有线和无线标准或协议可以包括在网络相关组件1030中。网络相关组件1030可以与芯片相关组件1020组合。

114.其它组件1040可以包括高频电感器、铁氧体电感器、功率电感器、铁氧体珠、低温共烧陶瓷(ltcc)、电磁干扰(emi)滤波器或多层陶瓷电容器(mlcc)。用于各种目的的其它无源组件可以包括在其它组件1040中。其它组件1040可以与芯片相关组件1020和/或网络相关组件1030组合。

115.根据电子装置1000的种类,电子装置1000可以包括其它电子组件,其它电子组件可以物理和/或电性连接到或者不连接到主板1010。其它电子组件可以包括例如相机1050、天线1060、显示器1070、电池1080、音频编解码器(未示出)、视频编解码器(未示出)、功率放大器(未示出)、罗盘(未示出)、加速度计(未示出)、陀螺仪(未示出)、扬声器(未示出)、大容

量存储装置(未示出)、光盘(cd)(未示出)和数字通用光盘(dvd)(未示出)。根据电子装置1000的种类,可以包括用于各种目的的其它电子组件。

116.电子装置1000可以包括智能电话、个人数字助理、数字视频相机、数字静态相机、网络系统、计算机、监视器、平板电脑、笔记本电脑、上网本、电视、视频游戏、智能手表或机动车辆。电子装置1000可以是处理数据的任何电子装置。

117.上面参照图1a至图4d描述的根据发明构思的实施例的半导体封装件10和半导体封装件20出于各种目的被应用于电子装置1000。在一些实施例中,电子装置1000可以包括参照图1a至图4d描述的根据发明构思的实施例的电感器100a、100b、100c、100d和100e中的一个。

118.图12是示出根据发明构思的实施例的半导体封装件1100的构造的框图。

119.参照图12,半导体封装件1100可以包括微处理单元(mpu)1110、存储器1120、接口1130、图形处理单元(gpu)1140、功能块1150以及将上述组件彼此连接的总线1160。

120.半导体封装件1100可以包括mpu 1110和gpu 1140两者或者mpu 1110和gpu 1140中的一个。

121.mpu 1110可以包括核和高速缓存。例如,mpu 1110可以包括多核。多核中的核可以具有相同的性能或不同的性能。多核中的核可以被同时激活或者可以在不同的时间点被激活。

122.存储器1120可以通过mpu 1110的控制来存储由功能块1150处理的结果。接口1130可以将信息或信号发送到外部装置,并且从外部装置接收信息或信号。gpu 1140可以执行图形功能。例如,gpu 1140可以执行视频编解码器或三维(3d)图形。功能块1150可以执行各种功能。例如,当半导体封装件1100是用于移动装置的应用处理器时,功能块1150中的一些可以执行通信功能。

123.半导体封装件1100可以包括上面参照图1a至图4d描述的根据发明构思的实施例的半导体封装件10和半导体封装件20中的一个。

124.虽然已经参考发明构思的实施例具体示出并描述了发明构思,但是将理解的是,在不脱离所附权利要求的精神和范围的情况下,可以对其进行形式和细节上的各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1