具有阶梯结构的三维存储器件及其形成方法与流程

背景技术:

1、本公开涉及存储器件以及用于形成存储器件的方法,更具体而言,涉及三维(3d)存储器件以及用于形成3d存储器件的方法。

2、通过改善工艺技术、电路设计、程序算法和制造工艺使得诸如存储器单元的平面半导体器件缩小到更小的尺寸。然而,随着半导体器件的特征尺寸接近下限,平面工艺和制造技术变得更加困难并且成本更加高昂。3d半导体器件架构能够解决一些平面半导体器件(例如,闪速存储器件)中的密度限制。

技术实现思路

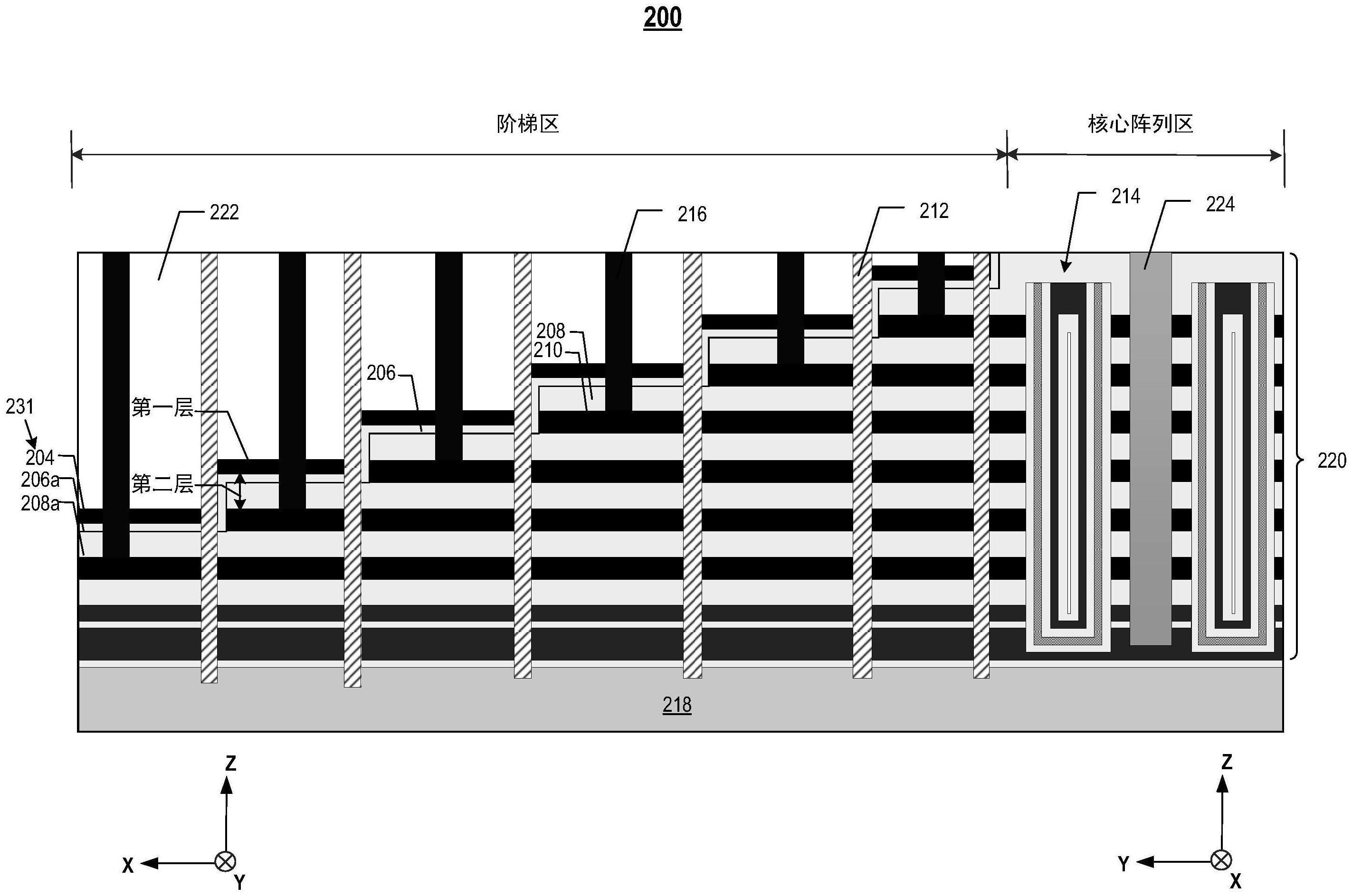

1、在一个方面中,一种3d存储器件包括交替的导电层和电介质层。所述导电层和电介质层的边缘限定了多个台阶。所述3d存储器件还包括多个焊盘(landing)结构,每个焊盘结构位于相应台阶处的相应导电层之上。所述焊盘结构中每者包括具有第一材料的第一层和具有第二材料的第二层,所述第一层位于所述第二层之上。

2、在一些实施方式中,所述第二层位于所述第一层和所述相应导电层之间。

3、在一些实施方式中,所述第一材料包括导电材料,并且所述第二材料包括电介质材料。

4、在一些实施方式中,所述第一材料包括钨。

5、在一些实施方式中,所述第二材料包括氧化硅、氮氧化硅或其组合。

6、在一些实施方式中,在所述多个台阶中的每者处,相应电介质层位于相应导电层以上并与之接触。

7、在一些实施方式中,所述3d存储器件包括覆盖电介质层,所述覆盖电介质层包括位于所述多个台阶之上的多个部分。在所述多个台阶中的每者处,所述覆盖电介质层的相应部分与所述相应电介质层和所述相应导电层接触;并且所述第二层包括所述覆盖电介质层的部分以及所述相应电介质层的部分。

8、在一些实施方式中,所述第一材料包括钨,并且所述第二材料包括氧化硅。

9、在一些实施方式中,所述第一层的厚度小于或等于55nm。

10、在一些实施方式中,所述焊盘结构还包括具有第三材料的第三层,所述第三层位于所述第一层中并且不同于所述第一材料。

11、在一些实施方式中,所述第三材料完全被所述第一层包围。

12、在一些实施方式中,所述第三材料包括氧化硅、氮化硅、氮氧化硅、多晶硅、碳或其组合。

13、在一些实施方式中,所述第三材料包括空气隙。

14、在一些实施方式中,所述第一层和所述相应导电层的总厚度大于或等于55nm。

15、在一些实施方式中,所述3d存储器件还包括多个互连结构,每个互连结构穿过所述第一层和所述第二层。所述互连结构均与所述相应导电层接触。

16、在一些实施方式中,所述3d存储器件还包括位于所述交替的导电层和电介质层中的沟道结构。所述沟道结构包括高k电介质层、存储器膜和半导体层。

17、在一些实施方式中,所述3d存储器件还包括在所述交替的导电层和电介质层中延伸的多个支撑结构。

18、在另一方面中,一种存储器系统包括3d存储器件。所述3d存储器件包括交替的导电层和电介质层。所述导电层和电介质层的边缘限定了多个台阶。所述3d存储器件还包括多个焊盘结构,每个焊盘结构位于相应台阶处的相应导电层之上。所述焊盘结构中的每者包括具有第一材料的第一层和具有第二材料的第二层,所述第一层位于所述第二层之上。所述存储器系统还包括耦接至所述3d存储器件并且被配置为控制所述3d存储器件的操作的存储器控制器。

19、在一些实施方式中,所述第二层位于所述第一层和所述相应导电层之间。

20、在一些实施方式中,所述第一材料包括导电材料,并且所述第二材料包括电介质材料。

21、在一些实施方式中,所述第一材料包括钨,并且所述第二材料包括氧化硅、氮氧化硅或其组合。

22、在一些实施方式中,所述存储器系统包括覆盖电介质层,所述覆盖电介质层具有位于所述多个台阶之上的多个部分。在所述多个台阶中的每者处,相应电介质层位于相应导电层以上并与之接触;所述覆盖电介质层的相应部分与所述相应电介质层和所述相应导电层接触;并且所述第二层包括所述覆盖电介质层的部分和所述相应电介质层的部分。

23、在一些实施方式中,所述第一材料包括钨,并且所述第二材料包括氧化硅;并且所述第一层的厚度小于或等于55nm。

24、在一些实施方式中,所述焊盘结构还包括具有第三材料的第三层,所述第三材料位于所述第一层中并且不同于所述第一材料。

25、在一些实施方式中,所述第三材料包括氧化硅、氮化硅、氮氧化硅、多晶硅、碳或其组合。

26、在一些实施方式中,所述第三材料包括空气隙。

27、在一些实施方式中,所述第一层和所述相应导电层的总厚度大于或等于55nm。

28、在另一方面中,一种用于形成3d存储器件的方法包括:形成包括交替的牺牲层和电介质层的堆叠结构,所述电介质层和所述牺牲层的边缘限定了多个台阶;形成均位于相应台阶上的牺牲部分;形成多个互连结构,每个互连结构穿过所述相应牺牲部分并且与所述相应台阶的相应牺牲层接触;去除所述牺牲部分和所述牺牲层,以形成多个横向凹陷;以及向所述横向凹陷中沉积导电材料。

29、在一些实施方式中,所述横向凹陷均包括第一凹陷部分以及位于所述第一凹陷部分之上的第二凹陷部分;并且向所述横向凹陷中沉积所述导电材料包括填充所述第一凹陷部分以及填充所述横向凹陷中的每者的所述第二凹陷部分的至少部分。

30、在一些实施方式中,沉积所述导电材料包括完全填满所述横向凹陷中的每者的所述第一凹陷部分。

31、在一些实施方式中,沉积所述导电材料包括完全填满所述横向凹陷中的每者的所述第二凹陷部分。

32、在一些实施方式中,沉积所述导电材料包括部分地填充所述横向凹陷中的每者的所述第二凹陷部分。

33、在一些实施方式中,沉积所述导电材料包括沉积钨、铝、钴、铜、多晶硅或其组合。

34、在一些实施方式中,所述方法还包括沉积不同于所述导电材料的第二材料,以填充所述第二凹陷部分。

35、在一些实施方式中,所述方法还包括在沉积所述第二材料之前去除所述第二凹陷部分中的所述导电材料。

36、在一些实施方式中,沉积所述第二材料包括沉积氧化硅、氮化硅、氮氧化硅、多晶硅、碳或其组合。

37、在一些实施方式中,所述方法还包括在所述电介质层之上形成覆盖电介质层。形成所述牺牲部分包括:在所述覆盖电介质层之上形成牺牲材料层;以及去除所述牺牲材料层的部分,以形成每者相互断开连接的所述牺牲部分。

38、在一些实施方式中,所述覆盖电介质层包括氧化硅,并且形成所述覆盖电介质层包括原子层沉积。

39、在一些实施方式中,形成所述牺牲部分包括:蚀刻所述电介质层,以露出均位于相应台阶处的所述牺牲层;在所述牺牲层之上形成牺牲材料层;以及去除所述牺牲材料层的部分,以形成每者相互断开连接的所述牺牲部分。

40、在一些实施方式中,形成均附接在所述相应台阶的相应牺牲层上的所述多个互连结构包括:形成均与所述相应台阶的相应牺牲部分接触的多个互连开口;继续对所述互连开口进行蚀刻,使得所述互连开口均与所述相应牺牲层接触;以及沉积互连结构的材料,使得所述互连结构均延伸穿过所述相应牺牲部分并且附接在所述相应牺牲层上。

41、在一些实施方式中,所述方法还包括在形成所述台阶之前形成在所述堆叠结构中延伸的沟道结构。形成所述沟道结构包括:形成在所述堆叠结构中延伸的沟道孔;以及在所述沟道孔中沉积高k电介质层,所述高k电介质层之上沉积存储器膜并且在存储器膜之上沉积半导体层。

42、在一些实施方式中,所述方法还包括:在形成所述互连结构之后,在所述交替的牺牲层和电介质层中形成缝隙结构;以及执行各向同性蚀刻工艺,以去除所述牺牲层和所述牺牲部分,从而形成所述横向凹陷。

43、在一些实施方式中,所述方法还包括在形成所述缝隙结构之前形成在所述堆叠结构中延伸的多个支撑结构。

44、在一些实施方式中,在形成所述互连结构之前形成所述支撑结构。

45、在一些实施方式中,在形成所述互连结构之后形成所述支撑结构。

- 还没有人留言评论。精彩留言会获得点赞!