系统级封装SIP芯片及其测试方法与流程

系统级封装sip芯片及其测试方法

技术领域

1.本发明涉及sip芯片技术领域,具体地说,涉及一种系统级封装sip芯片及其测试方法。

背景技术:

2.sip(system in a package,系统级封装)封装是将多种功能晶圆,包括处理器、存储器等功能晶圆根据应用场景、封装基板层数等因素,集成在一个封装内,从而实现一个基本完整功能的封装方案。sip级芯片是指采用了上述系统级封装这类新型封装技术,sip级芯片可将各功能所需的器件有效组合为一体,达到更高的集成度,从而实现一个基本完整的功能性器件。

3.但现有技术中,将多个功能芯片和无源器件在印刷电路板上进行系统集成时,没有考虑到带来的产品体积大、厚度厚等弊端,导致设计尺寸大,占用较大的面积,不利于小型化设计。

技术实现要素:

4.有鉴于此,本发明提供一种系统级封装sip芯片及其测试方法,利于sip芯片的小型化设计。

5.根据本发明的一个方面,提供一种系统级封装sip芯片,包括:

6.基板;

7.第一应用处理器单元,与所述基板连接;

8.电源管理单元和无线通信单元,均与所述基板连接,且均与所述第一应用处理器单元连接;所述电源管理单元分布于第一裸片,所述无线通信单元分布于第二裸片,所述第一裸片和所述第二裸片堆叠设置;以及

9.无线收发单元,分别与所述无线通信单元、所述基板以及所述第一应用处理器单元连接。

10.可选地,所述sip芯片包含有多个不同的功能单元,不同的功能单元分布于不同的裸片,且所有的裸片采用不同的堆叠设计方案。

11.可选地,所述无线通信单元包含第二应用处理器单元和基带处理单元,所述第二应用处理器单元和所述基带处理单元均与所述基板连接,且均与无线收发单元连接。

12.可选地,所述无线收发单元包括发射链路功率放大器和接收链路功率放大器;所述sip芯片具有一封装空间,所述发射链路功率放大器和所述接收链路功率放大器均位于所述封装空间内。

13.可选地,所述基板设置为多层结构。

14.可选地,所述第一裸片和所述第二裸片之间、所述第一裸片与所述基板之间、以及所述第二裸片与所述基板之间采用金线键合的方式进行封装。

15.根据本发明的另一个方面,提供一种sip芯片的测试方法,用于对上述sip芯片进

行测试,所述测试方法包括步骤:

16.s110,获取第一次测试结果为不良品的芯片,作为待测试芯片;

17.s120,获取所述待测试芯片所属的芯片类别,作为目标类别;

18.s130,获取各个测试机台在历史测试中针对所述目标类别的测试通过率;

19.s140,基于所述测试通过率,确定目标测试机台;以及

20.s150,利用所述目标测试机台对所述待测试芯片进行二次测试。

21.可选地,步骤s140包括:

22.将所述测试通过率最高的前n个测试机台,作为备选测试机台;其中,n为大于1的整数;

23.获取各所述备选测试机台的当前测试任务和当前测试进度;

24.基于所述当前测试任务和当前测试进度,计算每一所述备选测试机台完成当前测试任务所需的预计剩余时长;以及

25.将最小的所述预计剩余时长对应的所述备选测试机台,作为目标测试机台。

26.可选地,所述测试通过率包括一次测试通过率数据和两次测试通过率数据;步骤s140包括:

27.基于所述测试通过率,获取各个测试机台关联所述目标类别的一次测试通过率数据;以及

28.将所述一次测试通过率数据中一次测试通过率最大的测试机台,作为目标测试机台。

29.可选地,步骤s140包括:

30.将所述测试通过率最大的测试机台,作为目标测试机台。

31.可选地,步骤s130包括:

32.获取各个测试机台在所有目标厂家的历史测试中针对所述目标类别的测试通过率;所述目标厂家为生产所述目标类别的sip芯片的厂家;

33.依据各个目标厂家的测试通过率,计算各所述测试机台的综合通过率;

34.步骤s140包括:

35.将所述综合通过率最大的测试机台,作为目标测试机台。

36.本发明与现有技术相比的有益效果在于:

37.本发明提供的系统级封装sip芯片及其测试方法通过将电源管理单元和无线通信单元分设于不同的裸片上,并且将各自的裸片以堆叠方式设置,实现在内部集成多个功能单元的同时,减小了sip芯片产品的体积,利于该sip芯片的小型化设计。

附图说明

38.此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本发明的实施例,并与说明书一起用于解释本发明的原理。显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

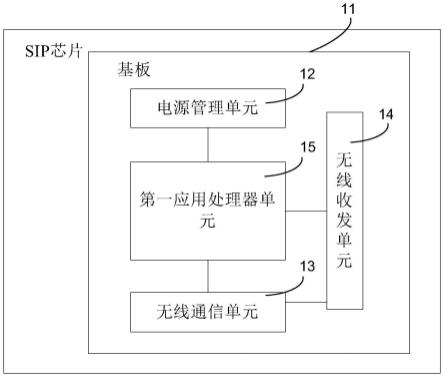

39.图1为本发明一实施例公开的一种系统级封装sip芯片的结构示意图;

40.图2为本发明一实施例公开的sip芯片的测试方法的流程示意图;

41.图3为本发明一实施例公开的sip芯片的测试方法中步骤s140的流程示意图;

42.图4为本发明另一实施例公开的sip芯片的测试方法的流程示意图;

43.图5为本发明另一实施例公开的sip芯片的测试方法的流程示意图;

44.图6为本发明另一实施例公开的sip芯片的测试方法的流程示意图。

具体实施方式

45.现在将参考附图更全面地描述示例实施方式。然而,示例实施方式能够以多种形式实施,且不应被理解为限于在此阐述的实施方式。相反,提供这些实施方式使得本发明将全面和完整,并将示例实施方式的构思全面地传达给本领域的技术人员。所描述的特征、结构或特性可以以任何合适的方式结合在一个或更多实施方式中。在下面的描述中,提供许多具体细节从而给出对本公开的实施方式的充分理解。然而,本领域技术人员将意识到,可以实践本公开的技术方案而没有所述特定细节中的一个或更多,或者可以采用其它的方法、材料、装置等。在其它情况下,不详细示出或描述公知技术方案以避免模糊本公开的各方面。图中相同的附图标记表示相同或类似的结构,因而将省略它们的详细描述。

46.用语“一个”、“一”、“该”、“所述”和“至少一个”用以表示存在一个或多个要素/组成部分/等;用语“包括”、“具有”以及“设有”用以表示开放式的包括在内的意思并且是指除了列出的要素/组成部分/等之外还可存在另外的要素/组成部分/等。

47.如图1所示,本发明公开了一种系统级封装sip芯片。该芯片包含有基板11、电源管理单元12、无线通信单元13、无线收发单元14以及第一应用处理器单元15。第一应用处理器单元15与基板11连接。

48.上述电源管理单元12、无线通信单元13和无线收发单元14均与基板11连接。且上述电源管理单元12、无线通信单元13和无线收发单元14均与第一应用处理器单元15连接。无线收发单元14与上述无线通信单元13连接。上述电源管理单元12分布于第一裸片,上述无线通信单元13分布于第二裸片,上述第一裸片和上述第二裸片堆叠设置。进一步地,上述无线收发单元14可以设置于第三裸片,上述第一裸片、第二裸片和第三裸片以堆叠方式设置。相比于平铺的方式设置多个裸片,这样利于减小整个sip芯片的体积,从而利于小型化设计。

49.基板11上可以设置有晶体振荡器、去耦电容、功率电感、射频匹配电路等所需的轻量级器件。电源管理单元12用于对sip的电源进行管理。该电源管理单元12利于实现系统最大限度的运行在低功耗模式下,低至2ua以下。无线通信单元13用于进行无线通信。无线收发单元14用于布置无线收发链路中所需的电路,比如上述发射链路功率放大器和接收链路功率放大器,及其关联周边器件。

50.本实施例中,上述无线通信单元13包含第二应用处理器单元和基带处理单元,上述第二应用处理器单元和基带处理单元分别与上述基板11连接。第二应用处理器单元和基带处理单元还分别与无线收发单元14连接。无线收发单元14包括发射链路功率放大器和接收链路功率放大器。这样可以实现在使用中,芯片外围无需额外增加任何功率器件,芯片外围仅需一颗隔直电容和天线即可实现整体无线收发功能。

51.在对上述芯片进行封装时,上述第一裸片和上述第二裸片之间、所述第一裸片与所述基板之间、以及所述第二裸片与所述基板之间均可以采用金线键合的方式进行封装;

这样可以保证在较低损耗率的同时,提升传导率。需要说明的是,其他不同的裸片之间均可以通过金线键合的方式进行封装。

52.本实施例中,上述sip芯片具有一封装空间,上述发射链路功率放大器和上述接收链路功率放大器均位于上述封装空间内。这样可以避免前级和接收链路功率放大器设置在芯片外围,不利于芯片小型化的问题;以及避免前级和接收链路功率放大器设置在芯片外围,导致无线通信指标测试时不达标,无线通信性能稳定性较差,增加测试需求的问题。

53.本实施例中,上述基板11设置为多层结构。该多层设计的基板11可以把各个信号分层处理,利于提高芯片的抗干扰能力,可在小型化的同时,提高芯片的抗干扰、稳定性、一致性等性能。另外,敏感设计链路比如丰富的对外接口即gipo接口,均可以分布在不同层。因为有些接口容易受外界干扰,比如usb 3.0有些线会相互干扰,这样可以提高芯片的抗干扰性能。

54.本实施例中,芯片上设计有大量gpio(general purpose input/output port,通用输入/输出端口)端口。还设计有串口通讯接口、定时器、串行外设接口、模数/数模转换器等。

55.本实施例中,晶体振荡器、去耦电容、功率电感、射频匹配电路通过锡膏贴焊于基板11或键合线的方式,实现各器件间的电气连接。最大程度的缩小了设计空间,实现了高度集成、小型的芯片化设计的同时,提高了芯片的抗干扰、稳定和一致性的性能。

56.作为一可选实施例,上述sip芯片还可以包含有其他的功能单元,不同的功能单元分布于不同的裸片,且所有的裸片可以全部呈堆叠布置。所有的裸片采用不同的堆叠设计方案。也可以部分堆叠布置,剩余部分以平铺方式布置;这样可以在兼顾sip芯片内部结构性能的同时,减小sip芯片的体积。

57.需要说明的是,图1中示出的电源管理单元12、无线通信单元13、无线收发单元14、基板11之间的位置关系并不表示它们之间真实的位置关系。作为一可选实施例,具体实施时,上述电源管理单元12、无线通信单元13和无线收发单元14可以在物理上设置于基板11的上方。但本技术不以此为限。

58.如图2所示,本发明一实施例还提供了一种sip芯片的测试方法,用于对上述任一实施例公开的sip芯片进行二次清不良测试。上述sip芯片的详细结构特征和优势可参照上述实施例的描述,此处不再赘述。本实施例公开的上述测试方法包括步骤:

59.s110,获取第一次测试结果为不良品的芯片,作为待测试芯片。

60.s120,获取上述待测试芯片所属的芯片类别,作为目标类别。

61.s130,获取各个测试机台在历史测试中针对上述目标类别的测试通过率。

62.s140,基于上述测试通过率,确定目标测试机台。

63.s150,利用上述目标测试机台对上述待测试芯片进行二次测试。

64.具体而言,一些芯片在进行测试时,可能需要进行多次测试,最后测试结果为不良时才会判定为不良品,只要有一次测试通过则判定为良品。比如,第一次在一个测试机台测试完成后,结果为不良品。第二次可以在同一测试机台再次测试,也可以在另一个测试机台再次测试。当第二次测试结果再次为未通过时,那么可能需要进行第三次测试。直至第三次测试结果为未通过,才判定为不良品。针对这种需要进行两次以上测试的情况,需要让芯片尽早通过测试,是本领域技术人员共同想要实现的目标。

65.比如,第一次测试为未通过,第二次测试为通过时,那么该芯片就测试结束且判定为良品。具体实施时,当第一次测试未通过时,第二次测试如果仍然采用第一次测试的机台测试,那么很可能会再次不通过,这样将会明显影响sip芯片测试时清不良的效率,甚至造成芯片良率下降的风险。

66.本技术参考各个测试机台在历史测试任务中,关于待测试芯片的目标类别的测试通过率,基于该测试通过率确定的目标测试机台,将会利于提高二次测试的通过率,从而利于提高芯片清不良的效率即提高了测试效率,也利于提高该批次的芯片良率。示例性地,上述芯片类别比如可以为心率芯片,即用于检测心率。上述步骤s140可以为选取测试通过率最高的机台作为目标测试机台。也可以为测试通过率最高的多个机台作为备选列表,然后从备选列表中选取针对所有类型的芯片的综合测试通过率最高的机台作为目标测试机台。这样就会进一步利于提高芯片二次测试的通过率,从而提高了芯片测试效率,同时有利于提高芯片良率。

67.如图3所示,本技术的另一实施例在上述图2对应实施例的基础上,公开了另一sip芯片测试方法。该方法中,上述步骤s140包括:

68.s141,将上述测试通过率最高的前n个测试机台,作为备选测试机台。其中,n为大于1的整数。

69.s142,获取各上述备选测试机台的当前测试任务和当前测试进度。

70.s143,基于上述当前测试任务和当前测试进度,计算每一上述备选测试机台完成当前测试任务所需的预计剩余时长。

71.s144,将最小的上述预计剩余时长对应的上述备选测试机台,作为目标测试机台。

72.具体而言,本实施例将备选测试机台中当前任务最快结束的机台作为目标测试机台,可以避免该待测试芯片二次测试的等待时间过长,利于提高其测试效率;另一方面也利于提高所有测试机台的综合利用效率。

73.如图4所示,本技术的另一实施例在上述图2对应实施例的基础上,公开了另一sip芯片测试方法。该方法中,上述测试通过率包括一次测试通过率数据和两次测试通过率数据。其中,一次测试通过率数据即为所有被测试sip芯片中,仅需一次测试就通过,也即第一次的测试结果就为通过的sip芯片所占的比例。两次测试通过率数据表示第一次测试时未通过,且在第二次测试时通过的sip芯片在所有被测试sip芯片中所占的比例。

74.本实施中,在包含上述步骤s110、s120、s130和s150的基础上,还包括步骤:

75.s145,基于上述测试通过率,获取各个测试机台关联上述目标类别的一次测试通过率数据。以及

76.s146,将上述一次测试通过率数据中一次测试通过率最大的测试机台,作为目标测试机台。

77.本实施例中,相比于采用两次测试通过率较高的测试机台,甚至需要更多次测试才通过的测试机台,采用一次测试通过率最大的测试机台作为目标测试机台,会有利于提高芯片测试效率,同时有利于提高芯片良率。

78.如图5所示,本技术的另一实施例在上述图2对应实施例的基础上,公开了另一sip芯片测试方法。本实施中,在包含上述步骤s110、s120、s130和s150的基础上,还包括步骤:

79.s147,将上述测试通过率最大的测试机台,作为目标测试机台。

80.这样实现了有利于提高芯片测试效率,同时有利于提高芯片良率。

81.如图6所示,本技术的另一实施例在上述图2对应实施例的基础上,公开了另一sip芯片测试方法。本实施中,在包含上述步骤s110、s120和s150的基础上,还包括步骤:

82.s131,获取各个测试机台在所有目标厂家的历史测试中针对上述目标类别的测试通过率。上述目标厂家为生产上述目标类别的sip芯片的厂家。

83.s132,依据各个目标厂家的测试通过率,计算各上述测试机台的综合通过率。

84.s148,将上述综合通过率最大的测试机台,作为目标测试机台。

85.本实施例采用所有测试过该类别sip芯片的厂家数据作为参考,计算各测试机台的综合通过率,从而使得综合通过率数据更加准确,依据该数据确定的目标测试机台利于使得待测试芯片的二次测试通过概率更高,从而利于提高芯片测试效率,同时有利于提高芯片良率。

86.综上,本发明的系统级封装sip芯片及其测试方法至少具有如下优势:

87.本发明上述实施例公开的系统级封装sip芯片及其测试方法通过将电源管理单元和无线通信单元分设于不同的裸片上,并且将各自的裸片以堆叠方式设置,实现在内部集成多个功能单元的同时,减小了sip芯片产品的体积,利于该sip芯片的小型化设计;上述公开的测试方法将历史测试中针对该芯片类别的测试通过率较高的机台进行二次测试,利于提高清芯片不良品的效率,提高了测试工站的运转效率;并且避免了清不良品的效率不高导致良率下降的问题。

88.以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1