一种AlGaN外延结构及其制备方法和半导体器件与流程

一种algan外延结构及其制备方法和半导体器件

技术领域

1.本发明涉及半导体外延技术领域,尤其涉及一种algan外延结构及其制备方法和半导体器件。

背景技术:

2.algan作为宽禁带半导体材料,可以实现禁带宽度3.4ev到6.2ev之间连续可调,被广泛应用于载流子阻挡层、紫外发光层及高电子气异质结等结构,在诸多领域有着重要应用价值。

3.由于同质衬底缺乏,algan材料通常采用异质衬底外延生长,由于和衬底存在较大的晶格常数和热膨胀系数差异,algan材料在外延生长过程中会产生大量的位错,同时还会出现外延薄膜的翘曲现象,甚至出现裂纹,这将直接导致半导体器件出现漏电等造成器件功能失效。

技术实现要素:

4.本发明的目的在于提供一种algan外延结构及其制备方法和半导体器件,用于为algan外延层提供高质量低应力的生长模板,获得具有低表面缺陷的高晶体质量algan外延层。

5.本发明的目的采用以下技术方案实现:

6.一种algan外延结构,包括:

7.衬底;

8.gan外延复合层,位于所述衬底上,所述gan外延复合层包括gan外延工艺层和sin

x

插入层,所述gan外延复合层的至少一部分为交替层叠的gan外延工艺层和sin

x

插入层;

9.algan外延复合层,位于所述gan外延复合层上,所述algan外延复合层包括algan外延工艺层和mgny插入层,所述algan外延复合层的至少一部分为交替层叠的algan外延工艺层和mgny插入层;

10.algan外延层,位于所述algan外延复合层上。

11.在一具体实施例中,所述gan外延复合层的厚度为1-2μm,交替层叠的gan外延工艺层的单层厚度为10-100nm,交替层叠的sin

x

插入层的单层厚度为1-2nm;

12.所述algan外延复合层的厚度为5-200nm,交替层叠的algan外延工艺层的单层厚度为1-10nm,交替层叠的mgny插入层的单层厚度为0.5-1nm;

13.所述algan外延层的厚度为20-2000nm。

14.在一具体实施例中,所述gan外延复合层中,交替层叠的所述gan外延工艺层的总厚度不超过所述gan外延复合层厚度的二分之一;

15.所述algan外延复合层中,交替层叠的所述algan外延工艺层的总厚度不超过所述algan外延复合层厚度的二分之一。

16.在一具体实施例中,所述gan外延复合层中,非交替层叠的所述gan外延工艺层的

厚度为0.5-1μm;

17.所述algan外延复合层中,非交替层叠的所述algan外延工艺层的厚度为2.5-100nm。

18.在一具体实施例中,所述gan外延复合层中,交替层叠的所述gan外延工艺层和sin

x

插入层位于非交替层叠的所述gan外延工艺层的上方或下方,或者,位于两个非交替层叠的所述gan外延工艺层之间;

19.所述algan外延复合层中,交替层叠的algan外延工艺层和mgny插入层位于非交替层叠的algan外延工艺层的上方或下方,或者,位于两个非交替层叠的所述algan外延工艺层之间。

20.在一具体实施例中,所述algan外延层表面粗糙度为0.1-10nm。

21.一种algan外延结构的制备方法,包括:

22.步骤s1:提供衬底;

23.步骤s2:在所述衬底上生长gan外延复合层,所述gan外延复合层包括gan外延工艺层和sin

x

插入层,所述gan外延复合层的至少一部分为交替生长的gan外延工艺层和sin

x

插入层;

24.步骤s3:在所述gan外延复合层上生长algan外延复合层,所述algan外延复合层包括algan外延工艺层和mgny插入层,所述algan外延复合层的至少一部分为交替生长的algan外延工艺层和mgny插入层;

25.步骤s4:在所述algan外延复合层上生长algan外延层。

26.在一具体实施例中,所述步骤s2包括:

27.先在所述衬底上生长非交替层叠的所述gan外延工艺层,再在非交替层叠的所述gan外延工艺层上生长交替层叠的gan外延工艺层和sin

x

插入层;或者,

28.先在所述衬底上生长交替层叠的gan外延工艺层和sin

x

插入层,再在交替层叠的gan外延工艺层和sin

x

插入层上生长非交替层叠的所述gan外延工艺层;或者,

29.先在所述衬底上生长非交替层叠的所述gan外延工艺层,再在非交替层叠的所述gan外延工艺层上生长交替层叠的gan外延工艺层和sin

x

插入层,最后在交替层叠的gan外延工艺层和sin

x

插入层上生长非交替层叠的所述gan外延工艺层。

30.在一具体实施例中,所述步骤s3包括:

31.先在所述衬底上生长非交替层叠的所述algan外延工艺层,再在非交替层叠的所述algan外延工艺层上生长交替层叠的algan外延工艺层和mgny插入层;或者,

32.先在所述衬底上生长交替层叠的algan外延工艺层和mgny插入层,再在交替层叠的algan外延工艺层和mgny插入层上生长非交替层叠的所述algan外延工艺层;或者,

33.先在所述衬底上生长非交替层叠的所述algan外延工艺层,再在非交替层叠的所述algan外延工艺层上生长交替层叠的algan外延工艺层和mgny插入层,最后在交替层叠的algan外延工艺层和mgny插入层上生长非交替层叠的所述algan外延工艺层。

34.一种半导体器件,包括上述任一项所述的algan外延结构。

35.与现有技术相比,本发明的有益效果至少包括:

36.通过设置包含gan外延工艺层和sin

x

插入层的gan外延复合层和包含algan外延工艺层和mgny插入层的algan外延复合层,利用原子的半径差异(mg>si),在gan外延复合层

中引入sin

x

插入层,可以调整gan外延复合层的晶格常数向algan靠近,在algan外延复合层中引入mgny插入层,可以调整algan外延复合层的晶格常数向gan靠近,可以实现gan外延复合层和algan外延复合层的晶体匹配,为algan外延层提供高质量低应力的生长模板,最终能够获得具有低表面缺陷的高晶体质量algan外延层。

37.此外,本发明中,形成的sin

x

插入层和mgny插入层工艺可以避免常规gan和algan材料掺杂工艺调整晶格常数带来的材料导电性能改变的影响,拓宽了algan外延层的应用领域。

附图说明

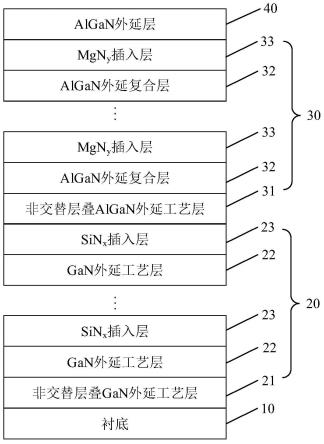

38.图1是本发明一个实施例的algan外延结构的结构示意图。

39.图2是本发明另一实施例的algan外延结构的结构示意图。

40.图3是本发明又一实施例的algan外延结构的结构示意图。

41.图4是本发明又一实施例的algan外延结构的结构示意图。

42.图5是本发明又一实施例的algan外延结构的结构示意图。

43.图6是本发明实施例的algan外延结构的制备方法的流程示意图。

44.图7是本发明实施例1的algan外延结构的光学显微镜照片。

45.图8是本发明对比例1的algan外延结构的光学显微镜照片。

46.图中:10、衬底;20、gan外延复合层;21、非交替层叠gan外延工艺层;22、gan外延工艺层;23、sin

x

插入层;30、algan外延复合层;31、非交替层叠algan外延工艺层;32、algan外延工艺层;33、sin

x

插入层;40、algan外延层。

具体实施方式

47.现在将参考附图更全面地描述示例实施方式。然而,示例实施方式能够以多种形式实施,且不应被理解为限于在此阐述的实施方式;相反,提供这些实施方式使得本发明更全面和完整,并将示例实施方式的构思全面地传达给本领域的技术人员。在图中相同的附图标记表示相同或类似的结构,因而将省略对它们的重复描述。

48.本发明中所描述的表达位置与方向的词,均是以附图为例进行的说明,但根据需要也可以做出改变,所做改变均包含在本发明保护范围内。

49.参照图1-5,本发明提供一种algan外延结构,包括依次层叠的衬底10、gan外延复合层20、algan外延复合层30和algan外延层40。

50.衬底10可以是蓝宝石材质的衬底10,还可以由氧化锌(zno)、氮化镓(gan)、碳化硅(sic)、氮化铝(aln)或类似物形成。

51.gan外延复合层20位于所述衬底10上,所述gan外延复合层20包括gan外延工艺层和sin

x

插入层23,0≤x≤1,所述gan外延复合层20的至少一部分为交替层叠的gan外延工艺层22和sin

x

插入层23。具体地,gan外延复合层20可以包括非交替层叠部分和交替层叠部分,非交替层叠部分和交替层叠部分上下层叠设置,非交替层叠部分可以包括非交替层叠的gan外延工艺层21(非交叠gan外延工艺层21),非交替层叠的gan外延工艺层21可以通过一次外延生长得到,交替层叠部分包括交替层叠的gan外延工艺层22和sin

x

插入层23,交替层叠的gan外延工艺层22和sin

x

插入层23则可以通过交替外延生长gan外延工艺层22和sin

x

插入层23得到。

52.algan外延复合层30位于所述gan外延复合层20上,所述algan外延复合层30包括algan外延工艺层和mgny插入层33,0≤y≤1,所述algan外延复合层30的至少一部分为交替层叠的algan外延工艺层32和mgny插入层33。具体地,algan外延复合层30可以包括非交替层叠部分和交替层叠部分,非交替层叠部分和交替层叠部分上下层叠设置,非交替层叠部分可以包括非交替层叠的algan外延工艺层31(非交叠algan外延工艺层31),非交替层叠的algan外延工艺层31可以通过一次外延生长得到,交替层叠部分包括交替层叠的algan外延工艺层32和mgny插入层33,交替层叠的algan外延工艺层32和mgny插入层33则可以通过交替外延生长algan外延工艺层32和mgny插入层33得到。

53.algan外延层40位于所述algan外延复合层30上。

54.由此,通过设置包含gan外延工艺层22和sin

x

插入层23的gan外延复合层20和包含algan外延工艺层32和mgny插入层33的algan外延复合层30,利用原子的半径差异(mg>si),在gan外延复合层20中引入sin

x

插入层23,可以调整gan外延复合层20的晶格常数向algan靠近,在algan外延复合层30中引入mgny插入层33,可以调整algan外延复合层30的晶格常数向gan靠近,可以实现gan外延复合层20和algan外延复合层30的晶体匹配,为algan外延层40提供高质量低应力的生长模板,最终能够获得具有低表面缺陷的高晶体质量algan外延层40。

55.此外,如通过掺杂工艺改变gan外延复合层20和algan外延复合层30的晶格常数,则会带来外延复合层导电性能的改变,而作为algan外延层40的生长模板,则不期望改变其导电性能。本发明中,形成的sin

x

插入层23和mgny插入层33工艺可以避免常规gan和algan材料掺杂工艺调整晶格常数带来的材料导电性能改变的影响,拓宽了algan外延层40的应用领域。

56.在一具体实施方式中,所述gan外延复合层20的厚度为1-2μm,例如为1.3μm、1.5μm或1.8μm,交替层叠的gan外延工艺层22的单层厚度为10-100nm,例如为30nm、50nm或80nm,交替层叠的sin

x

插入层23的单层厚度为1-2nm,例如为1.3nm、1.5nm或1.8nm。将sin

x

插入层23的单层厚度设置为1-2nm则更有利于调整gan外延复合层20的晶格常数向algan靠近。

57.所述algan外延复合层30的厚度为5-200nm,例如为50nm、100nm或150nm,交替层叠的algan外延工艺层32的单层厚度为1-10nm,例如为3nm、5nm或8nm,交替层叠的mgny插入层33的单层厚度为0.5-1nm,例如为0.6nm、0.8nm或0.9nm。厚度为5-200nm的algan外延复合层30与厚度为1-2μm的gan外延复合层20配合,可以有效缓解衬底10与algan外延层40之间的晶格失配,改善生长于衬底10上的晶体的质量。将mgny插入层33的单层厚度设置为0.5-1nm则更有利于调整algan外延复合层30的晶格常数向gan靠近,实现gan外延复合层20和algan外延复合层30的晶体匹配。

58.所述algan外延层40的厚度为20-2000nm,例如为100nm、300nm、500nm、1000nm、1300nm、1500nm或1800nm。

59.在一具体实施方式中,所述gan外延复合层20中,交替层叠的所述gan外延工艺层22的总厚度不超过所述gan外延复合层20厚度的二分之一,其中,非交替层叠的所述gan外延工艺层22的厚度优选为0.5-1μm,例如为0.6μm、0.8μm或0.9μm。所述algan外延复合层30中,交替层叠的所述algan外延工艺层32的总厚度不超过所述algan外延复合层30厚度的二

分之一,其中,非交替层叠的algan外延工艺层31的厚度优选为2.5-100nm,例如为10nm、30nm、50nm、或80nm。

60.在一具体实施方式中,如图1-3所示,所述gan外延复合层20中,交替层叠的所述gan外延工艺层22和sin

x

插入层23位于非交替层叠的所述gan外延工艺层21的上方或下方,或者,位于两个非交替层叠的所述gan外延工艺层21之间。

61.如图1、4和5所示,所述algan外延复合层30中,交替层叠的algan外延工艺层32和mgny插入层33位于非交替层叠的algan外延工艺层31的上方或下方,或者,位于两个非交替层叠的所述algan外延工艺层31之间。

62.通过改变交替层叠的所述gan外延工艺层22和sin

x

插入层23的位置,或者,通过改变交替层叠的所述algan外延工艺层32和mgny插入层33的位置,可以调整algan外延层40的表面粗糙度,所述algan外延层40表面粗糙度能够在0.1-10nm范围内调整,从而实现将表面粗化工艺从晶体质量工艺控制中单独分离出来,进而扩大了外延层表面粗化的外延生长工艺窗口,从而满足不同的外延技术需求。

63.所述gan外延复合层20中,交替层叠的所述gan外延工艺层22的总厚度不超过所述gan外延复合层20厚度的二分之一,所述algan外延复合层30中,交替层叠的所述algan外延工艺层32的总厚度不超过所述algan外延复合层30厚度的二分之一,此处根据实际生产工艺对最大厚度进行限制,一方面是外延工艺层厚度超过二分之一时,sin

x

插入层23和mgny插入层33无法起到对gan外延工艺层和algan外延工艺层的晶格调整的作用,另一方面,外延工艺层厚度超过二分之一时,algan外延层40的表面粗糙度受到交叠层在非交叠层的插入位置的影响不明显,无法实现仅仅通过插入位置改变表面粗糙度的工艺。

64.本发明还提供一种半导体器件,包括上述任一实施方式所述的algan外延结构,半导体器件例如是led器件、hemt器件等。

65.如图6所示,本发明还提供一种algan外延结构的制备方法,包括以下步骤:步骤s1-步骤s4,algan外延结构的制备可以采用mocvd外延生长设备完成。

66.步骤s1:提供衬底10。

67.衬底10可以是蓝宝石材质的衬底10,还可以由氧化锌(zno)、氮化镓(gan)、碳化硅(sic)、氮化铝(aln)或类似物形成。

68.步骤s2:在所述衬底10上生长gan外延复合层20,所述gan外延复合层20包括gan外延工艺层和sin

x

插入层23,所述gan外延复合层20的至少一部分为交替生长的gan外延工艺层22和sin

x

插入层23。

69.具体地,在1095-1125℃温度条件、150-350torr压力条件下,在衬底10上生长厚度为1-2μm的gan外延复合层20,具体可以包括步骤s201和步骤s202。

70.步骤s201:生长厚度为0.5-1μm的非交替层叠的gan外延工艺层21。

71.步骤s202:周期性循环交替生长单层厚度为10-100nm的gan外延工艺层22和单层厚度为1-2nm的sin

x

插入层23,循环周期中gan外延工艺层22的总厚度优选不超过gan外延复合层20厚度的二分之一。

72.步骤s202可以在步骤s201之后、之前或两个步骤s201之间进行,从而使交替层叠的所述gan外延工艺层22和sin

x

插入层23位于非交替层叠的gan外延工艺层21的上方或下方,或者,位于两个非交替层叠的所述gan外延工艺层21之间,进而调整algan外延层40的表

面粗糙度。

73.具体地,所述步骤s2可以包括:

74.先在所述衬底10上生长非交替层叠的所述gan外延工艺层21,再在非交替层叠的所述gan外延工艺层21上生长交替层叠的gan外延工艺层22和sin

x

插入层23。

75.或者,先在所述衬底10上生长交替层叠的gan外延工艺层22和sin

x

插入层23,再在交替层叠的gan外延工艺层22和sin

x

插入层23上生长非交替层叠的所述gan外延工艺层21。

76.或者,先在所述衬底10上生长非交替层叠的所述gan外延工艺层21,再在非交替层叠的所述gan外延工艺层21上生长交替层叠的gan外延工艺层22和sin

x

插入层23,最后在交替层叠的gan外延工艺层22和sin

x

插入层23上生长非交替层叠的所述gan外延工艺层21。

77.步骤s3:在所述gan外延复合层20上生长algan外延复合层30,所述algan外延复合层30包括algan外延工艺层和mgny插入层33,所述algan外延复合层30的至少一部分为交替生长的algan外延工艺层32和mgny插入层33。

78.具体地,在1065-1095℃温度条件、50-150torr压力条件下,在gan外延复合层20上生长厚度为5-200nm的algan外延复合层30,具体可以包括步骤s301和步骤s302。

79.步骤s301:生长厚度为2.5-100nm的非交替层叠的algan外延工艺层31。

80.步骤s302:周期性循环交替生长单层厚度为1-10nm的algan外延工艺层32和单层厚度为0.5-1nm的mgny插入层33,循环周期中algan外延工艺层32的总厚度优选不超过algan外延复合层30厚度的二分之一。

81.步骤s302可以在步骤s301之后、之前或两个步骤s301之间进行,从而使交替层叠的所述algan外延工艺层32和mgny插入层33位于非交替层叠的algan外延工艺层31的上方或下方,或者,位于两个非交替层叠的algan外延工艺层31之间,进而调整algan外延层40的表面粗糙度。

82.具体地,所述步骤s3可以包括:

83.先在所述衬底10上生长非交替层叠的algan外延工艺层31,再在非交替层叠的algan外延工艺层31上生长交替层叠的algan外延工艺层32和mgny插入层33。

84.或者,先在所述衬底10上生长交替层叠的algan外延工艺层32和mgny插入层33,再在交替层叠的algan外延工艺层32和mgny插入层33上生长非交替层叠的algan外延工艺层31。

85.或者,先在所述衬底10上生长非交替层叠的algan外延工艺层31,再在非交替层叠的algan外延工艺层31上生长交替层叠的algan外延工艺层32和mgny插入层33,最后在交替层叠的algan外延工艺层32和mgny插入层33上生长非交替层叠的algan外延工艺层31。

86.步骤s4:在所述algan外延复合层30上生长algan外延层40。

87.具体地,在1085-1115℃温度条件、50-150torr压力条件下,在algan外延复合层30上,生长厚度为20-2000nm的algan外延层40。

88.实施例1:

89.采用mocvd外延生长设备制备algan外延结构,包括:

90.步骤s11:提供蓝宝石衬底10。

91.步骤s21:在1105℃温度条件、200orr压力条件下,在衬底10上生长1.5μm的gan外延复合层20,包括以下步骤:

92.先在衬底10上,周期性循环交替生长单层厚度为50m的gan外延工艺层22和单层厚度为1.5nm的sin

x

插入层23,循环周期中gan外延工艺层总厚度为gan复合层厚度的20%;

93.再在交替层叠的gan外延工艺层22和sin

x

插入层23上,生长厚度为0.6μm的非交替层叠的gan外延工艺层21。

94.步骤s31:在1075℃温度条件、100torr压力条件下,在gan外延复合层20上生长厚度为100nm的algan外延复合层30,包括以下步骤:

95.先在gan外延复合层20上,周期性循环交替生长单层厚度为5nm的algan外延工艺层32和单层厚度为0.8nm的mgny插入层33,循环周期中algan外延工艺层32总厚度为algan外延复合层30厚度的20%;

96.再在交替层叠的algan外延工艺层32和mgny插入层33上,生长厚度为80nm的非交替层叠的algan外延工艺层31。

97.步骤s41:在1095℃温度条件、120torr压力条件下,在algan外延复合层30上,生长厚度为1000nm的algan外延层40。

98.实施例2:

99.实施例2与实施例1的制备过程基本相同,区别仅在于步骤s21不同。

100.步骤s21:

101.先在衬底10上,生长厚度为0.6μm的非交替层叠的gan外延工艺层21;

102.再在非交替层叠的gan外延工艺层21上,周期性循环交替生长单层厚度为50nm的gan外延工艺层22和单层厚度为1.5nm的sin

x

插入层23,循环周期中gan外延工艺层总厚度为gan复合层厚度的20%。

103.实施例3:

104.实施例3与实施例1的制备过程基本相同,区别仅在于步骤s21不同。

105.步骤s21:

106.先在衬底10上生长厚度为0.3μm的非交替层叠的gan外延工艺层21。

107.再在非交替层叠的gan外延工艺层21上,周期性循环交替生长单层厚度为50nm的gan外延工艺层22和单层厚度为1.5nm的sin

x

插入层23,循环周期中gan外延工艺层总厚度为gan复合层厚度的20%。

108.最后在交替层叠的gan外延工艺层22和sin

x

插入层23上生长厚度为0.3μm的非交替层叠的所述gan外延工艺层21。

109.实施例4:

110.实施例4与实施例1的制备过程基本相同,区别仅在于步骤s31不同。

111.步骤s31:

112.先在gan外延复合层20上,生长厚度为80nm的非交替层叠的algan外延工艺层31;

113.再在非交替层叠的algan外延工艺层31上,周期性循环交替生长单层厚度为5nm的algan外延工艺层32和单层厚度为0.8nm的mgny插入层33,循环周期中algan外延工艺层总厚度为algan复合层厚度的20%。

114.实施例5:

115.实施例3与实施例1的制备过程基本相同,区别仅在于步骤s31不同。

116.步骤s31:

117.先在gan外延复合层20上生长厚度为40nm的非交替层叠的algan外延工艺层31。

118.再在非交替层叠的algan外延工艺层31上,周期性循环交替生长单层厚度为5nm的algan外延工艺层32和单层厚度为0.8nm的mgny插入层33,循环周期中algan外延工艺层总厚度为algan复合层厚度的20%。

119.最后在交替层叠的algan外延工艺层32和mgny插入层33上生长厚度为40nm的非交替层叠的algan外延工艺层31。

120.分别对实施例1~5的algan外延结构进行bow值、表面粗糙度ra、(002)和102半峰宽测试,结果见表1:

121.表1

122.实施例bow/μmra/nm002/arsec102/arsec实施例1580.76242278实施例2573.97245276实施例3582.12248277实施例4595.89248279实施例5593.47247276

123.从表1数据可以看出:gan和algan交替层叠厚度主要影响algan外延结构表面的粗糙度,随着交叠层靠近外延结构表面,粗糙度逐渐增大,随着交叠层远离外延结构表面粗糙度逐渐减小,并且,外延结构的bow值和(002)和102半峰宽基本不随插入层的位置而变化,从而实现将表面粗化工艺从晶体质量工艺控制中单独分离出来,进而扩大了外延层表面粗化的外延生长工艺窗口,从而满足不同的外延技术需求。

124.对比例1:

125.对比例1与实施例1的制备过程基本相同,区别仅在于步骤s21和s31不同。

126.步骤s21中,gan外延复合层20未生长sin

x

插入层23。

127.步骤s31中,algan外延复合层30未生长mgny插入层33。

128.对比例2:

129.对比例1与实施例1的制备过程基本相同,区别仅在于步骤s21不同。

130.步骤s21中,循环周期中gan外延工艺层总厚度为gan复合层厚度的60%。

131.对比例3:

132.对比例1与实施例1的制备过程基本相同,区别仅在于步骤s21不同。

133.步骤s21中,循环周期中gan外延工艺层总厚度为gan复合层厚度的80%。

134.对比例4:

135.对比例2与实施例1的制备过程基本相同,区别仅在于步骤s31不同。

136.步骤s31中,循环周期中algan外延工艺层32总厚度为algan外延复合层30厚度的60%。

137.对比例5

138.步骤s31中,循环周期中algan外延工艺层32总厚度为algan外延复合层30厚度的80%。

139.分别对实施例1和对比例1~5的algan外延结构进行bow值、表面粗糙度ra、(002)和102半峰宽测试,结果见表2:

140.表2

141.实施例bow/μmra/nm002/arsec102/arsec实施例1580.76242278对比例1760.73297351对比例2620.68249281对比例3660.67254289对比例4680.77256291对比例5700.76262295

142.从上表可以看出,对比例1和实施例1采用光致发光pl测试得到algan外延结构的bow值(弯曲度)分别为58μm和76μm,从图7所示的algan外延结构的光学显微镜图片看出,实施例1的algan外延结构具有光滑的外延结构表面,并且xrd测试(002)和(102)半峰宽分别为242arsec和278arsec,而对比例1具有坑状缺陷分布,并且xrd测试(002)和(102)半峰宽分别为297arsec和351arsec,说明本发明gan和algan外延复合层结构具有更低bow值,即在采用本发明实施例1可以实现gan外延复合层和algan外延复合层的晶体匹配,为algan外延层提供高质量低应力的生长模板,能够获得具有低表面缺陷的高晶体质量algan外延层。

143.对比例2、3和对比例4、5中,循环周期中gan和algan外延工艺层厚度占比均大于二分之一(50%),从测试数据可以看出,对比例2、3和4、5中的bow值、(002)和(102)半峰宽都有增大趋势,说明所述gan外延复合层20中,交替层叠的所述gan外延工艺层22的总厚度不超过所述gan外延复合层20厚度的二分之一,所述algan外延复合层30中,交替层叠的所述algan外延工艺层32的总厚度不超过所述algan外延复合层30厚度的二分之一,sin

x

插入层23和mgny插入层33无法起到对gan外延工艺层和algan外延工艺层的晶格调整的作用;此外根据实际生产经验,当交替层叠的外延工艺层厚度超过二分之一时,表面粗糙度受到交叠层在非交叠层的插入位置的影响不明显,无法实现仅仅通过插入位置改变表面粗糙度的工艺。

144.尽管上面已经示出和描述了本发明的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本发明的限制,本领域的普通技术人员在不脱离本发明的原理和宗旨的情况下,在发明的范围内可以对上述实施例进行变化、修改、替换和变型,所有的这些改变都应该属于本发明权利要求的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1