半导体器件的制作方法

本公开涉及半导体器件。

背景技术:

1、为了满足对具有高性能、高速和/或多功能的半导体器件的日益增长的需求,需要具有更高集成度的半导体器件。在这点上,可能需要半导体器件来实现具有减小的图案之间的间隔距离的精细图案。此外,需要一种包括鳍式场效应晶体管(finfet)的半导体器件,该finfet具有允许完全去除牺牲层的三维沟道结构,以克服由平面金属氧化物半导体场效应晶体管(fet)的尺寸减小而引起的操作特性的限制。

技术实现思路

1、示例实施例提供了一种具有改进的可靠性的半导体器件。

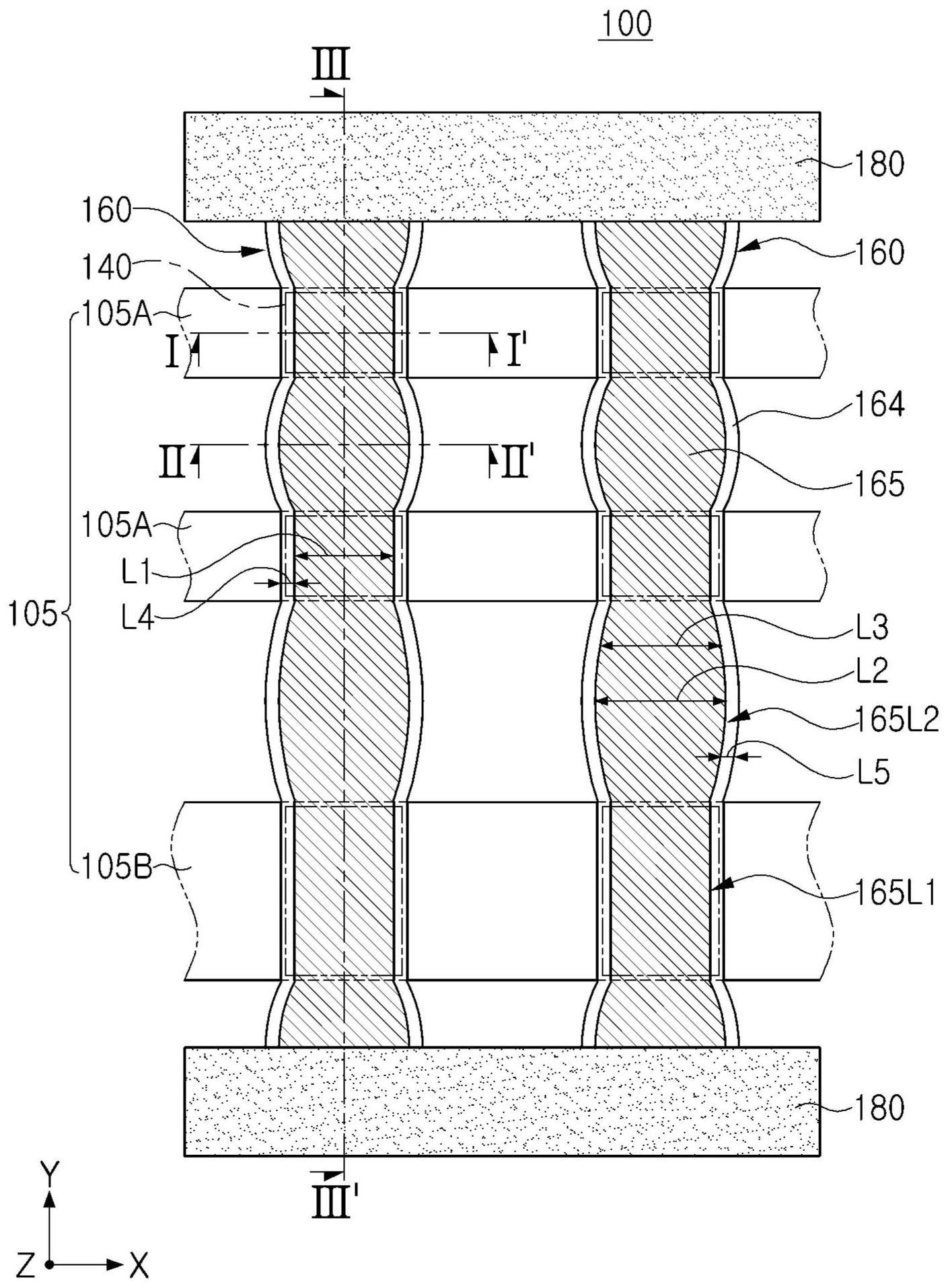

2、根据示例实施例,一种半导体器件包括:衬底,具有在第一方向上延伸的有源区;元件隔离层,在衬底中与有源区相邻;衬底上的栅电极,在与第一方向交叉的第二方向上延伸;有源区上的多个沟道层,沿垂直于衬底的上表面的第三方向彼此间隔开,并由栅电极围绕;以及源/漏区,设置在有源区的与栅电极相邻的凹陷中,并连接到多个沟道层。在第一方向上,栅电极在有源区上具有第一长度并在元件隔离层上具有第二长度,第二长度大于第一长度。

3、根据示例实施例,一种半导体器件包括:衬底,具有在第一方向上延伸的有源区;元件隔离层,在衬底中与有源区相邻;衬底上的栅电极,在与第一方向交叉的第二方向上延伸;有源区上的多个沟道层,沿垂直于衬底的上表面的第三方向彼此间隔开,并由栅电极围绕。在平面图中,在栅电极与元件隔离层重叠的区域中,栅电极具有凸侧表面。

4、根据示例实施例,一种半导体器件包括:衬底,具有在第一方向上延伸的有源区;衬底上的第一栅结构,在与第一方向交叉的第二方向上延伸;衬底上的第二栅结构,在第二方向上延伸;有源区上的多个沟道层,沿垂直于衬底的上表面的第三方向彼此间隔开,并由第一栅结构和第二栅结构中的每一个围绕;以及在第一栅结构与第二栅结构之间在有源区上的源/漏区,连接到多个沟道层。在第一方向上,第一栅结构在多个沟道层上具有第一长度并在多个沟道层的外侧具有第二长度,第二长度大于第一长度。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,其中,在平面图中,所述栅电极具有在所述有源区上沿所述第二方向线性延伸的第一侧表面和在所述元件隔离层上从所述第一侧表面凸出的第二侧表面。

3.根据权利要求2所述的半导体器件,其中,所述第一侧表面与所述第二侧表面之间的边界对应于所述有源区与所述元件隔离层之间的边界。

4.根据权利要求2所述的半导体器件,其中,所述第一侧表面与所述第二侧表面之间的边界在所述元件隔离层上,并与所述有源区与所述元件隔离层之间的边界间隔开。

5.根据权利要求1所述的半导体器件,其中,所述第二长度在所述第一长度的约1.1倍至约1.3倍的范围内。

6.根据权利要求1所述的半导体器件,还包括所述栅电极的侧面上的栅间隔物层,

7.根据权利要求1所述的半导体器件,还包括在所述有源区与所述栅电极之间以及所述元件隔离层与所述栅电极之间的栅介电层,

8.根据权利要求1所述的半导体器件,其中,所述有源区的上表面比所述元件隔离层的上表面离所述衬底的上表面更远。

9.根据权利要求1所述的半导体器件,其中,在所述栅电极沿所述第三方向与所述多个沟道层重叠的区域中,所述栅电极在所述第一方向上具有所述第一长度。

10.根据权利要求1所述的半导体器件,其中,所述多个沟道层在所述第三方向上不与所述元件隔离层重叠。

11.根据权利要求1所述的半导体器件,其中,在所述栅电极具有所述第二长度的区域中,所述栅电极在所述第三方向上不与所述有源区重叠。

12.根据权利要求1所述的半导体器件,还包括所述栅电极的侧面上的栅分离层。

13.根据权利要求1所述的半导体器件,还包括在所述栅电极与所述源/漏区之间的间隔物层。

14.一种半导体器件,包括:

15.根据权利要求14所述的半导体器件,其中,在平面图中,在所述栅电极与所述有源区重叠的区域中,所述栅电极具有在所述第二方向上线性延伸的侧表面。

16.根据权利要求14所述的半导体器件,其中,所述栅电极具有基于其在所述第一方向上的中心的对称形状。

17.根据权利要求14所述的半导体器件,其中,在所述第一方向上,在所述栅电极沿所述第三方向与所述有源区重叠的区域中所述栅电极具有第一长度,并且在所述栅电极与所述元件隔离层重叠的区域中所述栅电极具有第二长度,所述第二长度大于所述第一长度。

18.根据权利要求17所述的半导体器件,其中,在所述栅电极与所述元件隔离层重叠的区域中,所述栅电极包括在所述第一方向上具有不同长度的多个区域,并且

19.一种半导体器件,包括:

20.根据权利要求19所述的半导体器件,其中,在所述第一方向上,所述第二栅结构在所述多个沟道层上具有第三长度并在所述多个沟道层的外侧具有第四长度,所述第四长度基本上等于所述第三长度。

技术总结

提供一种半导体器件。该半导体器件包括:衬底,具有在第一方向上延伸的有源区;元件隔离层,在衬底中与有源区相邻;衬底上的栅电极,在与第一方向交叉的第二方向上延伸;有源区上的多个沟道层,沿垂直于衬底的上表面的第三方向彼此间隔开,并由栅电极围绕;以及源/漏区,设置在有源区的与栅电极相邻的凹陷中,并连接到多个沟道层。在第一方向上,栅电极在有源区上具有第一长度并在元件隔离层上具有第二长度,第二长度大于第一长度。

技术研发人员:孙珍景,金承帝,朴志源,林在抱,曹玟锡,林升炫,崔津荣

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!