三维半导体设备和制造该三维半导体设备的方法与流程

各种实施例总体上涉及一种半导体设备和制造该半导体设备的方法,更具体地,涉及一种三维半导体设备和制造该三维半导体设备的方法。

背景技术:

1、半导体设备的集成度主要取决于单位存储器单元的占用面积。近来,由于包括衬底上的单个存储器单元的半导体设备的集成度的提高可能已经达到极限,可以提出包括堆叠在衬底上的存储器单元的三维(3d)半导体设备。此外,为了提高3d半导体设备的操作可靠性,可以开发各种结构和制造方法。

技术实现思路

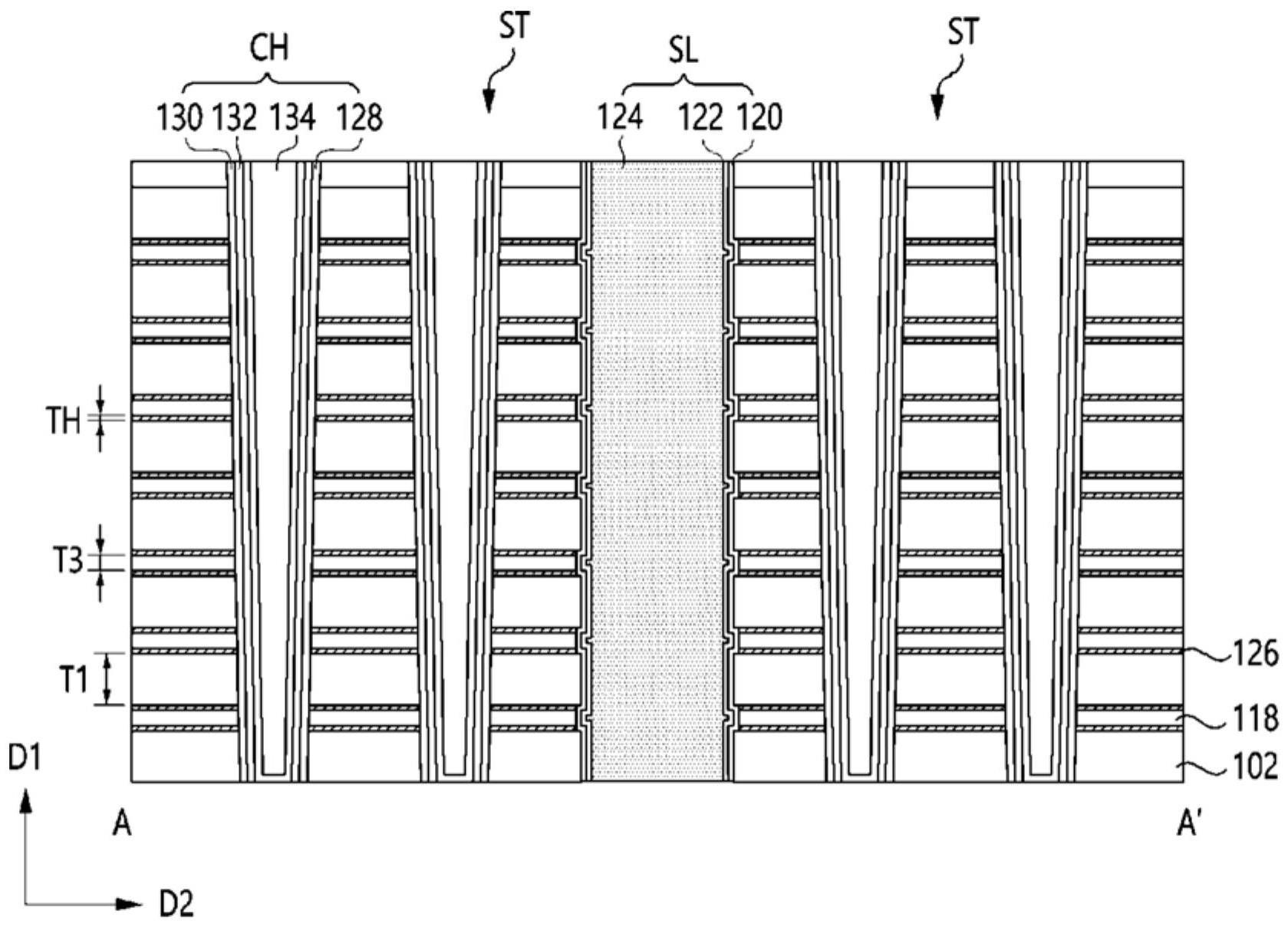

1、根据多个实施例的示例,可以提供一种三维(3d)半导体设备。3d半导体设备可以包括至少一个堆叠结构和至少一个竖直通道结构。堆叠结构可以包括顺序地堆叠的第一绝缘图案、下部导电图案和第二绝缘图案。第一绝缘图案可以包括第一厚度,并且第二绝缘图案可以包括与第一厚度不同的第二厚度。下部导电图案中的每一个的上部表面可以与第二绝缘图案中的每一个的下部表面直接接触。

2、根据多个实施例的示例,可以提供一种三维(3d)半导体设备。3d半导体设备可以包括堆叠结构和至少一个竖直通道结构。堆叠结构可以包括至少一个单元存储器块。单元存储器块可以包括在单元区域和接触区中顺序地堆叠至少一次的第一绝缘图案、下部字线、第二绝缘图案和上部字线。竖直通道结构可以包括在单元区域中穿过堆叠结构形成的数据存储层。单元区域中的第一绝缘图案可以具有比单元区域中的第二绝缘图案的厚度更厚的厚度。

3、根据多个实施例的示例,可以提供一种制造3d半导体设备的方法。在制造3d半导体设备的方法中,第一绝缘中间层和牺牲层可以交替地堆叠至少一次以形成堆叠结构。可以选择性地去除牺牲层以在第一绝缘中间层之间形成开口。可以在开口的内部表面上形成导电层。可以在具有导电层的开口中形成第二绝缘中间层。第二绝缘中间层可以具有与第一绝缘中间层的厚度不同的厚度。可以形成穿过堆叠结构的孔。可以去除通过孔暴露的导电层以限定字线。可以在孔中形成竖直通道结构。

技术特征:

1.一种三维3d半导体设备,包括:

2.根据权利要求1所述的3d半导体设备,其中所述堆叠结构还包括与所述第二绝缘图案的上部表面直接接触的上部导电图案。

3.根据权利要求2所述的3d半导体设备,其中所述上部导电图案包括与所述下部导电图案的材料和厚度基本上相同的材料和厚度。

4.根据权利要求2所述的3d半导体设备,其中所述下部导电图案通过切口部分与所述上部导电图案电隔离。

5.根据权利要求4所述的3d半导体设备,其中所述切口部分位于所述第二绝缘图案的端部的上部表面处。

6.根据权利要求1所述的3d半导体设备,其中所述第一厚度比所述第二厚度更厚。

7.根据权利要求6所述的3d半导体设备,

8.根据权利要求1所述的3d半导体设备,其中所述下部导电图案包括钼。

9.根据权利要求1所述的3d半导体设备,其中所述下部导电图案包括被堆叠的阻挡层和导电层,

10.根据权利要求1所述的3d半导体设备,其中所述第一绝缘图案和所述第二绝缘图案包括从相同的材料和不同的材料中选择的一种。

11.根据权利要求10所述的3d半导体设备,其中所述第一绝缘图案和所述第二绝缘图案中的至少一个包括以下项中的至少一种:氧化物,包括氧化硅和包含金属的氧化物;氮化物,包括氮化硅和氮氧化硅;绝缘材料,包括杂质;以及气隙。

12.一种3d半导体设备,包括:

13.根据权利要求12所述的3d半导体设备,其中所述上部字线和所述下部字线中的每一个具有比所述第二绝缘图案的厚度更薄的厚度。

14.根据权利要求13所述的3d半导体设备,其中所述第一绝缘图案具有比所述下部字线的厚度、所述第二绝缘图案的厚度和所述上部字线的厚度之和更厚的厚度。

15.根据权利要求12所述的3d半导体设备,其中所述上部字线和所述下部字线中的至少一个包括钼。

16.根据权利要求12所述的3d半导体设备,其中所述上部字线和所述下部字线中的每一个包括阻挡层和导电层,所述阻挡层与所述第一绝缘图案的上部表面接触,并且所述导电层与所述第二绝缘图案的上部表面接触。

17.根据权利要求12所述的3d半导体设备,其中所述第一绝缘图案和所述第二绝缘图案包括相同的材料和不同的材料中的一种。

18.根据权利要求12所述的3d半导体设备,其中所述接触区中的所述第二绝缘图案具有比所述单元区域中的所述第二绝缘图案的厚度更厚的厚度。

19.根据权利要求18所述的3d半导体设备,其中被布置在所述第二绝缘图案的上部表面上的所述上部字线和被布置在所述第二绝缘图案的下部表面上的所述下部字线通过所述第二绝缘图案的所述上部表面处的切口部分被电隔离,以及

20.根据权利要求19所述的3d半导体设备,还包括:

21.根据权利要求12所述的3d半导体设备,其中所述竖直通道结构还包括至少一个突出部分,所述至少一个突出部分被布置在与所述第二绝缘图案相对应的所述竖直通道结构的外部表面处。

22.一种制造3d半导体设备的方法,所述方法包括:

23.根据权利要求22所述的方法,其中所述第一绝缘中间层和所述第二绝缘中间层中的至少一个包括以下项中的至少一种:氧化物,包括氧化硅和包含金属的氧化物;氮化物,包括氮化硅和氮氧化硅;绝缘材料,包括杂质;以及气隙。

24.根据权利要求22所述的方法,其中所述牺牲层具有比所述第一绝缘中间层的厚度与所述导电层的厚度的两倍之和更厚的厚度。

25.根据权利要求22所述的方法,其中形成所述导电层包括在所述开口的所述内部表面上形成钼层。

26.根据权利要求22所述的方法,其中形成所述导电层包括:

27.根据权利要求23所述的方法,其中所述堆叠结构包括单元区域和所述单元区域外部的接触区,所述单元区域包括所述竖直通道结构,

28.根据权利要求27所述的方法,还包括:

29.根据权利要求28所述的方法,还包括:

技术总结

本公开的实施例涉及三维半导体设备和制造该三维半导体设备的方法。3D半导体设备可以包括堆叠结构和竖直通道结构。堆叠结构可以包括第一绝缘图案、下部导电图案和第二绝缘图案。下部导电图案可以被布置在第一绝缘图案上。第二绝缘图案可以被布置在下部导电图案上。第一绝缘图案可以具有比第二绝缘图案的厚度更厚的厚度。竖直通道结构可以被布置在堆叠结构中。下部导电图案可以具有与第二绝缘图案的下部表面直接接触的上部表面。

技术研发人员:李昇珉,安正烈

受保护的技术使用者:爱思开海力士有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!