一种2004nmPIN光电探测器及其制备方法与流程

本发明涉及光电探测器,具体来说涉及一种2004nm pin光电探测器及其制备方法。

背景技术:

1、相比于传统的电化学法,利用激光光谱法(tdls)进行二氧化碳探测可以大幅度降低系统的成本。二氧化碳对于2004nm的激光具有较强的吸收,因此,用于二氧化碳探测的光电探测器需要在宽温度区间内对于2004nm的激光具有较强的响应度。传统的ingaas pin探测器的in组分为53%,ingaas吸收层和inp衬底晶格匹配。这样有助于降低吸收层的位错,从而降低器件的暗电流。传统ingaas pin探测器的室温截止波长约为1700nm,对于2004nm光线的响应度为0。

2、因此,需要对传统的ingaas pin光电探测器进行改进,从而保证其在宽温度区间(-40-85℃)内对2004nm的光线都具有较强的响应度。考虑到探测器可能的低温应用场景,因此,该类型探测器的室温截止波长至少要到2100nm。为了提高ingaas材料的截止波长,需要提高ingaas材料中in的组分。2100nm截止波长对应的in组分为70%。而in组分的增加会造成ingaas材料晶格常数的增大,从而与inp衬底不再晶格匹配。in0.7ga0.3as与inp衬底的晶格失配达到了1.15%。如果在inp衬底上直接生长in0.7ga0.3as材料,会造成in0.7ga0.3as吸收层中产生非常高的位错密度,从而造成探测器的高暗电流。、

3、现有的技术方案中,一般需要通过引入多层的组分渐变异变缓冲层来实现从inp衬底到ingaas吸收层的晶格常数变化。在多层组分渐变的异变缓冲层中,相邻2层的in组分差距不能太大,否则会引入过高的位错密度;而每层的厚度又必须超过其晶格弛豫的临界厚度,否则由于晶格常数差距而造成的压应变不能得到有效释放。综合上述两点,整个多层组分渐变异变缓冲层的厚度会变得很厚。比如,为了在inp衬底上异变生长截止波长为2100nm的ingaas材料,通常需要10层以上的异变缓冲层,整体厚度超过6μm。这样就极大的增加了外延材料的生长成本。

技术实现思路

1、为了解决上述技术方案的不足,本发明的目的在于提供一种2004nm pin光电探测器的制备方法。

2、本发明的另一目的在于提供上述制备方法制备的2004nm pin光电探测器。

3、本发明的目的是通过下述技术方案予以实现的。

4、一种2004nm pin光电探测器的制备方法,包括以下步骤:

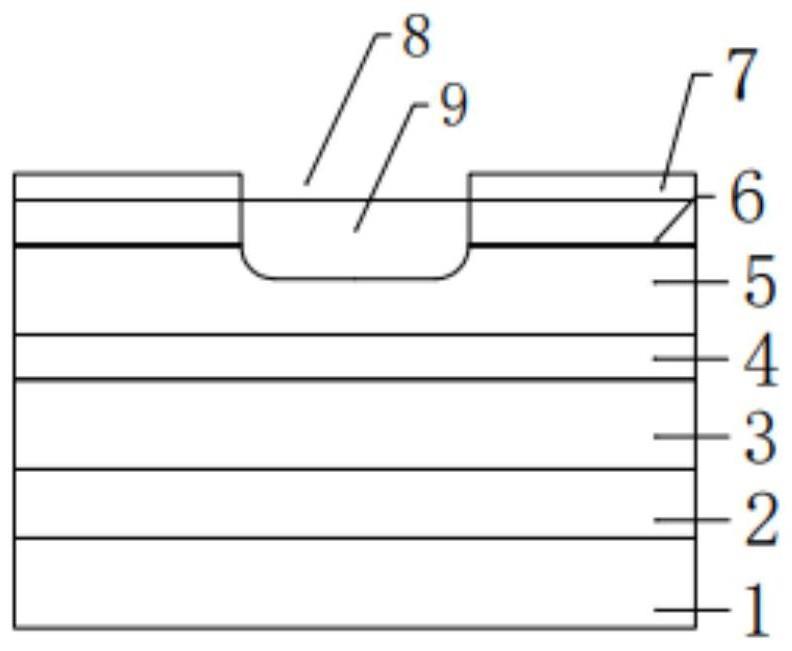

5、步骤一:利用mocvd或者mbe的沉积方式在n型inp衬底上依次生长n型inp缓冲层、n型ingaas抛物线异变缓冲层、n型ingaas组分回退层、非故意掺杂型ingaas吸收层和非故意掺杂inasp盖层;

6、步骤二:利用pecvd的淀积方式在所述非故意掺杂inasp盖层的上表面沉积sin薄膜;

7、步骤三:利用光刻胶在所述sin薄膜的表面形成zn扩散窗口图形,利用刻蚀的方法去除zn扩散窗口图形上的所述sin薄膜,以使下方的所述非故意掺杂inasp盖层暴露出来,刻蚀完成后去除光刻胶,形成zn扩散窗口;

8、步骤四:利用mocvd或者炉管法在所述zn扩散窗口区域进行zn扩散,形成p-型zn扩散区域;

9、步骤五:利用pecvd的淀积方式在所有裸露在外的上表面沉积sin减反膜;

10、步骤六:利用光刻胶在所述p-型zn扩散区域上方的sin减反膜上形成via孔洞图形,利用刻蚀的方法去除via孔洞图形上的sin减反膜,得到via孔洞,使得下方的p-型zn扩散区域暴露出来,刻蚀完成后去除光刻胶,在p-型zn扩散区域上表面形成金属接触孔洞;

11、步骤七:利用光刻胶在所述via孔洞的上方形成p金属图形,利用电子束蒸发或者磁控溅射蒸镀金属并进行金属剥离,退火,得到p金属电极,p金属电极和p-型zn扩散区域的上表面接触为欧姆接触;

12、步骤八:在所述在n型inp衬底的背面进行减薄和抛光;

13、步骤九:利用电子束蒸镀或者磁控溅射的方法在所述n型inp衬底的背面制备n金属电极,并退火形成欧姆接触。

14、在上述技术方案中,在步骤一中,n型inp缓冲层的厚度为0.5~2μm,掺杂浓度为1×1017/cm3~2×1018/cm3。

15、在上述技术方案中,在步骤一中,在步骤一中,n型ingaas抛物线异变缓冲层中in组分从53%开始,自下而上按照开口向下的抛物线函数增加至70%-85%,所述n型ingaas抛物线异变缓冲层的厚度为1~5μm。

16、在上述技术方案中,在步骤一中,n型ingaas组分回退层中in组分小于n型ingaas抛物线异变缓冲层最上方in组分,其差值为1%~10%,n型ingaas组分回退层的厚度为1~5μm。

17、在上述技术方案中,在步骤一中,非故意掺杂型ingaas吸收层与n型ingaas组分回退层的晶格常数相同,非故意掺杂型ingaas吸收层中in组分大于等于70%,其室温荧光(pl)波长大于等于2100nm,其室温截止波长大于2004nm,在-40℃下对于2004nm光线的响应度不低于0.5a/w。

18、在上述技术方案中,在步骤二中,所述sin薄膜的厚度为100~500nm。

19、在上述技术方案中,在步骤三中,zn扩散窗口为圆形或者方形,其直径或边长均为10~5000μm。

20、在上述技术方案中,在步骤四中,p-型zn扩散区域自上而下依次从非故意掺杂inasp盖层的上表面到非故意掺杂型ingaas吸收层内,其中,在非故意掺杂型ingaas吸收层的深度为0.1~0.5μm。

21、在上述技术方案中,在步骤五中,sin减反膜对于2004nm波长光线的反射率大于等于70%。

22、在上述技术方案中,步骤八中,减薄、抛光后所述n型inp衬底的厚度为50~200μm。

23、上述制备方法获得的2004nm pin光电探测器。

24、本发明的优点和有益效果为:

25、1.本发明的探测器in组分呈抛物线函数变化的异变缓冲层可以在较薄的厚度(小于2μm)内实现晶格常数从inp衬底到ingaas吸收层的变化,并将大部分的位错限制在异变缓冲层的底部区域。ingaas抛物线异变缓冲层起到了扩展inp衬底晶格常数的作用,用于适用在其上部生长的材料与inp衬底之间的晶格不匹配。

26、2.本发明的探测器的n型ingaas组分回退层的晶格常数与ingaas非故意掺杂吸收层的晶格常数一致。ingaas组分回退层,可以进一步平衡异变缓冲层中未完全释放的长应力,从而为上层ingaas吸收层的生长提供了一种“虚拟衬底”,从而可以在其上进行高质量的高in组分的ingaas吸收层的生长。

27、3.本发明的目的在于提供一种in组分成抛物线函数变化的异变缓冲层和一层组分回退层。相比于传统的组分渐变多层异变缓冲层,in组分成抛物线函数变化的异变缓冲层可以在较薄的厚度(小于2μm)内实现晶格常数从n型inp衬底到ingaas吸收层的变化,并将大部分的位错限制在异变缓冲层的底部区域。其上生长的ingaas组分回退层,可以进一步平衡异变缓冲层中未完全释放的长应力,从而为上层ingaas吸收层的生长提供了一种“虚拟衬底”,从而可以在其上进行高质量的高in组分的ingaas吸收层的生长。

- 还没有人留言评论。精彩留言会获得点赞!