屏蔽栅沟槽半导体器件的沟槽结构、制作方法及仿真方法与流程

本发明涉及半导体器件,更具体地说是指屏蔽栅沟槽半导体器件的沟槽结构、制作方法及仿真方法。

背景技术:

1、沟槽型双层栅半导体场效应管作为一种功率器件,具有击穿电压高,导通电阻低,开关速度快的特点。屏蔽栅沟槽型半导体场效应管的结构其沟槽分为上下两部分,沟槽下半部填充多晶硅形成屏蔽栅。半导体场效应管最主要的研究方向就是不断降低功耗,包括导通损耗和开关损耗。屏蔽栅沟槽半导体场效应管的输出电容coss为栅漏电容cgd和栅源电容cgs之和;较大的输出电容会引起瞬态响应下较长的关断时间,引起较高的开关损耗,因此输出电容成为了限制器件工作频率和开关损耗的主要因素之一,须设法减小沟槽型半导体场效应管的输出电容coss。然而随着技术的发展,系统端对器件提出了不同性能需求,比如在同步整流电路中,为了进一步提升系统效率,上管需要开关更快的半导体场效应管器件,而下管偏重需要更低导通内阻的器件。

2、目前降低功耗技术中则是更多的通过技术提升来减小芯片面积和增加栅氧厚度等方法。但此种方式不仅会改变器件本身的结构和尺寸,还会带来其它器件性能变化,且阈值电压会漂移,稳定性不高。

3、因此,有必要设计一种新的制作方法,实现不用改变器件的结构与尺寸,优化器件的动态参数,减少屏蔽栅沟槽半导体场效应管的输出电容,降低功耗以获得功率半导体器件性能的提升。

技术实现思路

1、本发明的目的在于克服现有技术的缺陷,提供屏蔽栅沟槽半导体器件的沟槽结构、制作方法及仿真方法。

2、为实现上述目的,本发明采用以下技术方案:屏蔽栅沟槽半导体器件的沟槽结构的制作方法,包括:

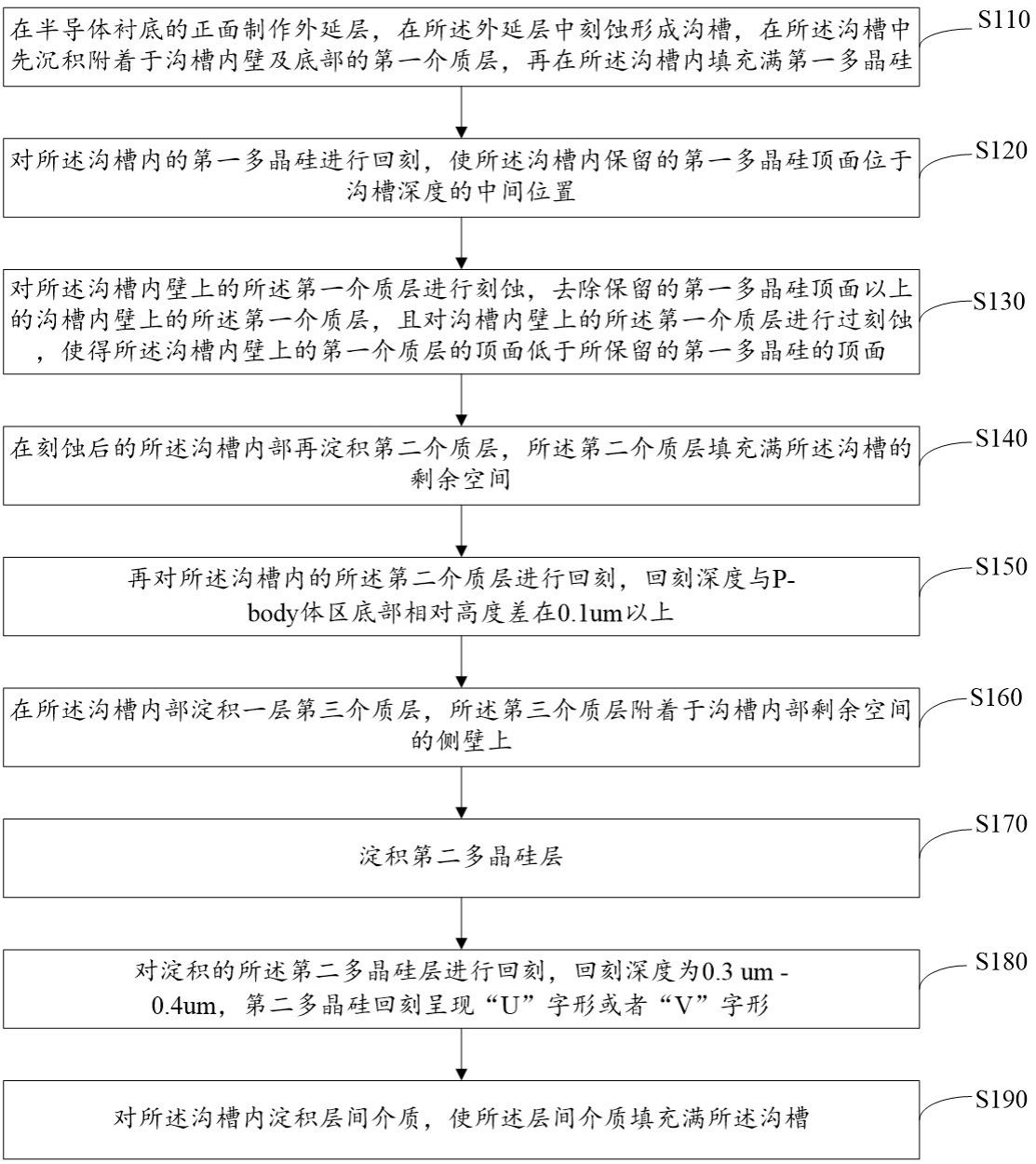

3、在半导体衬底的正面制作外延层,在所述外延层中刻蚀形成沟槽,在所述沟槽中先沉积附着于沟槽内壁及底部的第一介质层,再在所述沟槽内填充满第一多晶硅;

4、对所述沟槽内的第一多晶硅进行回刻,使所述沟槽内保留的第一多晶硅顶面位于沟槽深度的中间位置;

5、对所述沟槽内壁上的所述第一介质层进行刻蚀,去除保留的第一多晶硅顶面以上的沟槽内壁上的所述第一介质层,且对沟槽内壁上的所述第一介质层进行过刻蚀,使得所述沟槽内壁上的第一介质层的顶面低于所保留的第一多晶硅的顶面;

6、在刻蚀后的所述沟槽内部再淀积第二介质层,所述第二介质层填充满所述沟槽的剩余空间;

7、再对所述沟槽内的所述第二介质层进行回刻,回刻深度与p-body体区底部相对高度差在0.1um以上;

8、在所述沟槽内部淀积一层第三介质层,所述第三介质层附着于沟槽内部剩余空间的侧壁上;

9、淀积第二多晶硅层;

10、对淀积的所述第二多晶硅层进行回刻,回刻深度为0.3 um -0.4um,第二多晶硅回刻呈现“u”字形或者“v”字形;

11、对所述沟槽内淀积层间介质,使所述层间介质填充满所述沟槽。

12、其进一步技术方案为:所述第一多晶硅的回刻深度为1.1 um ~1.8um。

13、其进一步技术方案为:所述对所述沟槽内壁上的所述第一介质层进行刻蚀,去除保留的第一多晶硅顶面以上的沟槽内壁上的所述第一介质层,且对沟槽内壁上的所述第一介质层进行过刻蚀,使得所述沟槽内壁上的第一介质层的顶面低于所保留的第一多晶硅的顶面的步骤中,所述沟槽内壁上的第一介质层的顶面低于所保留的第一多晶硅的顶面0.05um至0.1um。

14、其进一步技术方案为:所述对所述沟槽内淀积层间介质,使所述层间介质填充满所述沟槽,包括:

15、所述层间介质沉积在所述沟槽中,所述第二多晶硅位于所述层间介质两侧,形成栅极结构。

16、本发明还提供了屏蔽栅沟槽半导体器件的沟槽结构,其特征在于,所述沟槽结构由上述的屏蔽栅沟槽半导体器件的沟槽结构的制作方法制作而成,所述沟槽结构包括半导体衬底,所述半导体衬底上设有外延层;所述外延层中设有沟槽,所述沟槽中设置有屏蔽栅结构以及栅极结构,所述屏蔽栅结构位于所述栅极结构的下方;

17、所述屏蔽栅结构包括位于所述沟槽内的第一介质层及第一多晶硅,其中,所述第一介质层置于所述第一多晶硅与所述沟槽的内壁之间,所述第一介质层呈u字形设置,所述第一介质层包裹所述第一多晶硅;

18、所述栅极结构包括u型第二多晶硅以及栅氧化层,所述u型第二多晶硅分别位于沟槽中的靠近沟槽内壁的两侧;所述u型第二多晶硅与沟槽的内壁之间设置有所述栅氧化层;

19、所述沟槽内还设有层间介质,所述层间介质将所述沟槽填满,且所述层间介质位于所述u型第二多晶硅之间的沟槽中。

20、其进一步技术方案为:所述层间介质的横向宽度大于所述第一多晶硅的横向宽度。

21、其进一步技术方案为:所述第一介质层的顶面低于所述第一多晶硅的顶面0.05um至0.1um。

22、其进一步技术方案为:所述外延层内设有p-body体区,所述第二介质层的顶面与p-body体区底部相对高度差在0.1um以上;所述屏蔽栅结构与所述栅极结构之间连接有第二介质层。

23、本发明还提供了屏蔽栅沟槽半导体器件的沟槽结构的仿真方法,包括:

24、获取上述的屏蔽栅沟槽半导体器件的沟槽结构的相关信息以及上述的屏蔽栅沟槽半导体器件的沟槽结构的制作方法的相关信息;

25、对所述沟槽结构分割为两个完全对称的结构,以得到待仿真结构;

26、从预设代码库中选取与所述屏蔽栅沟槽半导体器件的沟槽结构的制作方法对应的仿真代码,并利用所述仿真代码以及所述待仿真结构的正面结构的区域参数对所述待仿真结构的正面结构进行结构仿真,以生成正面仿真模块;

27、根据所述待仿真结构的背面结构进行平面结构仿真,得到背面仿真模块;

28、将所述正面仿真模块与所述背面仿真模块进行整合,得到待仿真沟槽结构;

29、采用历史经验法对所述待仿真沟槽结构对应的正面仿真模块的虚拟网格密度进行优化调整,得到调整后的待仿真沟槽结构;

30、根据预置的运行规则对调整后的待仿真沟槽结构进行仿真运行,以得到所述待仿真沟槽结构的仿真电学性能参数。

31、其进一步技术方案为:采用历史经验法对所述待仿真沟槽结构对应的正面仿真模块的虚拟网格密度进行优化调整,得到调整后的待仿真沟槽结构,包括:

32、根据已存的历史数据查找出与所述待仿真沟槽结构对应的正面结构最接近一致的历史虚拟网格密度,并按所述历史虚拟网格密对所述待仿真沟槽结构对应的正面仿真模块的虚拟网格密度进行优化调整,得到调整后的待仿真沟槽结构。

33、本发明与现有技术相比的有益效果是:本发明通过优化p型体区底部与栅极多晶硅底部的高度差降低cgd, 同时通过工艺参数控制栅极多晶硅回刻深度减小cgs, 不用新增其他光罩,兼容现有屏蔽栅沟槽功率半导体器件常规流程,从而达到提高开关频率,降低功耗,实现不用改变器件的结构与尺寸,优化器件的动态参数,减少屏蔽栅沟槽半导体场效应管的输出电容,降低功耗以获得功率半导体器件性能的提升。

34、下面结合附图和具体实施例对本发明作进一步描述。

- 还没有人留言评论。精彩留言会获得点赞!