上电复位信号发生装置的制作方法

各种实施方式总体上涉及半导体集成电路技术,并且更具体地,涉及上电复位信号发生装置。

背景技术:

半导体设备通过从外部电源供给电源电压而操作。当半导体设备被提供电源电压时,半导体设备执行上电操作。当电源电压的电压电平变得稳定时,半导体设备使能上电复位信号。当上电复位信号被使能时,半导体设备初始化内部电路并为正常操作做准备。当对半导体设备的电源电压供给中断时,半导体设备执行断电操作。当电源电压的电压电平下降到预定电平以下或更低电平时,半导体设备禁用上电复位信号。

半导体设备检测电源电压的电平以生成上电复位信号。然而,从外部电源提供的电源电压不可避免地伴有噪声。因此,在上电时段或断电时段期间,电源电压的电压电平停留在作为稳定的基准的目标电压电平附近,同时相对于目标电压电平反复上下波动。由于电源电压的这种噪声,当电源电压达到目标电压电平附近时,上电复位信号变为使能和/或禁用,然后变为禁用和/或使能,这引发上电复位信号的毛刺(glitch)。上电复位信号的毛刺导致半导体设备故障。

技术实现要素:

根据一个实施方式,一种上电复位信号发生装置可以包括基准电压发生器、信号驱动器和稳定电路。基准电压发生器可以检测电源电压的电压电平以生成上电基准电压。信号驱动器可以驱动上电基准电压以生成上电复位信号。稳定电路可以在上电复位信号被使能时保持上电复位信号在预定量时间期间被使能,并且可以在上电复位信号被禁用时防止上电复位信号在预定量时间期间被使能。

根据一个实施方式,一种上电复位信号发生装置可以包括基准电压发生器、信号驱动器和稳定电路。基准电压发生器可以基于电源电压的电压电平来生成上电基准电压。信号驱动器可以驱动上电基准电压以生成上电复位信号。稳定电路可以接收反馈的上电复位信号,以继续保持上电基准电压的电压电平,而与电源电压的电压电平波动无关。

根据一个实施方式,一种上电复位信号发生装置可以包括基准电压发生器、信号驱动器和稳定电路。基准电压发生器可以检测电源电压的电压电平以生成上电基准电压。信号驱动器可以驱动上电基准电压以生成在电源电压等于或大于目标电压电平时被使能的上电复位信号。稳定电路可以在上电复位信号从禁用状态转变为使能状态之后,即使电源电压在预定量时间期间小于目标电压,也使上电复位信号在预定量时间期间保持使能状态。

附图说明

图1是例示了根据一个实施方式的上电复位信号发生装置的配置的图;

图2是例示了图1所示的上电复位信号发生装置的操作的图;

图3是例示了图1所示的上电复位信号发生装置的另一操作的图;

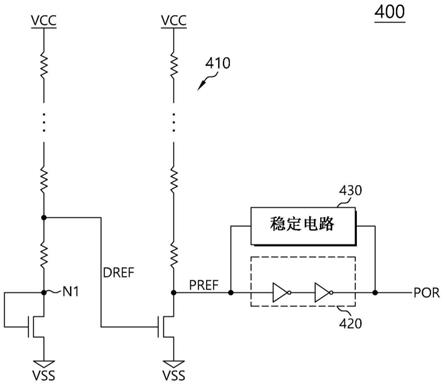

图4是例示了根据一个实施方式的上电复位信号发生装置的配置的图;

图5是例示了图4所示的稳定电路的配置的图;

图6是例示了根据一个实施方式的控制信号发生器的配置的图;

图7是示出图6所示的控制信号发生器的操作的时序图;

图8是例示了在上电时段期间根据实施方式的上电复位信号发生装置的操作的时序图;

图9是例示了在断电时段期间根据实施方式的上电复位信号发生装置的操作的时序图;以及

图10是例示了在断电时段期间图5所示的稳定电路的另一操作的时序图。

具体实施方式

图1是例示了根据一个实施方式的上电复位信号发生装置100的配置的图。参照图1,上电复位信号发生装置100可以接收电源电压vcc,并且可以检测电源电压vcc的电压电平以生成上电复位信号por。上电复位信号发生装置100可以检测上电状态以使能上电复位信号por,并且可以检测断电状态以禁用上电复位信号por。在上电状态下,可以从外部电源提供电源电压vcc,并且电源电压vcc的电压电平可以升高以达到目标电压电平或更高的电压电平。当电源电压vcc的电压电平升高以达到目标电压电平或更高的电压电平时,电源电压vcc的电压电平可以被确定为稳定的。在断电状态下,来自外部电源的电源电压vcc的供应可以被中断,并且电源电压vcc的电压电平可以下降到目标电压电平以下。当电源电压vcc的电压电平升高以达到目标电压电平或更高的电压电平时,上电复位信号发生装置100可以使能上电复位信号por。当电源电压vcc的电压电平停留在目标电压电平或更高的电压电平时,上电复位信号发生装置100可以使上电复位信号por保持在使能状态。当电源电压vcc的电压电平下降到目标电压电平以下时,上电复位信号发生装置100可以禁用上电复位信号por为禁用状态。

上电复位信号发生装置100可以包括基准电压发生器110和信号驱动器120。基准电压发生器110可以检测电源电压vcc的电压电平以生成上电基准电压pref。当电源电压vcc的电压电平升高以达到目标电压电平或更高的电压电平时,基准电压发生器110可以降低上电基准电压pref,使得上电基准电压pref的电压电平可以被确定为逻辑低电平。当电源电压vcc的电压电平停留在目标电压电平或更高的电压电平时,基准电压发生器110可以将上电基准电压pref保持在能够被确定为上电基准电压pref的逻辑低电平的电压电平。当电源电压vcc的电压电平下降到目标电压电平以下时,基准电压发生器110可以改变上电基准电压pref,使得上电基准电压pref的电压电平能够被确定为逻辑高电平。基准电压发生器110可以通过多个电阻对电源电压vcc进行分压,以从一个或更多个分压的电压生成检测电压dref。当检测电压dref的电压电平变为目标电压电平或更大的电压电平时,基准电压发生器110可以通过接地电压来驱动上电基准电压pref。当检测电压dref的电压电平变得低于目标电压电平时,基准电压发生器110可以将上电基准电压pref驱动到电源电压vcc。

信号驱动器120可以接收上电基准电压pref以生成上电复位信号por。信号驱动器120可以驱动上电基准电压pref以生成上电复位信号por。在实施方式中,信号驱动器120可以非反相驱动(non-inversion-drive)上电基准电压pref以生成上电复位信号por。例如,信号驱动器120可以包括偶数个反相器,并且可以通过偶数个反相器依次反相驱动上电基准电压pref,以生成上电复位信号por。例如,如图1所示,信号驱动器120可以包括第一反相器121和第二反相器122。第一反相器121可以接收上电基准电压pref,可以将上电基准电压pref反相,并且可以输出反相的上电基准电压pref。第二反相器122可以接收第一反相器121的输出,可以将第一反相器121的输出反相并且可以输出上电复位信号por。在实施方式中,信号驱动器120可以包括奇数个反相器,以反相驱动上电基准电压pref来生成上电复位信号por。在这种情况下,从信号驱动器120输出的上电复位信号por可以被使能为另一逻辑电平。

基准电压发生器110可以包括第一分压器111、第二分压器112、二极管晶体管113和触发晶体管114。第一分压器111和第二分压器112可以具有彼此相同的配置。第一分压器111可以包括串联联接在被提供电源电压vcc的节点与第一节点n1之间的多个电阻器。多个电阻器可以具有彼此相同的电阻值。检测电压dref可以从彼此串联联接的多个电阻器当中的任意两个电阻器之间的节点nr输出。可以任意选择用于指定节点nr的两个电阻器之间的位置,以改变目标电压电平。例如,随着两个被选电阻器越靠近被提供电源电压vcc的节点,目标电压电平可以变得越高。相反,随着两个被选电阻器越靠近第一节点n1,目标电压电平可以变得越低。二极管晶体管113可以联接在第一节点n1与被提供接地电压vss的节点之间。例如,二极管晶体管113可以是n沟道mos晶体管。二极管晶体管113的栅极和漏极可以联接至第一节点n1,并且其源极可以联接至被提供接地电压vss的节点。二极管晶体管113可以允许稳定量的电流从第一节点n1和被提供接地电压vss的节点流过。

第二分压器112可以包括串联联接在被提供电源电压vcc的节点与第二节点n2之间的多个电阻器。第二分压器112中所包括的电阻器的数量可以与第一分压器111中所包括的电阻器的数量相同。第二分压器112中所包括的每个电阻器的电阻值可以与第一分压器111中所包括的每个电阻器的电阻值相同。可以从第二节点n2输出上电基准电压pref。触发晶体管114可以联接在第二节点n2与被提供接地电压vss的节点之间。触发晶体管114可以接收检测电压dref。例如,触发晶体管114可以是n沟道mos晶体管。触发晶体管114的栅极可以接收检测电压dref,其漏极可以联接到第二节点n2,并且其源极可以联接到被提供接地电压vss的节点。当检测电压dref具有高的足以使触发晶体管114导通的电压电平时,触发晶体管114可以导通,并且上电基准电压pref可以被驱动为接地电压vss。当检测电压dref具有低的不足以使触发晶体管114导通的电压电平时,触发晶体管114可以截止,并且上电基准电压pref可以由电源电压vcc驱动。

图2是例示了图1所示的上电复位信号发生装置100的操作的图。在下文中参照图1和图2所描述的将是上电复位信号发生装置100的操作。当从外部电源提供电源电压vcc时,电源电压vcc的电压电平可以逐渐变高。随着电源电压vcc的电压电平逐渐变高,第一节点n1、检测电压dref和上电基准电压pref的电压电平可以升高。随着检测电压dref的电压电平升高,流过触发晶体管114的电流量可以变大。随着上电基准电压pref的电压电平升高,上电复位信号por的电压电平可以升高。当触发晶体管114随着检测电压dref的电压电平升高而完全导通时,上电基准电压pref的电压电平可以下降。当上电基准电压pref的电压电平下降到第一反相器121的阈值电压以下时,上电复位信号por可以被使能为逻辑低电平。当电源电压vcc的电压电平被保持时,可以保持流过触发晶体管114的电流量,并且因此可以保持上电基准电压pref的电压电平并且上电复位信号por可以保持使能。

当来自外部电源的电源电压vcc的供应中断时,电源电压vcc的电压电平可以逐渐下降。随着电源电压vcc的电压电平逐渐下降,检测电压dref的电压电平下降并且流过触发晶体管114的电流量可以变小。因此,上电基准电压pref的电压电平可以升高。当上电基准电压pref的电压电平随着检测电压dref的电压电平下降而升高以达到第一反相器121的阈值电压或更大的电压电平时,上电复位信号por可以被禁用为逻辑高电平。然后,随着电源电压vcc的电压电平下降,检测电压dref、上电基准电压pref和上电复位信号por的电压电平可以下降。当电源电压vcc的电压电平升高以达到目标电压电平或更高的电压电平时,上电复位信号发生装置100可以将上电复位信号por使能为逻辑低电平。当电源电压vcc的电压电平下降到目标电压电平以下时,上电复位信号发生装置100可以将上电复位信号por禁用为逻辑高电平。

图3是示意性地例示了图1中所示的上电复位信号发生装置100的另一操作的图。电源电压vcc的电压电平可以改变,同时电源电压vcc伴随有相当大量的噪声。具体地,当电源电压vcc升高或下降到目标电压电平附近时,电源电压vcc的电压电平由于噪声而可能反复变得高于或低于目标电压电平tl。当电源电压vcc的电压电平反复变得高于或低于目标电压电平tl时,从上电复位信号发生装置100生成的上电复位信号por的状态可能改变。即,即使在上电复位信号por变为使能之后,上电复位信号por由于电源电压vcc的噪声而可能反复变为使能或禁用。另外,即使在上电复位信号por变为禁用之后,上电复位信号por由于电源电压vcc的噪声而可能反复变为使能或禁用。上电复位信号por的不稳定状态和/或在上电复位信号por中出现的毛刺可能引发具有上电复位信号发生装置100的半导体设备的可靠性问题。

图4是例示了根据一个实施方式的上电复位信号发生装置400的配置的图。参照图4,上电复位信号发生装置400可以包括基准电压发生器410和信号驱动器420,这与图1所示的上电复位信号发生装置100相同,并且上电复位信号发生装置400可以进一步包括稳定电路430。在配置上电复位信号发生装置400的元件当中,与上电复位信号发生装置100中所包括的元件相同的元件可以用相似的附图标记表示,并且将省略相同元件的描述。稳定电路430可以联接在信号驱动器420的输入节点和输出节点之间。稳定电路430可以接收上电复位信号por以使上电复位信号por的状态稳定。上电复位信号por可以被反馈到稳定电路430,并且稳定电路430可以继续保持上电基准电压pref的电压电平,从而防止上电复位信号por不稳定地变化。当上电复位信号por被使能时,稳定电路430可以在预定量时间期间保持上电复位信号por被使能,而与电源电压vcc的电压电平波动无关。稳定电路430可以在预定量时间期间继续保持上电基准电压pref的电压电平,以防止上电复位信号por波动而再次变为禁用。当上电复位信号por变为禁用时,稳定电路430可以在预定量时间期间继续保持上电复位信号por被禁用,而与电源电压vcc的电压电平波动无关。稳定电路430可以在预定量时间期间继续保持上电基准电压pref的电压电平,以防止上电复位信号por波动而再次变为使能。如本文中针对参数所使用的词“预定”(诸如,预设时段)是指在过程或算法中使用该参数之前确定该参数的值。对于一些实施方式,在过程或算法开始之前确定参数的值。在其它实施方式中,在过程或算法期间但在过程或算法中使用参数之前确定参数的值。

当上电复位信号por变为被使能为逻辑低电平时,稳定电路430可以在预定量时间期间将上电基准电压pref驱动到接地电压vss的电平。因此,即使在电源电压vcc的电压电平中出现噪声时,也可以防止上电复位信号por波动而再次变为禁用。当上电复位信号por变为被禁用为逻辑高电平时,稳定电路430可以在预定量时间期间将上电基准电压pref驱动到电源电压vcc的电平。因此,即使在电源电压vcc的电压电平中出现噪声时,也可以防止上电复位信号por波动而再次变为使能。

图5是例示了图4所示的稳定电路430的配置的图。参照图5,稳定电路430可以包括放电控制信号发生器510、充电控制信号发生器520和电压驱动器530。放电控制信号发生器510可以接收上电复位信号por并且可以基于上电复位信号por生成放电控制信号dcct。当上电复位信号por被使能时,放电控制信号发生器510可以使能放电控制信号dcct。充电控制信号发生器520可以接收上电复位信号por,并且可以基于上电复位信号por来生成充电控制信号cct。当上电复位信号por被禁用时,充电控制信号发生器520可以使能充电控制信号cct。电压驱动器530可以基于放电控制信号dcct和充电控制信号cct来改变上电基准电压pref的电压电平。电压驱动器530可以基于放电控制信号dcct将上电基准电压pref驱动至接地电压vss。电压驱动器530可以基于充电控制信号cct将上电基准电压pref驱动至电源电压vcc。当放电控制信号dcct被使能时,电压驱动器530可以将上电基准电压pref驱动至接地电压vss,以降低上电基准电压pref的电压电平。当充电控制信号cct被使能时,电压驱动器530可以将上电基准电压pref驱动至电源电压vcc,以升高上电基准电压pref的电压电平。

放电控制信号发生器510可以包括第一控制信号发生器511。当上电复位信号por被使能时,第一控制信号发生器511可以生成放电控制信号dcct,该放电控制信号dcct在预定量时间期间保持使能。放电控制信号dcct可以在预定量时间期间保持使能为逻辑高电平。当上电复位信号por被禁用时,充电控制信号发生器520可以生成充电控制信号cct,该充电控制信号cct在预定量时间期间保持使能。充电控制信号cct可以在预定量时间期间保持使能为逻辑低电平。充电控制信号发生器520可以包括第一反相器521、第二控制信号发生器522和第二反相器523。第一反相器521可以接收上电复位信号por,并且可以将上电复位信号por反相以输出上电复位信号por的互补信号porb。第二控制信号发生器522可以与第一控制信号发生器511在配置上基本上相同,并且可以按照与第一控制信号发生器511基本相同的方式进行操作。当上电复位信号por被禁用并且上电复位信号por的互补信号porb被使能为逻辑低电平时,第二控制信号发生器522可以生成在预定量时间期间保持使能为逻辑高电平的信号。第二反相器523可以将第二控制信号发生器522生成的信号反相以输出充电控制信号cct。

电压驱动器530可以包括放电驱动器531和充电驱动器532。放电驱动器531可以联接在上电基准电压pref的节点与被提供接地电压vss的节点之间。放电驱动器531可以接收放电控制信号dcct。当放电控制信号dcct被使能时,放电驱动器531可以将上电基准电压pref的节点驱动至接地电压vss。充电驱动器532可以联接在被提供电源电压vcc的节点与上电基准电压pref的节点之间。充电驱动器532可以接收充电控制信号cct。当充电控制信号cct被使能时,充电驱动器532可以将上电基准电压pref的节点驱动至电源电压vcc。

放电驱动器531可以包括第一晶体管。第一晶体管可以是n沟道mos晶体管。第一晶体管的漏极可以联接到上电基准电压pref的节点,并且其源极可以联接到被提供接地电压vss的节点。第一晶体管的栅极可以接收放电控制信号dcct。充电驱动器532可以包括第二晶体管。第二晶体管可以是p沟道mos晶体管。第二晶体管的源极可以联接至被提供电源电压vcc的节点,并且其漏极可以联接至上电基准电压pref的节点。第二晶体管的栅极可以接收充电控制信号cct。

图6是根据一个实施方式例示了包括在放电控制信号发生器510中的第一控制信号发生器511的配置的图。参照图6,第一控制信号发生器511可以接收上电复位信号por,并且在上电复位信号por被使能时,可以生成放电控制信号dcct,该放电控制信号dcct在预定时间量期间保持使能。第一控制信号发生器511可以包括延迟器610、第一门电路620、第二门电路630、电容器640和放电器650。延迟器610可以延迟上电复位信号por以输出延迟信号dly。延迟器610可以是非反相延迟器。例如,延迟器610可以包括四个反相器和三个电容器,每个电容器联接在四个反相器当中的相邻反相器之间。延迟器610中包括的反相器和电容器的数量将不限于此。反相器的数量可以是偶数,诸如2个、4个或更多个,并且电容器的数量可以根据反相器的数量而增加或减少。延迟器610的延迟量可以由延迟器610中包括的反相器和电容器的适当数量来确定。

第一门电路620可以对上电复位信号por和延迟信号dly执行门运算以生成使能信号en。第一门电路620可以对上电复位信号por和延迟信号dly执行与运算以生成使能信号en。当上电复位信号por和延迟信号dly当中的任何一个变为逻辑低电平时,第一门电路620可以将使能信号en使能为逻辑低电平。第一门电路620可以包括第一与非门621和反相器622。第一与非门621可以通过其两个输入节点分别接收上电复位信号por和延迟信号dly。反相器622可以联接到第一与非门621的输出节点。反相器622可以将第一与非门621的输出反相,以输出使能信号en。第二门电路630可以对上电复位信号por和使能信号en执行门运算以生成控制信号con。第二门电路630可以对上电复位信号por和使能信号en执行与非运算以生成控制信号con。当上电复位信号por和使能信号en当中的任何一个被使能为逻辑低电平时,第二门控电路630可以将控制信号con转变为逻辑高电平。第二门电路630可以包括第二与非门631。第二与非门631可以通过其两个输入节点分别接收上电复位信号por和使能信号en。第二与非门631可以通过其输出节点输出控制信号con。

电容器640可以基于控制信号con来使能放电控制信号dcct。当控制信号con被使能为逻辑高电平时,电容器640可以被充电并且可以将放电控制信号dcct使能为逻辑高电平。电容器640可以在一端联接到第二与非门631的输出节点,并且可以通过这一端接收控制信号con。电容器640可以在另一端联接到输出节点on。可以通过输出节点on输出放电控制信号dcct。放电器650可以接收偏置电压bias,并且可以基于偏置电压bias来改变放电控制信号dcct的电压电平。放电器650可以使电容器640放电以降低放电控制信号dcct的电压电平。放电器650可以包括n沟道mos晶体管651。n沟道mos晶体管651的漏极可以联接至输出节点on,并且其源极可以联接至被提供接地电压vss的节点。n沟道mos晶体管651的栅极可以接收偏置电压bias。电容器640的电容、n沟道mos晶体管651的尺寸和/或电流驱动性以及偏置电压bias的电压电平可以以各种方式改变以设置预定量时间。除了第二控制信号发生器522可以接收上电复位信号por的互补信号porb而不是上电复位信号por之外,第二控制信号发生器522可以具有与第一控制信号发生器511相同的配置。

图7是例示了图5和图6所示的第一控制信号发生器511的操作的时序图。参照图5至图7在下文中所描述的将是第一控制信号发生器511的操作。当提供电源电压vcc时,上电复位信号por和偏置电压bias的电压电平可以升高。上电复位信号por的电压电平可以还对应于逻辑低电平。从第二门电路630输出的控制信号con可以具有逻辑高电平。即使当上电复位信号por的电压电平升高时,延迟器610也可以延迟上电复位信号por,以生成延迟信号dly。因此,在与延迟器610的延迟量相对应的延迟时间期间,延迟信号dly的电压电平可以不升高。当经过了与延迟器610的延迟量相对应的延迟时间时,从第一门电路620输出的使能信号en的电压电平可以与上电复位信号por的电压电平一起升高。当上电复位信号por和使能信号en的电压电平升高到逻辑高电平时,第二门电路630可以将控制信号con转变为逻辑低电平。当上电复位信号por的电压电平根据电源电压vcc的电压电平持续升高并且电源电压vcc的电压电平达到目标电压电平时,上电复位信号por可以转变到逻辑低电平。此外,使能信号en也可以转变为逻辑低电平,并且第二门电路630可以将控制信号con转变为逻辑高电平。当控制信号con转变为逻辑高电平时,电容器640可以被充电并且放电控制信号dcct可以被使能。在放电器650基于偏置电压bias使电容器640放电并且放电控制信号dcct的电压电平下降时,放电控制信号dcct可以因此在预定量时间期间保持使能。

图8是例示了在上电时段期间根据实施方式的上电复位信号发生装置400的操作的时序图。图9是例示了在断电时段期间根据实施方式的上电复位信号发生装置400的操作的时序图。在下文中参照图4至图9所描述的将是上电复位信号发生装置400的操作。图8和图9是例示了当电源电压vcc的电压电平已经升高到目标电压电平附近时的时间的放大图。因此,电源电压vcc看起来像在预定范围内振荡。当电源电压vcc的电压电平在上电时段期间升高以达到目标电压电平或更高电压电平时,上电复位信号发生装置400可以将上电复位信号por使能为逻辑低电平。当上电复位信号por变为被使能为逻辑低电平时,放电控制信号发生器510可以在预定量时间期间使放电控制信号dcct继续被使能为逻辑高电平。当放电控制信号dcct被使能时,电压驱动器530可以在预定量时间期间将上电基准电压pref驱动至接地电压vss。在电源电压vcc中可能出现噪声,因此电源电压vcc的电压电平下降到目标电压电平以下,并且在第一节点n1处可能出现噪声。根据现有技术,出现了使能的上电复位信号por波动而再次变为禁用的毛刺。然而,根据本公开的实施方式,上电基准电压pref可以被驱动至接地电压vss,因此可以防止上电复位信号por波动而再次变为禁用。因此,在上电复位信号por被使能时,稳定电路430可以在预定量时间期间保持上电复位信号por被使能,而与电源电压vcc的电压电平波动无关。当经过了预定量时间时,电源电压vcc的电压电平升高到足以达到目标电压电平或更大的电压电平,因此即使在电源电压vcc中出现噪声,在上电复位信号por中也没有机会出现毛刺。

参照图9,当在断电时段中电源电压vcc的电压电平下降到目标电压电平以下时,上电复位信号发生装置400可以将上电复位信号por禁用为逻辑高电平。充电控制信号发生器520的第一反相器521可以将上电复位信号por反相以输出上电复位信号por的互补信号porb,并且第二控制信号发生器522可以生成具有与图8所示的放电控制信号dcct基本相同波形的信号。第二反相器523可以将从第二控制信号发生器522生成的信号反相以生成充电控制信号cct。充电控制信号cct可以在上电复位信号por被禁用时被使能为逻辑低电平,并且可以在预定量时间期间保持使能。当充电控制信号cct被使能时,电压驱动器530可以在预定量时间期间将上电基准电压pref驱动到电源电压vcc。由于即使在电源电压vcc中出现噪声并且因此电源电压vcc的电压电平升高以达到目标电压电平或更高的电压电平时,上电基准电压pref也被驱动到电源电压vcc的电平,因此可以防止上电复位信号por波动而再次变为被使能。因此,在上电复位信号por被禁用时,稳定电路430可以在预定量时间期间保持上电复位信号por被禁用,而与电源电压vcc的电压电平波动无关。当经过了预定量时间时,电源电压vcc的电压电平下降得足以在目标电压电平以下,因此,即使在电源电压vcc中出现噪声,在上电复位信号por中也没有机会出现毛刺。

图10是例示了在断电时段期间图4和图5所示的稳定电路430的另一操作的时序图。参照图10,当在断电时段中电源电压vcc的电压电平下降到目标电压电平以下时,上电复位信号por可以转变为逻辑高电平。此时,稳定电路430可以将充电控制信号cct使能为逻辑低电平,以防止在上电复位信号por中出现毛刺。然而,即使在上电复位信号por中出现不期望的毛刺时,稳定电路430也可以防止上电基准电压pref被驱动至接地电压vss的电平。当在上电复位信号por中出现毛刺时,放电控制信号发生器510可以检测上电复位信号por中的毛刺,以使能放电控制信号dcct,并且可能发生充电控制信号cct和放电控制信号dcct二者被使能的故障。然而,具有延迟器610的第一控制信号发生器511可以防止在充电控制信号cct和放电控制信号dcct之间的任何一个被使能的时段期间充电控制信号cct和放电控制信号dcct两者都被使能。一起参照图6,即使在上电复位信号por中出现毛刺时,在与延迟器610的延迟量相对应的延迟时间期间,放电控制信号发生器510的使能信号en的电压电平也可以继续保持。因此,从第二门电路630输出的控制信号con可能不转变为逻辑低电平,而是可以停留在逻辑高电平,并且放电控制信号dcct可以固定为逻辑低电平并且可以保持禁用。稳定电路430可以基于充电控制信号cct,通过充电驱动器532将上电基准电压pref驱动至电源电压vcc的电平。相反,即使在上电复位信号por被使能为逻辑低电平之后在上电复位信号por中出现不期望的毛刺,第二控制信号发生器522的延迟器610也可以防止充电控制信号cct被使能。因此,即使当在与延迟器610的延迟量相对应的延迟时间期间在上电复位信号por中出现毛刺,充电控制信号cct也可能不被使能,并且稳定电路430可以通过放电驱动器531将上电基准电压pref驱动至接地电压vss的电平。

尽管上面已经描述了一些实施方式,但是本领域技术人员将理解,所描述的实施方式仅是示例性的。因此,不应基于所描述的实施方式来限制上电复位信号发生装置。相反,应该仅根据结合以上描述和附图的所附权利要求书来限制本文所述的上电复位信号发生装置。

相关申请的交叉引用

本申请要求于2019年11月29日在韩国知识产权局提交的韩国申请no.10-2019-0157542的优先权,该韩国申请的全部内容通过引用整体并入本文中,如同在本文中完整阐述一样。

- 还没有人留言评论。精彩留言会获得点赞!