一种用于ADC的高精度张弛振荡器

一种用于adc的高精度张弛振荡器

技术领域

1.本发明涉及电路设计技术领域,尤其是一种用于adc的高精度张弛振荡器。

背景技术:

[0002] 随着物联网行业的兴起,传感器作为一种能够将自然界中的非电学信号转换为电学信号的器件,是整个物联网系统信息的来源。在自然界中的信号都是连续的模拟信号,以目前的技术能力,要处理模拟信号比较困难,而处理数字信号更为容易,所以信息很多时候需要通过模数转换器(analog-to-digital converter,adc)来实现模拟域到数字域的转换。

[0003]

在adc系统中,需要使用振荡器为其提供时钟频率。不同的振荡器电路结构在功耗、频率稳定性和面积等方面各有优劣。常用的作为时钟的振荡器电路有晶体振荡器、环形振荡器、lc振荡器和rc振荡器。

[0004]

(1)晶体振荡电路具有精度高、抗干扰性强等优点。但是晶体振荡器需要外界接入石英晶体,因此不利于芯片的内部集成。

[0005]

(2)环形振荡器有电路结构简单、使用方便等优点。然而环形振荡器的输出频率易受环境影响,抗干扰能力弱,导致频率稳定性不高。

[0006]

(3)lc振荡器有良好的温度特性和电压特性。但其需要大量电容器件c与电感器件l,对于芯片面积的占用太大,并且不易集成。

[0007]

(4)rc振荡器可操作性强,且可集成到芯片内部,面积和成本较小。但是rc振荡器频率稳定性不高,输出频率比较容易受到温度、器件失配和电源电压的影响。

[0008]

对于adc这样要求集成度高的系统,常采用环形振荡器与rc振荡器,rc振荡器相比于环形振荡器,温度系数更小,输出频率更加稳定。故而rc振荡器被广泛应用。而rc振荡器存在容易受到温度、器件失配与电压的影响,振荡频率不稳定的问题。因此研究高精度的振荡器是当下研究热点。张弛振荡器也是rc振荡器的一种类型。本发明涉及一种用于adc的高精度张弛振荡器。

技术实现要素:

[0009]

本发明提出一种用于adc的高精度张弛振荡器,电路结构简单,易于集成,可操作性强并且功耗低。

[0010]

本发明采用以下技术方案。

[0011]

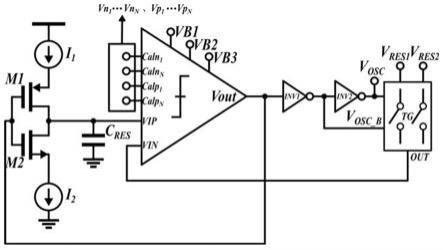

一种用于adc的高精度张弛振荡器,所述振荡器包括电流源i1与i2、电容器cres、比较器、反相器inv1、inv2、振荡器晶体管组和电压选择开关tg;所述比较器与反相器inv1、电容器cres相连,还与振荡器晶体管m1、 m2相连;比较器连有偏置电源vb1、vb2、vb3,以及校准信号端口caln1~ calnn、calp1~ calpn,通过接入校准信号vn1~vnn、vp1~vpn,来校准在比较过程中存在的失配问题;所述振荡器通过对比较器失配的校准来实现振荡器的高精度,电压选择开关根据

比较器输出结果选择相应标准电压以实现振荡输出。

[0012]

所述电流源i1的下端连接振荡器晶体管m1的源极,上端接入供电电源;电流源i2的上端连接振荡器晶体管m2的源极,下端接地;振荡器晶体管m1、m2的漏极与比较器输入端口vip以及电容cres上极板接在一起,栅极与比较器输出端口vout相接;电容器cres上极板接比较器输入端vip;下级板接地;输入端vip从电容cres上极板相连接;输入端vin与选择开关tg右端相连接;反相器inv1左端接比较器输出端口vout;右端与反相器inv2的左端相连接并且作为选择开关tg的输入信号端vosc_b;反相器inv2的右端与选择开关tg的输入信号端vosc相连接并且作为整体电路的输出端;电压选择开关tg接入待选参考电压vres1、vres2;右端接入比较器输入端vin。

[0013]

振荡器工作时振荡输出信号,方法为:步骤s1、若vout为低电平,则晶体管m1导通,m2关断,cres被充电将vip拉到高电平;而电压选择开关tg根据比较器的输出vout选择低参考电压vres2,则vin为低电平。系统输出vosc为低电平;步骤s2、随后,由于vip》vin,比较器输出端voutp为高电平,此时晶体管m2导通,m1关断,cres对地放电将vip拉到低电平;而电压选择开关tg根据比较器的输出vout选择选择高参考电压vres1,则vin为高电平,使系统输出vosc高电平;步骤s1、步骤s2循环往复。

[0014]

所述比较器由电流源ic0~icn+1以及比较器晶体管m1、m2、m3、m4、m5、m6、m7、m8、m9、m10、m11、mn1~mnn和mp1~mpn组成;比较器晶体管m1、m2栅极接入偏置电源vb1,源极接地,m1的漏极与m3的源极相连;m2的漏极与m4的源极相连;比较器晶体管m3、m4栅极接入偏置电源vb2,m3的漏极与m5的漏极相连;m4的漏极与m6的漏极相连;比较器晶体管m5、m6栅极接入偏置电源vb3,m5的源极与m7的漏极相连;m6的源极与m8的漏极相连;比较器晶体管m7、m8栅极短接并接入m3与m5的漏极,源极接入电源电位;晶体管m9、m10的源极均与电流源ic1下端相连接,m9栅极接入vin信号,漏极与m1的漏极相连接;m10栅极接入vip信号,漏极与m2的漏极相连接;其余比较器晶体管mn1~mnn和mp1~mpn,都根据序号1~n成对排布;比较器晶体管mn1与mp1的源极均与电流源ic2下端相连接,mn1栅极接入caln1信号,漏极与m1的漏极相连接;mp1栅极接入calp1信号,漏极与m2的漏极相连接;比较器晶体管mnn与mpn的源极均与电流源icn+1下端相连接,mnn栅极接入calnn信号,漏极与m1的漏极相连接;mpn栅极接入calpn信号,漏极与m2的漏极相连接;比较器晶体管m11的栅极m4、m6的漏极相连接,源极接地,漏极与电流源ic0下端相连接,并作为比较器输出端vout;当vip 》 vin时,流经比较器晶体管m2的电流变小,比较器晶体管m2的漏极电位下

降,比较器晶体管m1的漏极电位上升;比较器晶体管m11的栅极电位下降,则比较器晶体管m11的漏极电位上升,输入信号vip-vin就通过多级运放结构增益放大并最终输出高电平。

[0015]

所述电压选择开关tg包括电压选择开关晶体管m1、m2、m3、m4;电压选择开关晶体管m1、m4的栅极接入信号vosc,m1的源极与m2的漏极相连接,并接入参考电位vres2,m1的漏极与m2的源极相连接,m2的栅极与m3的栅极相连接,并接入信号vosc_b;m3的源极与m4的漏极相连接,并接入参考电位vres1; m3的漏极与m4的源极相连接并与m1的漏极与m2的源极相连作为输出端口out;当信号vosc为高电平、vosc_b为低电平时,电压选择开关晶体管m1、m2关断;m3、m4导通,输出端口out的输出电压out为vres1;当信号vosc为低电平、vosc_b为高电平时,电压选择开关晶体管m1、m2导通;电压选择开关晶体管m3、m4关断,输出端口out的输出电压out为vres2。

[0016]

所述校准信号vn1~vnn、vp1~vpn为通过外部fpga输入或内部dac产生的校准信号。

[0017]

所述比较器的多级运放结构为大增益的两级运放结构。

[0018]

本发明提出的振荡器拥有精确校准的功能。相比于传统振荡器电路,加入了校准信号vn1~vnn、vp1~vpn(外部fpga输入或内部dac产生校准信号)。电路结构简单,易于集成,可操作性强并且功耗低。

[0019]

本发明在电路结构简单的情况下实现高精度的效果,适合应用于adc系统。

附图说明

[0020]

下面结合附图和具体实施方式对本发明进一步详细的说明:附图1是本发明所述振荡器的整体电路示意图;附图2是本发明的比较器的电路示意图;附图3是电压选择开关tg的电路示意图。

具体实施方式

[0021]

如图所示,一种用于adc的高精度张弛振荡器,所述振荡器包括电流源i1与i2、电容器cres、比较器、反相器inv1、inv2、振荡器晶体管组和电压选择开关tg;所述比较器与反相器inv1、电容器cres相连,还与振荡器晶体管m1、 m2相连;比较器连有偏置电源vb1、vb2、vb3,以及校准信号端口caln1~ calnn、calp1~ calpn,通过接入校准信号vn1~vnn、vp1~vpn,来校准在比较过程中存在的失配问题;所述振荡器通过对比较器失配的校准来实现振荡器的高精度,电压选择开关根据比较器输出结果选择相应标准电压以实现振荡输出。

[0022]

所述电流源i1的下端连接振荡器晶体管m1的源极,上端接入供电电源;电流源i2的上端连接振荡器晶体管m2的源极,下端接地;振荡器晶体管m1、m2的漏极与比较器输入端口vip以及电容cres上极板接在一起,栅极与比较器输出端口vout相接;电容器cres上极板接比较器输入端vip;下级板接地;输入端vip从电容cres上极板相连接;输入端vin与选择开关tg右端相连接;反相器inv1左端接比较器输出端口vout;右端与反相器inv2的左端相连接并且作

为选择开关tg的输入信号端vosc_b;反相器inv2的右端与选择开关tg的输入信号端vosc相连接并且作为整体电路的输出端;电压选择开关tg接入待选参考电压vres1、vres2;右端接入比较器输入端vin。

[0023]

振荡器工作时振荡输出信号,方法为:步骤s1、若vout为低电平,则晶体管m1导通,m2关断,cres被充电将vip拉到高电平;而电压选择开关tg根据比较器的输出vout选择低参考电压vres2,则vin为低电平。系统输出vosc为低电平;步骤s2、随后,由于vip》vin,比较器输出端voutp为高电平,此时晶体管m2导通,m1关断,cres对地放电将vip拉到低电平;而电压选择开关tg根据比较器的输出vout选择选择高参考电压vres1,则vin为高电平,使系统输出vosc高电平;步骤s1、步骤s2循环往复。

[0024]

如图2所示,所述比较器由电流源ic0~icn+1以及比较器晶体管m1、m2、m3、m4、m5、m6、m7、m8、m9、m10、m11、mn1~mnn和mp1~mpn组成;比较器晶体管m1、m2栅极接入偏置电源vb1,源极接地,m1的漏极与m3的源极相连;m2的漏极与m4的源极相连;比较器晶体管m3、m4栅极接入偏置电源vb2,m3的漏极与m5的漏极相连;m4的漏极与m6的漏极相连;比较器晶体管m5、m6栅极接入偏置电源vb3,m5的源极与m7的漏极相连;m6的源极与m8的漏极相连;比较器晶体管m7、m8栅极短接并接入m3与m5的漏极,源极接入电源电位;晶体管m9、m10的源极均与电流源ic1下端相连接,m9栅极接入vin信号,漏极与m1的漏极相连接;m10栅极接入vip信号,漏极与m2的漏极相连接;其余比较器晶体管mn1~mnn和mp1~mpn,都根据序号1~n成对排布;比较器晶体管mn1与mp1的源极均与电流源ic2下端相连接,mn1栅极接入caln1信号,漏极与m1的漏极相连接;mp1栅极接入calp1信号,漏极与m2的漏极相连接;比较器晶体管mnn与mpn的源极均与电流源icn+1下端相连接,mnn栅极接入calnn信号,漏极与m1的漏极相连接;mpn栅极接入calpn信号,漏极与m2的漏极相连接;比较器晶体管m11的栅极m4、m6的漏极相连接,源极接地,漏极与电流源ic0下端相连接,并作为比较器输出端vout;当vip 》 vin时,流经比较器晶体管m2的电流变小,比较器晶体管m2的漏极电位下降,比较器晶体管m1的漏极电位上升;比较器晶体管m11的栅极电位下降,则比较器晶体管m11的漏极电位上升,输入信号vip-vin就通过多级运放结构增益放大并最终输出高电平。

[0025]

如图3所示,所述电压选择开关tg包括电压选择开关晶体管m1、m2、m3、m4;电压选择开关晶体管m1、m4的栅极接入信号vosc,m1的源极与m2的漏极相连接,并接入参考电位vres2,m1的漏极与m2的源极相连接,m2的栅极与m3的栅极相连接,并接入信号vosc_b;m3的源极与m4的漏极相连接,并接入参考电位vres1; m3的漏极与m4的源极相连接并与m1的漏极与m2的源极相连作为输出端口out;当信号vosc为高电平、vosc_b为低电平时,电压选择开关晶体管m1、m2关断;m3、m4

导通,输出端口out的输出电压out为vres1;当信号vosc为低电平、vosc_b为高电平时,电压选择开关晶体管m1、m2导通;电压选择开关晶体管m3、m4关断,输出端口out的输出电压out为vres2。

[0026]

所述校准信号vn1~vnn、vp1~vpn为通过外部fpga输入或内部dac产生的校准信号。

[0027]

所述比较器的多级运放结构为大增益的两级运放结构。

[0028]

实施例:振荡器工作时,若vout此时为低电平,则晶体管m1导通,m2关断,cres被充电将vip拉到高电平;而电压选择开关tg根据比较器的输出vout选择低参考电压vres2,则vin为低电平。系统输出vosc为低电平。

[0029]

比较器工作时,当vip 》 vin时,流经m2的电流变小,m2的漏极电位下降,m1的漏极电位上升;m11的栅极电位下降,则m11的漏极电位上升。由于比较器采用两级运放结构,增益较大,最终输出高电平。比较器在比较过程中存在的失配问题,通过在外端接入校准信号vn1~vnn、vp1~vpn。选择相应的电流源对输入电流进行校准。

[0030]

随后,由于vip》vin,比较器输出端voutp为高电平,此时晶体管m2导通,m1关断,cres对地放电将vip拉到低电平。

[0031]

电压选择开关tg根据比较器的输出vout选择,选择高参考电压vres1,则vin为高电平。

[0032]

系统输出vosc高电平。该张弛振荡器就得到振荡的输出信号,以此循环往复,实现功能。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1