一种算法步长及环路带宽自适应调整的小数全数字锁相环

1.本发明属于集成电路设计技术领域,尤其涉及一种算法步长及环路带宽自适应调整的小数全数字锁相环。

背景技术:

2.锁相环主要用于收发系统中,并为射频前端提供高分辨率、低相位噪声和高频谱纯度的本振信号,近年来,随着数字系统的发展,全数字锁相环因其可移植性好和不逊于模拟锁相环的特点逐渐占据优势。小数数字锁相环因其较高的频率分辨率而应用非常广泛,但实现小数数字锁相环中时间数字转换器与σ-δ调制器的量化噪声对输出频谱上的小数杂散带来较大的影响,从而使其在无线收发器中对数据接收与发射带来较大的干扰。为减轻小数锁相环时间数字转换器与σ-δ调制器量化噪声的影响,传统通过最小均方(lms)算法来降低σ-δ调制器的量化噪声所导致的小数杂散时,lms算法通常需要较长的时间才会收敛,通常收敛时间达到亚毫秒量级,因此限制了锁相环的应用。同时,小数数字锁相环的带宽通常设置得非常小来抑制带内相位噪声,但这又会导致锁相环的锁定时间变长,从而限制其在某些情况下的应用。

技术实现要素:

3.本发明的主要目的是提供一种算法步长及环路带宽自适应调整的小数全数字锁相环,该小数全数字锁相环能够根据锁相环环路锁定状态,自适应并行地调整lms算法的步长以及环路带宽,减小了lms算法收敛的时间与环路锁定时间,降低了σδ调制器量化误差导致的杂散,并抑制了带内相位噪声。

4.为实现上述目的,本发明提供了一种算法步长及环路带宽自适应调整的小数全数字锁相环,包括鉴频鉴相器、时间数字转换器、自适应步长/带宽控制算法模块、第一减法器、第二减法器、第一加法器、第一寄存器、第一乘法器、lms算法模块、数字环路滤波器、数控振荡器、多模分频器及σδ调制器;

5.其中,所述鉴频鉴相器的两个输入端分别接外部时钟信号和多模分频器的输出信号,鉴频鉴相器的一个输出端接自适应步长/带宽控制算法模块的输入端、另外两个输出端接时间数字转换器的输入端;所述自适应步长/带宽控制算法模块的输出分别接lms算法模块以及数字环路滤波器;所述时间数字转换器的输出接第一减法器的一个输入;所述第一减法器的一端输入接时间数字转换器的输出作为减数,另一端输入接第一乘法器的输出作为被减数,第一减法器的输出接数字环路滤波器的输入以及lms算法模块的输入;

6.所述第二减法器的一端输入接外部输入的频率控制字fcw作为减数,另一端输入接σδ调制器的输出作为被减数,所述第二减法器的输出接第一加法器的输入;所述第一加法器的两个输入分别接第二减法器的输出以及第一寄存器的输出,所述第一加法器的输出接第一寄存器的输入、第一乘法器的输入和lms算法模块的其中一个输入;所述第一乘法器的两个输入分别接第一加法器的输出以及lms算法模块的输出,所述第一乘法器的输出

通过截断后作为第一减法器的另一端输入;

7.所述lms算法模块的三个输入分别接自适应步长/带宽控制算法模块的输出、第一加法器的输出以及第一减法器的输出,所述lms算法模块的输出接第一乘法器的其中一个输入;所述数字环路滤波器的两个输入分别接第一减法器的输出以及自适应步长/带宽控制算法模块的输出,数字环路滤波器的输出接数控振荡器的输入;所述σδ调制器的两个输入分别接外部信号fcw和多模分频器的输出,σδ调制器的输出接多模分频器的输入以及第二减法器的另一端输入;所述数控振荡器的输出接多模分频器的另一个输入;所述多模分频器的输出接鉴频鉴相器的其中一个输入以及σδ调制器的时钟端。

8.作为本发明的进一步改进,所述鉴频鉴相器包括第一d触发器、第二d触发器、第一与非门~第十与非门、延时器、与门、第一反相器以及第二反相器;

9.其中,所述第一d触发器的三个输入分别接外部参考时钟、电源电压以及延时器的输出,第一d触发器的输出分别接第一与非门、第五与非门和第八与非门的输入以及与门的输入;所述第二d触发器的三个输入分别接多模分频器的输出、电源电压以及延时器的输出,第二d触发器的输出接第二与非门、第六与非门和第九与非门的输入以及与门的输入;所述与门的输入分别接第一d触发器和第二d触发器的输出,与门的输出接延时器的输入;

10.所述第一与非门的两个输入分别接第一d触发器的输出以及第二与非门的输出,第一与非门的输出接第三与非门的输入;所述第二与非门的两个输入分别接第二d触发器的输出以及第一与非门的输出,第二与非门的输出接第四与非门的输入;所述第三与非门的两个输入分别接第一与非门和第四与非门的输出,第三与非门的输出接第五与非门和第九与非门的输入;第四与非门的两个输入分别接第二与非门和第三与非门的输出,第四与非门的输出接第三与非门、第六与非门和第八与非门的输入以及第一反相器的输入;第五与非门的两个输入分别接第一d触发器的输出以及第三与非门的输出,第五与非门的输出接第七与非门的输入;第六与非门的两个输入分别接第二d触发器的输出以及第四与非门的输出,第六与非门的输出接第七与非门的输入;第七与非门的两个输入分别接第五与非门和第六与非门的输出,第七与非门的输出接start;第八与非门的两个输入分别接第一d触发器的输出以及第四与非门的输出,第八与非门的输出接第十与非门的输入;第九与非门的两个输入分别接第二d触发器的输出以及第三与非门的输出,第九与非门的输出接第十与非门的输入;第十与非门的两个输入分别接第八与非门和第九与非门的输出,第十与非门的输出接stop;所述第一反相器的输入接第四与非门的输出,第一反相器的输出接第二反相器的输入;第二反相器的输入接第一反相器的输出,第二反相器的输出接sign。

11.作为本发明的进一步改进,所述时间数字转换器包含第一量化单元~第六十四量化单元和解码器;

12.所述第一量化单元的两个输入分别接外部信号start、stop,第一量化单元的三个输出分别接第二量化单元的两个输入以及解码器的一个输入;所述第二量化单元~第六十四量化单元结构相同,并与第一量化单元串联形成所述时间数字转换器;所述第一量化单元~第六十四量化单元的输出接解码器的输入,解码器的输出接第一减法器的正端;

13.所述第一量化单元包含第一延时单元、第二延时单元和d触发器;所述第一延时单元接外部输入start,第一延时单元的输出接d触发器的一个输入以及第二量化单元的第一延时单元;所述第二延时单元接外部输入stop,第二延时单元的输出接d触发器的时钟端输

入以及第二量化单元的第二延时单元;所述d触发器的两个输入分别接第一延时单元和第二延时单元的输出,所述d触发器的输出接解码器。

14.作为本发明的进一步改进,所述自适应步长/带宽控制算法模块包含第二加法器、第二寄存器、分频器、第一数字比较器、第二数字比较器、计数器以及或门;

15.所述第二加法器的一个输入接外部sign信号、另一个输入接第二寄存器的输出,第二加法器的输出接第二寄存器的输入以及第一比较器的负端输入、第二数字比较器的正端输入;所述第二寄存器的两个输入分别接第二加法器的输出和或门的输出,第二寄存器另外一个输入接外部时钟信号fref,第二寄存器的输出接第二加法器的输入;所述分频器的输入接外部时钟信号fref,分频器的输出接第一数字比较器和第二数字比较器的时钟端输入;所述第一数字比较器的正端输入接外部输入ntarget1,第一数字比较器的负端输入接第二加法器的输出,第一数字比较器的时钟端输入接分频器输出,第一数字比较器的输出接或门的一个输入;所述第二数字比较器的正端输入接第二加法器的输出,第二数字比较器的负端输入接外部输入ntarget2,第二数字比较器的时钟端输入接分频器输出,第二数字比较器的输出接或门的另一个输入;所述或门的两个输入分别接第一数字比较器和第二数字比较器的输出,或门的输出接第二寄存器的一个输入以及sel。

16.作为本发明的进一步改进,所述lms算法模块包含第二乘法器、第三乘法器、mux、第三加法器以及第三寄存器;

17.所述第二乘法器的两个输入分别接外部输入p[k]、e[k],第二乘法器的输出接第三乘法器的一个输入;所述mux的两个输入分别接外部输入γ0、γ1,mux的选择端接外部输入sel,mux的输出接第三乘法器的另一个输入;所述第三乘法器的两个输入分别接mux的输出和第二乘法器的输出,第三乘法器的输出接第三加法器的一个输入;所述第三加法器的两个输入分别接第三乘法器的输出以及第三寄存器的输出,第三加法器的输出接第三寄存器的输入以及输出端out;所述第三寄存器的输入接第三加法器的输出,第三寄存器的输出接第三加法器的一个输入。

[0018]

作为本发明的进一步改进,所述数字环路滤波器包括第四乘法器、第五乘法器、第四加法器、第五加法器、第四寄存器、第五寄存器,第一mux及第二mux;

[0019]

所述第四乘法器的两个输入分别接外部数字信号e[k]以及第一mux的输出,第四乘法器的输出接第五加法器;所述第五乘法器的两个输入分别接外部数字信号e[k]以及第二mux的输出,第五乘法器的输出接第四加法器;所述第一mux的两个输入分别接外部输入α0、α1,第一mux的选择端接外部输入sel,第一mux的输出接第四乘法器的输入;所述第二mux的两个输入分别接外部输入β0、β1,第二mux的选择端接外部输入sel,第二mux的输出接第五乘法器的输入;所述第四加法器的两个输入分别接第五乘法器的输出以及第四寄存器的输出,第四加法器的输出接第四寄存器的输入;所述第四寄存器的两个输入分别接外部时钟fref与第四加法器的输出,第四寄存器的输出接第四加法器的输入以及第五加法器的输入;所述第五加法器的两个输入分别接第四寄存器的输出以及第四乘法器的输出;第五加法器的输出接第五寄存器的输入;所述第五寄存器的两个输入分别接第五加法器的输出以及外部时钟信号fref,第五寄存器的输出接out。

[0020]

作为本发明的进一步改进,所述数控振荡器包括第一nmos管nm1、第二nmos管nm2、第一pmos管pm1、第二pmos管pm2、第一电阻r1、第二电阻r2、第一电容c1、第二电容c2、粗调

电容阵列、精调电容阵列及电感l1;

[0021]

所述电感l1的左右两端分别接vp、vn,电感l1的中心抽头接vdd;所述第一nmos管nm1的栅极接vn以及第一电容c1的一端,nm1的漏极接vp、第二nmos管nm2的栅极和第二电容c2的一端,nm1的源极接第一pmos管pm1的源极;所述第二nmos管nm2的栅极接vp以及第二电容c2的一端,nm2的漏极接vn、第一nmos管nm1的栅极和第一电容c1的一端,nm2的源极接第二pmos管pm2的源极;所述第一pmos管pm1的栅极接第二电容c2的另一端以及第一电阻r1的一端,pm1的源极接第一nmos管nm1的源极,pm1的漏极接gnd;所述第二pmos管pm2的栅极接第一电容c1的另一端以及第二电阻r2的一端,pm2的源极接第二nmos管nm2的源极,pm2的漏极接gnd;所述第一电阻r1的一端接pm1的栅极以及第二电容c2的另一端,第一电阻r1的另一端接gnd;所述第二电阻r2的一端接pm2的栅极以及第一电容c1的另一端,第二电阻r2的另一端接gnd;所述第一电容c1的一端接nm1的栅极以及vn,第一电容c1的另一端接pm2的栅极以及r2的一端;所述第二电容c2的一端接nm2的栅极以及vp,第二电容c2的另一端接pm1的栅极以及r1的一端。

[0022]

作为本发明的进一步改进,所述精调电容阵列由第一组的第三pmos管和第四pmos管以及第二~第八组结构相同但尺寸不同的阵列组成,第一组的第三pmos管和第四pmos管的源极、漏极都接外部输入信号df[0],第三pmos管的栅极接vp,第四pmos管的栅极接vn;第二组到第八组精调电容阵列都采用相同结构,与第一组共同形成阵列;

[0023]

所述粗调电容阵列由第一组的nmos管、第三电容、第四电容、第三电阻、第四电阻、反相器以及第二组粗调电容阵列~第五组粗调电容阵列组成,所述第三电容的一端接vp、另一端接第三电阻的一端与第三nmos管的源极;所述第三电阻的另一端接第一反相器的输出及第四电阻的一端;所述第三nmos管的栅极接外部输入dc[0],第三nmos管的漏极接第四电阻的另一端以及第四电容的一端;所述第四电容的另一端接vn;所述第一反相器的输入接外部输入dc[0];第二组到第五组粗调电容阵列都采用相同结构,与第一组共同形成阵列。

[0024]

作为本发明的进一步改进,所述多模分频器包含第一2/3分频器~第六2/3分频器;

[0025]

所述第一2/3分频器的三个输入端分别接外部输入fin、p0以及第二2/3分频器的输出,第一2/3分频器的输出接第二2/3分频器的一个输入;所述第二2/3分频器的三个输入端分别接外部输入p1、第一2/3分频器的输出以及第三2/3分频器的输出,第二2/3分频器的两个输出分别接第一2/3分频器和第三2/3分频器的输入;所述第三2/3分频器的三个输入端分别接外部输入p2、第二2/3分频器的输出以及第四2/3分频器的输出,第三2/3分频器的两个输出分别接第二2/3分频器和第四2/3分频器的输入;所述第四2/3分频器的三个输入端分别接外部输入p3、第三2/3分频器的输出以及第五2/3分频器的输出,第四2/3分频器的两个输出分别接第三2/3分频器和第五2/3分频器的输入;所述第五2/3分频器的三个输入端分别接外部输入p4、第四2/3分频器的输出以及第六2/3分频器的输出,第五2/3分频器的两个输出分别接第四2/3分频器和第六2/3分频器的输入;所述第六2/3分频器的三个输入端分别接外部输入p5、第五2/3分频器的输出以及电源电压vdd,第六2/3分频器的两个输出分别接第五2/3分频器的输入以及输出端fout。

[0026]

作为本发明的进一步改进,所述σδ调制器包括一个19位cla、两个24位cla、一个

5比特移位模块、四个1位寄存器、一个19位寄存器、两个24位寄存器及噪声消除电路;

[0027]

所述19位cla的两个输入端分别接第四寄存器的1比特输出端和第五寄存器的19比特输出端,19位cla的19比特输出端接5比特移位模块的19比特输入端,19位cla的1比特输出端分别接第一寄存器和第五寄存器的1比特输入端;所述5比特移位模块的24比特输出端接第一24位cla的24比特输入端;所述第一24位cla的另外两个输入端分别接19位cla的1比特输出端和第六寄存器的24比特输出端,第一24位cla的1比特输出端分别接第二寄存器和第二24位cla的1比特输入端,第一24位cla的24比特输出端接第二24位cla的24比特输入端;所述第二24位cla的另外两个输入端分别接24位cla的1比特输出端和第七寄存器的24比特输出端,第二24位cla的1比特输出端接第三寄存器的1比特输入端,第二24位cla的24比特输出端接第七寄存器的24比特输入端;所述噪声消除电路的三个输入端分别接第一寄存器、第二寄存器和第三寄存器的1比特输出端,噪声消除电路的4比特输出端接y。

[0028]

本发明的有益效果为:本发明在现有技术及电路结构的基础上进行了改进与优化,通过检测环路的锁定状态来自适应并行调整lms算法的步长与数字环路滤波器的带宽,当锁相环环路未锁定时,电路选择较大的lms步长和数字环路滤波器的增益系数,从而可以缩短lms算法收敛时间和锁相环的锁定时间;当锁相环环路锁定时,电路选择较小的lms步长和数字环路滤波器的增益系数,从而可以抑制小数杂散和带内相位噪声。

附图说明

[0029]

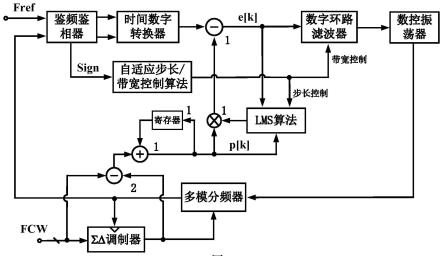

图1是本发明的小数全数字锁相环的结构框图。

[0030]

图2是图1中鉴频鉴相器的电路图。

[0031]

图3(a)和图3(b)分别是图1中时间数字转换器与量化单元的电路图。

[0032]

图4是图1中自适应步长/带宽控制算法模块的电路图。

[0033]

图5是图1中lms算法模块的电路图。

[0034]

图6是图1中数字环路滤波器的电路图。

[0035]

图7是图1中数控振荡器的电路图。

[0036]

图8(a)和图8(b)分别是图1中多模分频器与2/3分频单元的电路图。

[0037]

图9是图1中σδ调制器的电路图。

具体实施方式

[0038]

为了使本发明的目的、技术方案和优点更加清楚,下面结合附图和具体实施例对本发明进行详细描述。

[0039]

需要强调的是,在描述本发明过程中,各种公式和约束条件分别使用前后一致的标号进行区分,但也不排除使用不同的标号标志相同的公式和/或约束条件,这样设置的目的是为了更清楚的说明本发明特征所在。

[0040]

如图1至图9所示,本发明提供了一种算法步长及环路带宽自适应调整的小数全数字锁相环,包括鉴频鉴相器、时间数字转换器、自适应步长/带宽控制算法模块、第一减法器、第二减法器、第一加法器、第一寄存器、第一乘法器、lms算法模块、数字环路滤波器、数控振荡器、多模分频器以及σδ调制器。

[0041]

所述鉴频鉴相器的两个输入端分别接外部时钟信号和多模分频器的输出信号,鉴

频鉴相器的一个输出端接自适应步长/带宽控制算法模块的输入端、另外两个输出端接时间数字转换器的输入端。所述自适应步长/带宽控制算法模块的输出分别接lms算法模块以及数字环路滤波器。所述时间数字转换器的输出接第一减法器的一端输入。所述第一减法器的一端输入接时间数字转换器的输出作为减数,另一端输入接第一乘法器的输出作为被减数,第一减法器的输出接数字环路滤波器的输入以及lms算法模块的输入。

[0042]

所述第二减法器的一端输入接外部输入的频率控制字fcw作为减数,另一端输入接σδ调制器的输出作为被减数,所述第二减法器的输出接第一加法器的输入。所述第一加法器的两个输入分别接第二减法器的输出以及第一寄存器的输出,所述第一加法器的输出接第一寄存器的输入、第一乘法器的输入和lms算法模块的其中一个输入。所述第一乘法器的两个输入分别接第一加法器的输出以及lms算法模块的输出,所述第一乘法器的输出通过截断后作为第一减法器的输入。

[0043]

所述lms算法模块的三个输入分别接自适应步长/带宽控制算法模块的输出、第一加法器的输出以及第一减法器的输出,所述lms算法模块的输出接第一乘法器的其中一个输入。所述数字环路滤波器的两个输入分别接第一减法器的输出以及自适应步长/带宽控制算法模块的输出,数字环路滤波器的输出接数控振荡器的输入。所述σδ调制器的两个输入分别接外部信号fcw和多模分频器的输出,σδ调制器的输出接多模分频器的输入以及第二减法器的输入。所述数控振荡器的输出接多模分频器的另一个输入。所述多模分频器的输出接鉴频鉴相器的其中一个输入以及σδ调制器的时钟端。

[0044]

所述鉴频鉴相器包括第一d触发器、第二d触发器、第一与非门~第十与非门、延时器、与门、第一反相器以及第二反相器。其中,所述第一d触发器的三个输入分别接外部参考时钟、电源电压以及延时器的输出,第一d触发器的输出分别接第一与非门、第五与非门和第八与非门的输入以及与门的输入;所述第二d触发器的三个输入分别接多模分频器的输出、电源电压以及延时器的输出,第二d触发器的输出接第二与非门、第六与非门和第九与非门的输入以及与门的输入;所述与门的输入分别接第一d触发器和第二d触发器的输出,与门的输出接延时器的输入。

[0045]

所述第一与非门的两个输入分别接第一d触发器的输出以及第二与非门的输出,第一与非门的输出接第三与非门的输入。所述第二与非门的两个输入分别接第二d触发器的输出以及第一与非门的输出,第二与非门的输出接第四与非门的输入。所述第三与非门的两个输入分别接第一与非门和第四与非门的输出,第三与非门的输出接第五与非门和第九与非门的输入。所述第四与非门的两个输入分别接第二与非门和第三与非门的输出,第四与非门的输出接第三与非门、第六与非门和第八与非门的输入以及第一反相器的输入。所述第五与非门的两个输入分别接第一d触发器的输出以及第三与非门的输出,第五与非门的输出接第七与非门的输入。所述第六与非门的两个输入分别接第二d触发器的输出以及第四与非门的输出,第六与非门的输出接第七与非门的输入。所述第七与非门的两个输入分别接第五与非门和第六与非门的输出,第七与非门的输出接start;第八与非门的两个输入分别接第一d触发器的输出以及第四与非门的输出,第八与非门的输出接第十与非门的输入。所述第九与非门的两个输入分别接第二d触发器的输出以及第三与非门的输出,第九与非门的输出接第十与非门的输入。所述第十与非门的两个输入分别接第八与非门和第九与非门的输出,第十与非门的输出接stop。所述第一反相器的输入接第四与非门的输出,

第一反相器的输出接第二反相器的输入;第二反相器的输入接第一反相器的输出,第二反相器的输出接sign。

[0046]

所述时间数字转换器包含第一量化单元~第六十四量化单元和解码器;其中,所述第一量化单元的两个输入分别接外部信号start、stop,第一量化单元的三个输出分别接第二量化单元的两个输入以及解码器的一个输入;所述第二量化单元~第六十四量化单元的结构相同,并与第一量化单元串联形成所述时间数字转换器;所述第一量化单元~第六十四量化单元的输出接解码器的输入,解码器的输出接第一减法器的正端。

[0047]

所述第一量化单元包含第一延时单元、第二延时单元和d触发器;所述第一延时单元接外部输入start,第一延时单元的输出接d触发器的一个输入以及第二量化单元的第一延时单元;所述第二延时单元接外部输入stop,第二延时单元的输出接d触发器的时钟端输入以及第二量化单元的第二延时单元;所述d触发器的两个输入分别接第一延时单元和第二延时单元的输出,所述d触发器的输出接解码器。

[0048]

所述自适应步长/带宽控制算法模块包含第二加法器、第二寄存器、分频器、第一数字比较器、第二数字比较器、计数器以及或门。其中,所述第二加法器的一个输入接外部sign信号、另一个输入接第二寄存器的输出,第二加法器的输出接第二寄存器的输入以及第一比较器的负端输入、第二数字比较器的正端输入。所述第二寄存器的两个输入分别接第二加法器的输出和或门的输出,第二寄存器另外一个输入接外部时钟信号fref,第二寄存器的输出接第二加法器的输入。所述分频器的输入接外部时钟信号fref,分频器的输出接第一数字比较器和第二数字比较器的时钟端输入。所述第一数字比较器的正端输入接外部输入ntarget1,第一数字比较器的负端输入接加法器的输出,第一数字比较器的时钟端输入接分频器输出,第一数字比较器的输出接或门的一个输入。所述第二数字比较器的正端输入接第二加法器的输出,第二数字比较器的负端输入接外部输入ntarget2,第二数字比较器的时钟端输入接分频器输出,第二数字比较器的输出接或门的另一个输入。所述或门的两个输入分别接第一数字比较器和第二数字比较器的输出,或门的输出接第二寄存器的一个输入以及sel。

[0049]

所述lms算法模块包含第二乘法器、第三乘法器、mux、第三加法器以及第三寄存器。其中,所述第二乘法器的两个输入分别接外部输入p[k]、e[k],第二乘法器的输出接第三乘法器的一个输入;所述mux的两个输入分别接外部输入γ0、γ1,mux的选择端接外部输入sel,mux的输出接第三乘法器的另一个输入;所述第三乘法器的两个输入分别接mux的输出和第二乘法器的输出,第三乘法器的输出接第三加法器的一个输入;所述第三加法器的两个输入分别接第三乘法器的输出以及第三寄存器的输出,第三加法器的输出接第三寄存器的输入以及输出端out;所述第三寄存器的输入接第三加法器的输出,第三寄存器的输出接第三加法器的一个输入。

[0050]

所述数字环路滤波器包括第四乘法器、第五乘法器、第四加法器、第五加法器、第四寄存器、第五寄存器,第一mux及第二mux。其中,所述第四乘法器的两个输入分别接外部数字信号e[k]以及第一mux的输出,第四乘法器的输出接第五加法器;所述第五乘法器的两个输入分别接外部数字信号e[k]以及第二mux的输出,第五乘法器的输出接第四加法器。所述第一mux的两个输入分别接外部输入α0、α1,第一mux的选择端接外部输入sel,第一mux的输出接第四乘法器的输入;所述第二mux的两个输入分别接外部输入β0、β1,第二mux的选择

端接外部输入sel,第二mux的输出接第五乘法器的输入。所述第四加法器的两个输入分别接第五乘法器的输出以及第四寄存器的输出,第四加法器的输出接第四寄存器的输入。所述第四寄存器的两个输入分别接外部时钟fref与第四加法器的输出,第四寄存器的输出接第四加法器的输入以及第五加法器的输入。所述第五加法器的两个输入分别接第四寄存器的输出以及第四乘法器的输出;第五加法器的输出接第五寄存器的输入。所述第五寄存器的两个输入分别接第五加法器的输出以及外部时钟信号fref,第五寄存器的输出接out。

[0051]

所述数控振荡器包括第一nmos管nm1、第二nmos管nm2、第一pmos管pm1、第二pmos管pm2、第一电阻r1、第二电阻r2、第一电容c1、第二电容c2、粗调电容阵列、精调电容阵列及电感l1。其中,所述电感l1的左右两端分别接vp、vn,电感l1的中心抽头接vdd;所述第一nmos管nm1的栅极接vn以及第一电容c1的一端,nm1的漏极接vp、第二nmos管nm2的栅极和第二电容c2的一端,nm1的源极接第一pmos管pm1的源极;所述第二nmos管nm2的栅极接vp以及第二电容c2的一端,nm2的漏极接vn、第一nmos管nm1的栅极和第一电容c1的一端,nm2的源极接第二pmos管pm2的源极。所述第一pmos管pm1的栅极接第二电容c2的另一端以及第一电阻r1的一端,pm1的源极接第一nmos管nm1的源极,pm1的漏极接gnd;所述第二pmos管pm2的栅极接第一电容c1的另一端以及第二电阻r2的一端,pm2的源极接第二nmos管nm2的源极,pm2的漏极接gnd。所述第一电阻r1的一端接pm1的栅极以及第二电容c2的另一端,第一电阻r1的另一端接gnd;所述第二电阻r2的一端接pm2的栅极以及第一电容c1的另一端,第二电阻r2的另一端接gnd。所述第一电容c1的一端接nm1的栅极以及vn,第一电容c1的另一端接pm2的栅极以及r2的一端;所述第二电容c2的一端接nm2的栅极以及vp,第二电容c2的另一端接pm1的栅极以及r1的一端。

[0052]

所述精调电容阵列由第一组的第三pmos管和第四pmos管以及第二~第八组结构相同但尺寸不同的阵列组成,第一组的第三pmos管和第四pmos管的源极、漏极都接外部输入信号df[0],第三pmos管的栅极接vp,第四pmos管的栅极接vn;第二组到第八组精调电容阵列都采用相同结构,与第一组共同形成阵列。

[0053]

所述粗调电容阵列由第一组的nmos管、第三电容、第四电容、第三电阻、第四电阻、反相器以及第二组粗调电容阵列~第五组粗调电容阵列组成,所述第三电容的一端接vp、另一端接第三电阻的一端与第三nmos管的源极;所述第三电阻的另一端接第一反相器的输出及第四电阻的一端;所述第三nmos管的栅极接外部输入dc[0],第三nmos管的漏极接第四电阻的另一端以及第四电容的一端;所述第四电容的另一端接vn;所述第一反相器的输入接外部输入dc[0];第二组到第五组粗调电容阵列都采用相同结构,与第一组共同形成阵列。

[0054]

所述多模分频器包含第一2/3分频器~第六2/3分频器,其中,所述第一2/3分频器的三个输入端分别接外部输入fin、p0以及第二2/3分频器的输出,第一2/3分频器的输出接第二2/3分频器的一个输入;所述第二2/3分频器的三个输入端分别接外部输入p1、第一2/3分频器的输出以及第三2/3分频器的输出,第二2/3分频器的两个输出分别接第一2/3分频器和第三2/3分频器的输入;所述第三2/3分频器的三个输入端分别接外部输入p2、第二2/3分频器的输出以及第四2/3分频器的输出,第三2/3分频器的两个输出分别接第二2/3分频器和第四2/3分频器的输入;所述第四2/3分频器的三个输入端分别接外部输入p3、第三2/3分频器的输出以及第五2/3分频器的输出,第四2/3分频器的两个输出分别接第三2/3分频

器和第五2/3分频器的输入;所述第五2/3分频器的三个输入端分别接外部输入p4、第四2/3分频器的输出以及第六2/3分频器的输出,第五2/3分频器的两个输出分别接第四2/3分频器和第六2/3分频器的输入;所述第六2/3分频器的三个输入端分别接外部输入p5、第五2/3分频器的输出以及电源电压vdd,第六2/3分频器的两个输出分别接第五2/3分频器的输入以及输出端fout。

[0055]

所述σδ调制器包括一个19位cla、两个24位cla、一个5比特移位模块、四个1位寄存器、一个19位寄存器、两个24位寄存器及噪声消除电路;其中,所述19位cla的两个输入端分别接第四寄存器4的1比特输出端和第五寄存器5的19比特输出端,19位cla的19比特输出端接5比特移位模块的19比特输入端,19位cla的1比特输出端分别接第一寄存器1和第五寄存器5的1比特输入端;所述5比特移位模块的24比特输出端接第一24位cla的24比特输入端;所述第一24位cla的另外两个输入端分别接19位cla的1比特输出端和第六寄存器6的24比特输出端,第一24位cla的1比特输出端分别接第二寄存器2和第二24位cla的1比特输入端,第一24位cla的24比特输出端接第二24位cla的24比特输入端;所述第二24位cla的另外两个输入端分别接24位cla的1比特输出端和第七寄存器7的24比特输出端,第二24位cla的1比特输出端接第三寄存器3的1比特输入端,第二24位cla的24比特输出端接第七寄存器7的24比特输入端;所述噪声消除电路的三个输入端分别接第一寄存器1、第二寄存器2和第三寄存器3的1比特输出端,噪声消除电路的4比特输出端接y。

[0056]

下面将结合具体的附图进行详细说明。

[0057]

如图1所示,鉴频鉴相器检测参考信号与分频器输出的信号并产生两带相位差信息的信号和频率提前或落后的符号信息,然后时间数字转换器将相位差信息转换为数字信号再通过环路进行调谐。鉴频鉴相器产生的频率提前或落后的符号信息输入到自适应步长/带宽控制算法模块,从而产生选择信号sel,产生的sel信号进行环路带宽控制和lms算法步长控制,从而实现加快环路锁定时间、降低带内相位噪声以及抑制小数杂散的性能。

[0058]

外部输入的频率控制字fcw与σδ调制器的输出进行相减产生σδ调制器的量化误差,所产生的量化误差通过第一加法器和第一寄存器继续累加产生数字序列p[k]。量化误差的数字序列p[k]作为lms算法模块的输入来拟合从多模分频器到时间数字转换器的传输函数,lms算法模块的输出与数字序列p[k]相乘后与时间数字转换器做差产生期望误差序列e[k],环路通过自适应步长/带宽控制算法模块来合理选择lms的收敛步长,从而既可以实现较小的期望误差序列e[k]来抑制σδ调制器导致的小数杂散,又可以加快lms算法的收敛。同时,自适应步长/带宽控制算法模块产生的选择信号合理选择数字环路滤波器不同的增益系数来实现不同的环路带宽,从而加快锁相环的锁定以及抑制带内相位噪声的性能。

[0059]

图2为鉴频鉴相器的电路图,其采用边沿采样式结构来实现提取参考信号与分频器输出的信号之间的相位差。为避免参考信号提前或落后分频器输出的信号,时间数字转换器能够正常量化相位差,鉴频鉴相器后面加入由与非门构成的锁存电路对传统鉴频鉴相器产生的up/dn信号进行处理,从而产生start、stop以及sign信号。无论参考信号提前或落后分频器输出的信号,start信号的脉冲宽度总是大于stop信号,可以避免将start、stop信号接在时间数字转换器时,时间数字转换器量化出错。当参考信号的频率大于分频器输出信号的频率时,鉴频鉴相器输出的sign信号一直为“1”;当参考信号的频率小于分频器输出

信号频率时,鉴频鉴相器输出的sign信号一直为“0”。

[0060]

图3(a)和图3(b)分别是时间数字转换器与量化单元的电路图,其采用游标卡尺结构来实现较好的量化线性度和较高的量化精度。量化单元的电路图中第一延时单元接start信号,第二延时单元接stop信号,第一延时单元的延时时间大于第二延时单元。因此,时间数字转换器就可以通过stop信号对start信号进行采样,从而实现量化相位误差。时间数字转换器的量化精度为两个不同延时单元的延时时间之差,量化精度越高,则带内相位噪声越好。为实现较高的量化精度,采用两个反相器作为延时单元,并通过设置延时单元不同的尺寸,从而可以实现亚皮秒级别的分辨率。

[0061]

图4为自适应步长/带宽控制算法模块的电路图,外部输入的sign信号通过第二加法器和第二寄存器累加后输出到第一数字比较器和第二数字比较器。fref经过分频器n后为两个数字比较器提供时钟fref_n,再进行数字比较。第一数字比较器、第二数字比较器的两个阈值的关系为n

target2

》n

target1

,设置n

target1

为1,n

target2

为n-1(n为分频器的分频比)。当sign信号一直为“0”时,锁相环没有锁定,累加器的输出一直为“0”,此时或门的输出sel为“1”;当sign信号一直为“1”时,锁相环没有锁定,累加器的输出为“n”,此时或门的输出sel为“1”;当sign信号交替出现“0”与“1”时,锁相环锁定,累加器的输出在“n/2”附近,此时或门的输出sel为“0”。因此,电路产生的sel信号就可以根据锁相环的锁定状态来自适应控制lms的收敛步长或数字环路滤波器的带宽,从而实现较好的性能。

[0062]

图5为lms算法模块的电路图,外部输入的数字序列p[k]和期望误差序列e[k]作为lms算法模块的第二乘法器的两个输入。sel信号控制lms算法的收敛步长γ0、γ1与第二乘法器的输出做乘后累加,从而使lms算法拟合的传输函数逐次逼近原系统的传输函数。sel信号通过环路的锁定状态控制不同的收敛步长,从而既可以加快lms算法收敛,又可以减小期望误差序列来抑制小数杂散。

[0063]

图6为数字环路滤波器的电路图,其采用比例积分型结构来降低电路的复杂性。外部输入的误差序列e[k]经过第四乘法器与第一mux的输出做乘,从而实现比例路径;误差序列e[k]经过第五乘法器与第二mux的输出做乘,然后通过第四加法器和第四寄存器进行累加,从而实现积分路径。第一mux和第二mux通过外部输入的sel信号来选择不通过增益系数,以实现宽带来加快环路锁定和窄带来抑制带内相位噪声。误差序列e[k]经过比例和积分路径后经过第五加法器相加实现整个滤波器的功能,第五加法器的输出通过寄存器作为输出,从而避免第五加法器造成的毛刺对环路的影响。

[0064]

图7为数控振荡器的电路图,其采用噪声循环结构来减少注入到谐振器的噪声电流,进而实现较低的相位噪声。nm1、电容c2和pm1构成一个噪声循环通路,当nm1产生噪声时,噪声电流会通过nm1、电容c2、pm1构成一个循环环路,使一部分噪声电流在nm1中循环,另一部分则会注入到谐振腔中形成相位噪声,从而减少了由nm1导致的相位噪声;同样,当pm1产生噪声电流时,一部分噪声电流会经过nm1到达谐振电路,产生相位噪声,另外一部分则循环回到pm1上,最终到达地面。数控振荡器由5位开关电容组成的粗调电容阵列和8位mos电容组成的精调阵列组成,nmos管nm1、nm2为振荡器提供负阻来补偿谐振腔的能量损耗。粗调电容阵列由mim电容、电阻、nmos管、反相器来覆盖输出的频率范围,精调电容阵列由两个pmos电容串联来实现较小的电容跳变。

[0065]

图8(a)和图8(b)分别是多模分频器与2/3分频单元的电路图,多模分频器采用2/3

级联结构来覆盖所设计的分频比。2/3分频单元由tspc结构的d触发器与门电路构成,在所覆盖的频率范围内,多模分频器既可以正常工作,又可以节省功耗。

[0066]

图9为σδ调制器的电路图,其采用mash 1-1-1结构来产生[-3,4]的数字序列的输出,可以随机化多模分频器的分频比,同时将量化噪声推到高频,然后通过环路的低通滤波器滤除。

[0067]

综上所述,本发明在现有技术及电路结构的基础上进行了改进与优化,通过检测环路的锁定状态来自适应并行调整lms算法的步长与数字环路滤波器的带宽,当锁相环环路未锁定时,电路选择较大的lms步长和数字环路滤波器的增益系数,从而可以缩短lms算法收敛时间和锁相环的锁定时间;当锁相环环路锁定时,电路选择较小的lms步长和数字环路滤波器的增益系数,从而可以抑制小数杂散和带内相位噪声。

[0068]

以上实施例仅用以说明本发明的技术方案而非限制,尽管参照较佳实施例对本发明进行了详细说明,本领域的普通技术人员应当理解,可以对本发明的技术方案进行修改或者等同替换,而不脱离本发明技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1