半导体结构的制造方法与流程

本公开实施例涉及半导体制造,特别涉及一种半导体结构的制造方法。

背景技术:

1、动态随机存取存储器(dynamic random access memory,简称dram)是一种半导体存储器,通常包括由多个重复的存储单元组成的阵列区和位于阵列区外围的外围区。

2、目前,在外围区和阵列区形成接触窗时,一方面容易在外围区刻蚀过量,导致漏电现象的出现;另一方面又容易在阵列区出现刻蚀不够,导致断路现象的出现。以上都会造成器件出现失效的问题。

技术实现思路

1、本公开实施例提供一种半导体结构的制造方法,至少有利于解决在阵列区存在的刻蚀不够问题以及外围区存在的刻蚀过量问题,以解决相应的器件失效问题,提高半导体结构的可靠性。

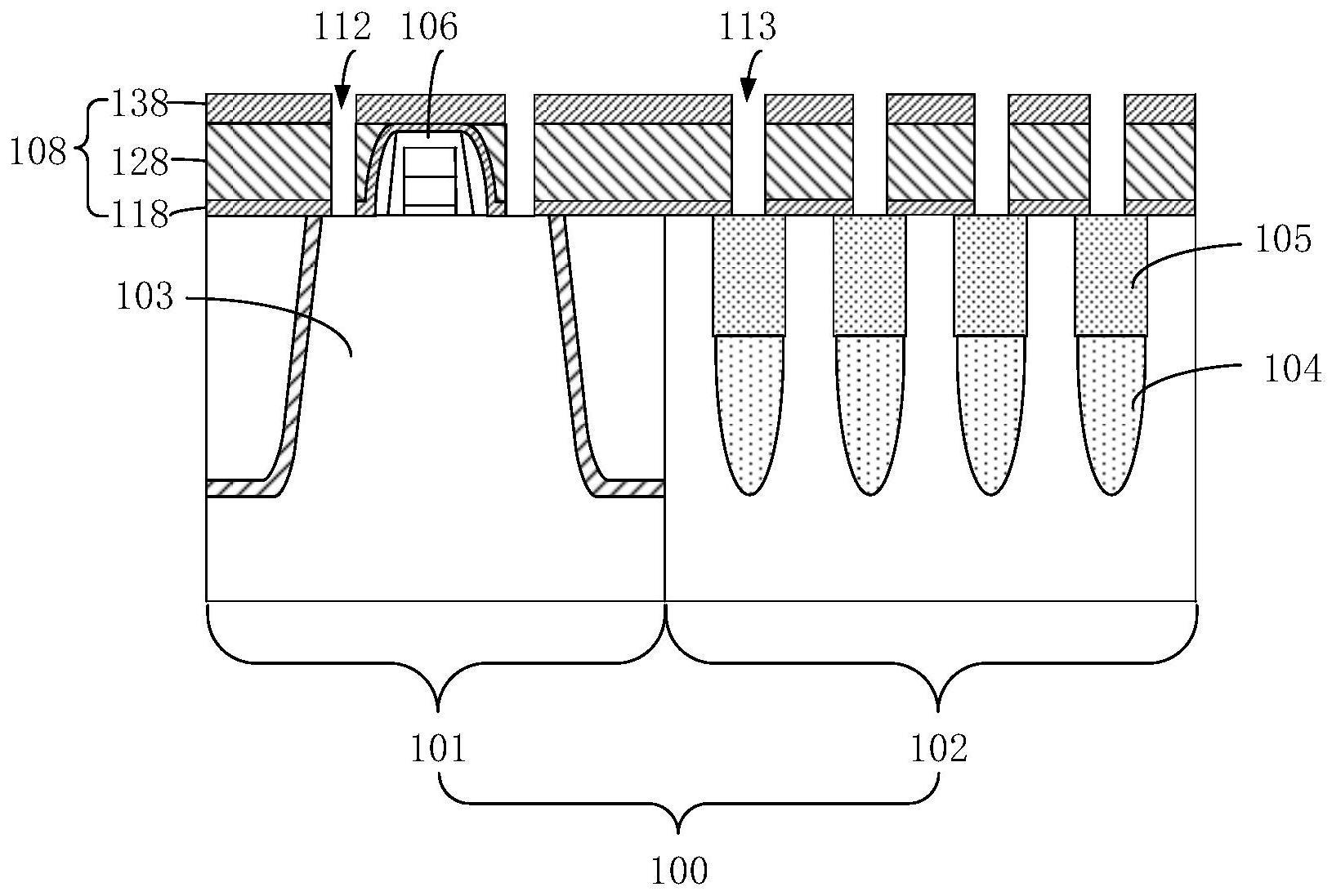

2、根据本公开一些实施例,本公开实施例提供一种半导体结构的制造方法,包括:提供衬底,所述衬底包括阵列区和外围区,所述外围区的所述衬底包括有源层,所述阵列区的所述衬底内具有埋入式字线和介电层,所述介电层位于所述埋入式字线上;在所述衬底上形成第一掩膜层,所述第一掩膜层覆盖所述外围区和所述阵列区;在所述第一掩膜层上形成阻挡层,所述阻挡层至少覆盖所述外围区;在所述阻挡层上形成第二掩膜层,所述第二掩膜层覆盖所述外围区和所述阵列区;在所述外围区依次刻蚀所述第二掩膜层、所述阻挡层以及所述第一掩膜层以形成第一通孔,并同时在所述阵列区刻蚀所述第二掩膜层、所述第一掩膜层以及所述介电层以形成第二通孔,所述第一通孔和所述第二通孔分别暴露出所述有源层和所述埋入式字线。

3、在一些实施例中,形成所述阻挡层的步骤,包括:在所述第一掩膜层上形成阻挡膜,所述阻挡膜覆盖所述阵列区和所述外围区;减薄或者去除所述阵列区的所述阻挡膜,使得剩余的所述阻挡膜构成所述阻挡层。

4、在一些实施例中,形成所述阻挡层的步骤,包括:在所述第一掩膜层上形成第一阻挡层,所述第一阻挡层覆盖所述阵列区和所述外围区;去除或者减薄所述外围区的所述第一阻挡层;在所述外围区的所述第一掩膜层或者所述外围区中剩余的所述第一阻挡层上形成第二阻挡层,所述第二阻挡层以及剩余的所述第一阻挡层构成所述阻挡层。

5、在一些实施例中,形成所述第二阻挡层的步骤,包括:在所述阵列区的所述第一阻挡层以及所述外围区的所述第一掩膜层或者所述外围区中剩余的所述第一阻挡层上形成第二阻挡层;对所述第二阻挡层进行平坦化处理,去除所述阵列区的所述第二阻挡层,并使所述外围区的所述第二阻挡层与所述阵列区的所述第一阻挡层平齐。

6、在一些实施例中,在刻蚀形成所述第一通孔和所述第二通孔的步骤中,所述第二阻挡层的刻蚀速度小于所述第一阻挡层的刻蚀速度。

7、在一些实施例中,在所述衬底上形成所述第一掩膜层之前,还包括:在所述衬底上形成隔离层,所述隔离层覆盖所述外围区和所述阵列区;在所述衬底上形成所述第一掩膜层的步骤,包括:在所述隔离层上形成所述第一掩膜层。

8、在一些实施例中,所述隔离层包括依次层叠的第一氮化层、氧化层以及第二氮化层。

9、在一些实施例中,所述阻挡层的材料包括无定形碳、氧化物、氮化物以及多晶硅中的至少一种。

10、在一些实施例中,形成所述第一通孔和所述第二通孔的步骤,包括:在所述第二掩膜层上形成图形化的光刻胶层;以所述图形化的光刻胶层作为掩膜,刻蚀所述第二掩膜层,形成图形化的第二掩膜层;以所述图形化的第二掩膜层作为掩膜,在所述外围区刻蚀所述阻挡层和所述第一掩膜层以形成第一通孔,并同时在所述阵列区刻蚀所述第一掩膜层和所述介电层以形成第二通孔。

11、在一些实施例中,在形成所述第一通孔和所述第二通孔的步骤之后,还包括:在所述第一通孔和所述第二通孔中分别形成第一导电结构和第二导电结构,所述第一导电结构与所述有源层接触,所述第二导电结构与所述埋入式字线接触。

12、在一些实施例中,所述第一掩膜层包括旋涂硬掩膜、氧化物、氮化物以及多晶硅中的至少一种,所述第二掩膜层包括氮氧化物或者氧化物中的至少一种。

13、在一些实施例中,所述介电层的材料包括二氧化硅。

14、在一些实施例中,所述有源层上还形成有栅极结构。

15、在一些实施例中,所述第一通孔的底部沿所述衬底的厚度方向到所述第二通孔的底部的距离大于60nm。

16、本公开实施例提供的技术方案至少具有以下优点:

17、通过在第一掩膜层和第二掩膜层之间形成至少覆盖外围区的阻挡层,以利用阻挡层带来的刻蚀阻挡作用,差异化在外围区形成第一通孔的刻蚀深度和在阵列区形成第二通孔的刻蚀深度,即在刻蚀过程中,使得阵列区刻蚀至第二通孔露出介电层时,而外围区的第一通孔还未露出有源层,在刻蚀完成后,使得第一通孔和第二通孔分别暴露出有源层和埋入式字线,同时解决了外围区刻蚀过量的问题和阵列区的刻蚀不够的问题,从而解决了相应的器件失效问题,提高了半导体结构的可靠性。

技术特征:

1.一种半导体结构的制造方法,其特征在于,包括:

2.根据权利要求1所述的制造方法,其特征在于,形成所述阻挡层的步骤,包括:

3.根据权利要求1所述的制造方法,其特征在于,形成所述阻挡层的步骤,包括:

4.根据权利要求3所述的制造方法,其特征在于,形成所述第二阻挡层的步骤,包括:

5.根据权利要求3所述的制造方法,其特征在于,在刻蚀形成所述第一通孔和所述第二通孔的步骤中,所述第二阻挡层的刻蚀速度小于所述第一阻挡层的刻蚀速度。

6.根据权利要求1所述的制造方法,其特征在于,在所述衬底上形成所述第一掩膜层之前,

7.根据权利要求6所述的制造方法,其特征在于,所述隔离层包括依次层叠的第一氮化层、氧化层以及第二氮化层。

8.根据权利要求1所述的制造方法,其特征在于,所述阻挡层的材料包括无定形碳、氧化物、氮化物以及多晶硅中的至少一种。

9.根据权利要求1所述的制造方法,其特征在于,形成所述第一通孔和所述第二通孔的步骤,包括:

10.根据权利要求1所述的制造方法,其特征在于,在形成所述第一通孔和所述第二通孔的步骤之后,还包括:

11.根据权利要求1所述的制造方法,其特征在于,所述第一掩膜层包括旋涂硬掩膜、氧化物、氮化物以及多晶硅中的至少一种,所述第二掩膜层包括氮氧化物或者氧化物中的至少一种。

12.根据权利要求1所述的制造方法,其特征在于,所述介电层的材料包括二氧化硅。

13.根据权利要求1所述的制造方法,其特征在于,所述有源层上还形成有栅极结构。

14.根据权利要求1所述的制造方法,其特征在于,所述第一通孔的底部沿所述衬底的厚度方向到所述第二通孔的底部的距离大于60nm。

技术总结

本公开实施例涉及半导体领域,提供一种半导体结构的制造方法,包括:提供衬底,衬底包括阵列区和外围区,外围区的衬底包括有源层,阵列区的衬底内具有埋入式字线和介电层,介电层位于埋入式字线上;在衬底上形成第一掩膜层,第一掩膜层覆盖外围区和阵列区;在第一掩膜层上形成阻挡层,阻挡层至少覆盖外围区;在阻挡层上形成第二掩膜层,第二掩膜层覆盖外围区和阵列区;在外围区依次刻蚀第二掩膜层、阻挡层以及第一掩膜层以形成第一通孔,并同时在阵列区刻蚀第二掩膜层、第一掩膜层以及介电层以形成第二通孔,第一通孔和第二通孔分别暴露出有源层和埋入式字线,从而同时解决不同区域分别存在的刻蚀过量和刻蚀不够的问题。

技术研发人员:常苏生,修春雨,宛伟

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!