半导体结构及其制备方法与流程

本公开实施例涉及半导体,特别是涉及一种半导体结构及其制备方法。

背景技术:

1、由于漏极的高浓度掺杂,导致漏极附近的横向电场增大,导致gidl(gate-induceddrain leakage,栅诱导漏极泄漏电流)。随着dram(dynamic random access memory,动态随机存取存储器)特征尺寸的缩小,dram中存储晶体管的gidl会增大,影响存储晶体管的性能,为了提高存储晶体管的性能,需要控制存储晶体管的阈值电压。

技术实现思路

1、本公开实施例提供了一种半导体结构及其制备方法,可以优化栅诱导漏极泄露电流和阈值电压。

2、本公开提供一种半导体结构的制备方法,包括:

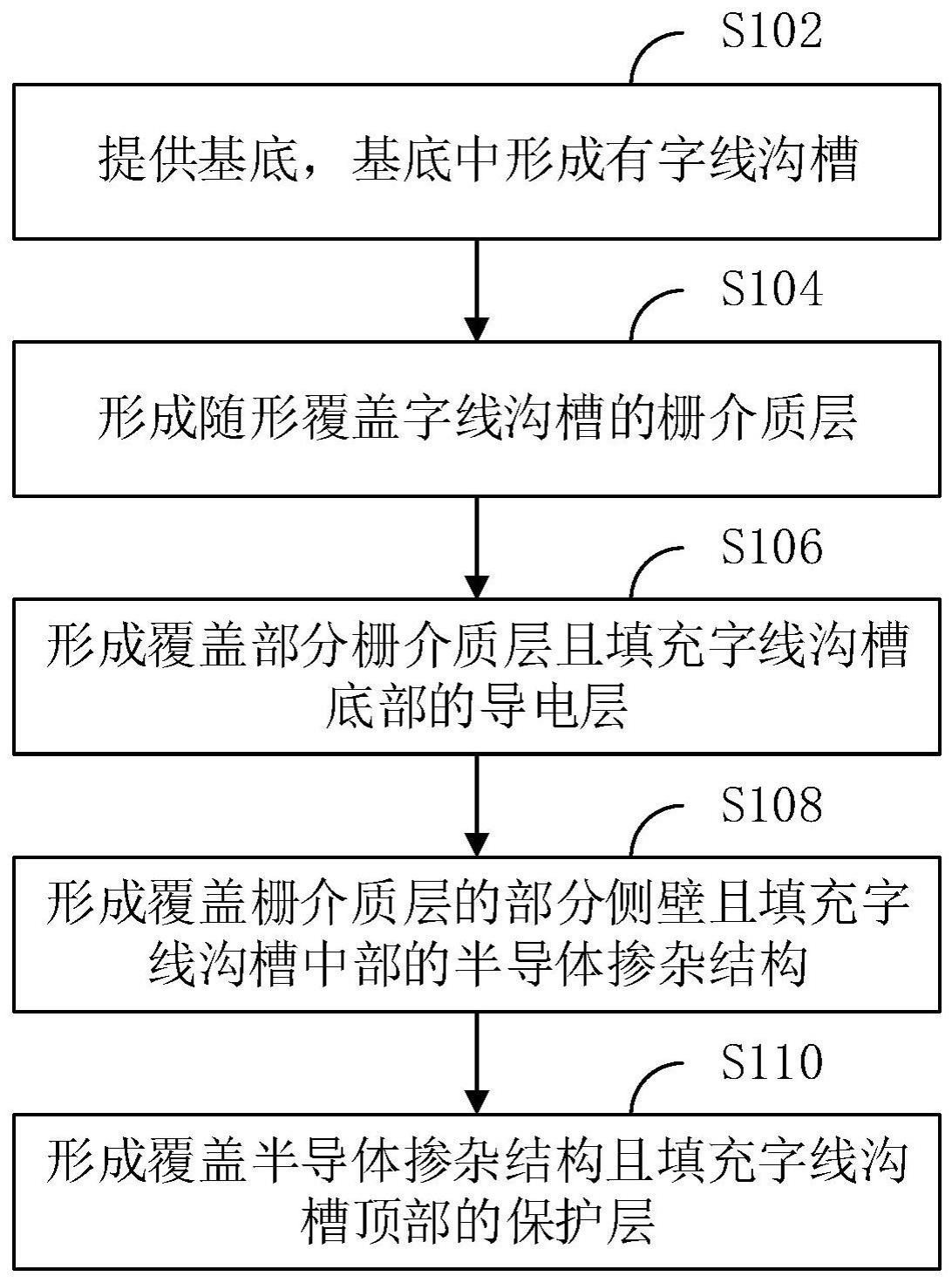

3、提供基底,基底中形成有字线沟槽;

4、形成随形覆盖字线沟槽的栅介质层;

5、形成覆盖部分栅介质层且填充字线沟槽底部的导电层;

6、形成覆盖栅介质层的部分侧壁且填充字线沟槽中部的半导体掺杂结构;

7、形成覆盖半导体掺杂结构且填充字线沟槽顶部的保护层;

8、其中,半导体掺杂结构包括第一半导体掺杂层和第二半导体掺杂层,第一半导体掺杂层覆盖栅介质层的部分侧壁,第二半导体掺杂层覆盖第一半导体掺杂层的侧壁且覆盖导电层的顶面,第二半导体掺杂层的掺杂浓度小于第一半导体掺杂层的掺杂浓度。

9、在其中一个实施例中,形成覆盖栅介质层的部分侧壁且填充字线沟槽中部的半导体掺杂结构,包括:

10、形成随形覆盖栅介质层的侧壁和导电层的顶面的第一半导体掺杂材料层;

11、回刻蚀第一半导体掺杂材料层,保留位于栅介质层靠近导电层的侧壁上的第一半导体掺杂材料层作为第一半导体掺杂层;

12、形成覆盖第一半导体掺杂层且填充字线沟槽的第二半导体掺杂材料层;

13、回刻蚀第二半导体掺杂材料层,保留位于字线沟槽中部的第二掺杂材料层作为第二半导体掺杂层。

14、在其中一个实施例中,形成覆盖第一半导体掺杂层且填充字线沟槽的第二半导体掺杂材料层,包括:

15、形成依次层叠的多个半导体掺杂材料子层,其中,后一个半导体掺杂材料子层随形覆盖前一个半导体掺杂材料子层,后一个半导体掺杂材料子层的掺杂浓度大于前一个半导体掺杂材料子层的掺杂浓度,第一个半导体掺杂材料子层随形覆盖第一半导体掺杂层和导电层的顶面。

16、在其中一个实施例中,在沿字线沟槽底部指向字线沟槽顶部且经过第二半导体掺杂层的顶面中心的方向上,第二半导体掺杂层的掺杂浓度逐渐增大;

17、在沿第二半导体掺杂层的顶面中心指向第二半导体掺杂层的顶面边缘的方向上,第二半导体掺杂层的掺杂浓度逐渐减小。

18、在其中一个实施例中,形成覆盖栅介质层的部分侧壁且填充字线沟槽中部的半导体掺杂结构,包括:

19、形成覆盖第一半导体掺杂层的顶面和第二半导体掺杂层的顶面且填充字线沟槽的第三半导体掺杂材料层;

20、回刻蚀第三半导体掺杂材料层,保留位于第一半导体掺杂层的顶面和第二半导体掺杂层的顶面上的第三半导体掺杂材料层作为第三半导体掺杂层;

21、其中,半导体掺杂结构还包括第三半导体掺杂层,第三半导体掺杂层的掺杂浓度大于或等于第一半导体掺杂层的掺杂浓度。

22、在其中一个实施例中,基底包括有源区,字线沟槽穿过有源区,半导体结构的制备方法还包括:

23、对有源区位于字线沟槽的相对两侧的部分进行掺杂,以形成源漏区,其中,源漏区与半导体掺杂结构横向交叠,且源漏区不与导电层横向交叠。

24、在其中一个实施例中,形成覆盖部分栅介质层且填充字线沟槽底部的导电层,包括:

25、形成随形覆盖栅介质层的扩散阻挡材料层;

26、形成覆盖扩散阻挡材料层且填充字线沟槽的金属材料层;

27、回刻蚀金属材料层和扩散阻挡材料层,保留位于字线沟槽底部的扩散阻挡材料层和金属材料层分别作为扩散阻挡层和金属层;

28、其中,导电层包括扩散阻挡层和金属层。

29、上述半导体结构的制备方法包括,形成覆盖栅介质层的部分侧壁且填充字线沟槽中部的半导体掺杂结构,半导体掺杂结构包括第一半导体掺杂层和第二半导体掺杂层,第二半导体掺杂层的掺杂浓度小于第一半导体掺杂层的掺杂浓度,与字线沟槽中部仅填充第一半导体掺杂层相比,半导体掺杂结构中覆盖栅介质层的部分侧壁的第一半导体掺杂层,使得半导体结构的栅诱导漏极泄漏电流保持不变,同时半导体掺杂结构中的第二半导体掺杂层的掺杂浓度小于第一半导体掺杂层的掺杂浓度,并且第二半导体掺杂层覆盖第一半导体掺杂层的侧壁和导电层的顶面,增加了半导体结构的阈值电压,提升了半导体结构(埋入式晶体管)的性能。

30、本公开还提供一种半导体结构,包括:

31、基底,基底中形成有字线沟槽;

32、栅介质层,随形覆盖字线沟槽;

33、导电层,覆盖部分栅介质层且填充字线沟槽的底部;

34、半导体掺杂结构,覆盖栅介质层的部分侧壁且填充字线沟槽的中部;

35、保护层,覆盖半导体掺杂结构且填充字线沟槽的顶部;

36、其中,半导体掺杂结构包括第一半导体掺杂层和第二半导体掺杂层,第一半导体掺杂层覆盖栅介质层的部分侧壁,第二半导体掺杂层覆盖第一半导体掺杂层的侧壁且覆盖导电层的顶面,第二半导体掺杂层的掺杂浓度小于第一半导体掺杂层的掺杂浓度。

37、在其中一个实施例中,沿字线沟槽的底部指向字线沟槽的顶部的且经过第二半导体掺杂层的顶面中心的方向上,第二半导体掺杂层的掺杂浓度逐渐增大;

38、在沿第二半导体掺杂层的顶面中心指述第二半导体掺杂层的顶面边缘的方向上,第二半导体掺杂层的掺杂浓度逐渐减小。

39、在其中一个实施例中,半导体掺杂结构还包括第三半导体掺杂层,第三半导体掺杂层覆盖第一半导体掺杂层的顶面和第二半导体掺杂层的顶面,第三半导体掺杂层的掺杂浓度大于或等于第一半导体掺杂层的掺杂浓度。

40、在其中一个实施例中,基底包括有源区,字线沟槽穿过有源区,有源区包括位于字线沟槽的相对两侧的源漏区,源漏区与半导体掺杂结构横向交叠,且源漏区不与导电层横向交叠。

41、在其中一个实施例中,第一半导体掺杂层覆盖导电层的部分顶面。

42、上述半导体结构中,半导体掺杂结构覆盖栅介质层的部分侧壁且填充字线沟槽的中部,半导体掺杂结构包括第一半导体掺杂层和第二半导体掺杂层,第二半导体掺杂层的掺杂浓度小于第一半导体掺杂层的掺杂浓度,与字线沟槽中部仅填充第一半导体掺杂层相比,覆盖栅介质层的部分侧壁的第一半导体掺杂层,使得半导体结构的栅诱导漏极泄漏电流保持不变,同时覆盖第一半导体掺杂层的侧壁和导电层的顶面、并且掺杂浓度小于第一半导体掺杂层的掺杂浓度的第二半导体掺杂层,增加了半导体结构的阈值电压,提升了半导体结构(埋入式晶体管)的性能。

技术特征:

1.一种半导体结构的制备方法,其特征在于,包括:

2.根据权利要求1所述的制备方法,其特征在于,所述形成覆盖所述栅介质层的部分侧壁且填充所述字线沟槽中部的所述半导体掺杂结构,包括:

3.根据权利要求2所述的制备方法,其特征在于,所述形成覆盖所述第一半导体掺杂层且填充所述字线沟槽的所述第二半导体掺杂材料层,包括:

4.根据权利要求3所述的制备方法,其特征在于,在沿所述字线沟槽底部指向所述字线沟槽顶部且经过所述第二半导体掺杂层的顶面中心的方向上,所述第二半导体掺杂层的掺杂浓度逐渐增大;

5.根据权利要求1所述的制备方法,其特征在于,所述形成覆盖所述栅介质层的部分侧壁且填充所述字线沟槽中部的所述半导体掺杂结构,还包括:

6.根据权利要求1所述的制备方法,其特征在于,所述基底包括有源区,所述字线沟槽穿过所述有源区,所述制备方法还包括:

7.根据权利要求1所述的制备方法,其特征在于,形成覆盖部分所述栅介质层且填充所述字线沟槽底部的所述导电层,包括:

8.一种半导体结构,其特征在于,包括:

9.根据权利要求8所述的半导体结构,其特征在于,沿所述字线沟槽的底部指向所述字线沟槽的顶部的且经过所述第二半导体掺杂层的顶面中心的方向上,所述第二半导体掺杂层的掺杂浓度逐渐增大;

10.根据权利要求8所述的半导体结构,所述半导体掺杂结构还包括第三半导体掺杂层,所述第三半导体掺杂层覆盖所述第一半导体掺杂层的顶面和所述第二半导体掺杂层的顶面,所述第三半导体掺杂层的掺杂浓度大于或等于所述第一半导体掺杂层的掺杂浓度。

11.根据权利要求8所述的半导体结构,所述基底包括有源区,所述字线沟槽穿过所述有源区,所述有源区包括位于所述字线沟槽的相对两侧的源漏区,所述源漏区与所述半导体掺杂结构横向交叠,且所述源漏区不与所述导电层横向交叠。

12.根据权利要求8所述的半导体结构,其特征在于,所述第一半导体掺杂层覆盖所述导电层的部分顶面。

技术总结

本公开实施例涉及一种半导体结构及其制备方法。该方法包括:提供基底,基底中形成有字线沟槽;形成随形覆盖字线沟槽的栅介质层;形成覆盖部分栅介质层且填充字线沟槽底部的导电层;形成覆盖栅介质层的部分侧壁且填充字线沟槽中部的半导体掺杂结构;形成覆盖半导体掺杂结构且填充字线沟槽顶部的保护层;其中,半导体掺杂结构包括第一半导体掺杂层和第二半导体掺杂层,第一半导体掺杂层覆盖栅介质层的部分侧壁,第二半导体掺杂层覆盖第一半导体掺杂层的侧壁且覆盖导电层的顶面,第二半导体掺杂层的掺杂浓度小于第一半导体掺杂层的掺杂浓度,提升了半导体结构的性能。

技术研发人员:孔令滔,王梓杰,汪治城,何家庆

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!