固态摄像装置和电子设备的制作方法

1.本发明涉及固态摄像装置和电子设备。

背景技术:

2.在互补金属氧化物半导体(cmos:complementary metal oxide semiconductor)型固态摄像装置(以下称为cmos图像传感器,或简称为图像传感器)中,将在光电转换单元(光接收单元)中产生的信号电荷在浮动扩散区域(浮动扩散部,fd)中转换为电压。通过由放大晶体管构成的源极跟随器电路,将在fd中转换的电压作为输出电压(也称为像素信号)读出。

3.假设信号检测电容为c,并且对应于光接收信号的信号电荷量为q,则像素的输出电压v由v=q/c给出。因此,如果信号检测电容c小,则可以增大输出电压v,也就是说,可以提高灵敏度。

4.因此,在现有技术中,已经通过构造如下的像素并且减小电容元件的电容来实现高灵敏度的信号输出,该像素包括:光电转换元件,其一端接地;源极接地型放大晶体管,其中,栅极电极连接到光电转换元件的另一端,源极电极接地,且漏极电极连接到负载电路;电容元件,其连接在放大晶体管的漏极电极和栅极电极之间;以及复位晶体管,其与电容元件并联连接。

5.引用列表

6.专利文献

7.专利文献1:日本专利申请特开第2008

‑

271280号

技术实现要素:

8.技术问题

9.然而,随着近年来像素的进一步微细化,从各个像素获得具有足够电压值的信号电压变得更加困难。当输出电压小时,噪声成分占输出电压的比率增大,结果,由于输出图像受到噪声的影响而导致图像质量劣化的问题。

10.因此,本发明提供了能够抑制图像质量劣化的固态摄像装置和电子设备。

11.解决问题的技术方案

12.为了解决上述问题,根据本发明的一方面的固态摄像装置包括:第一垂直信号线和第二垂直信号线;电流镜像电路,其连接到所述第一垂直信号线和所述第二垂直信号线;第一单位像素,其连接到所述第一垂直信号线;第二单位像素,其连接到所述第二垂直信号线;第一单位单元,其连接到所述第一垂直信号线;第二单位单元,其连接到所述第二垂直信号线;电流供应线,其连接到所述第一单位像素和所述第二单位像素以及所述第一单位单元和所述第二单位单元;以及恒流电路,其连接到所述电流供应线,其中,所述第一单位像素的第一放大晶体管、所述第二单位像素的第二放大晶体管、所述电流镜像电路和所述恒流电路构成第一差分放大电路,并且所述第一单位单元的第三放大晶体管、所述第二单

位单元的第四放大晶体管、所述电流镜像电路和所述恒流电路构成第二差分放大电路。

13.(作用)使用根据本发明的一个实施例的固态摄像装置,差分放大电路由第一单位单元和第二单位单元的第三放大晶体管和第四放大晶体管、电流镜像电路以及恒流电路形成,从而可以防止构成差分型放大读出构造的差分对的电流路径被消除。由此,可以保持电流消耗,从而电源电压vdd和接地电压的下降量或上升量减小,并且可以防止第一垂直信号线或第二垂直信号线的稳定时间延长。

14.在第一单位像素或第二单位像素中,当电荷从光电转换元件传输到电荷累积单元时,第一垂直信号线和第二垂直信号线与第一单位像素和第二单位像素分离,并且第一垂直信号线和第二垂直信号线的电压电平保持在复位电平,从而可以防止由于传输晶体管和电荷累积单元的电容耦合引起的馈通而在第一垂直信号线和第二垂直信号线中产生较大幅度(在传输晶体管的栅极从低(low)电平过渡到高(high)电平时,浮动扩散部通过电容耦合而放大的现象),因此可以防止第一垂直信号线和第二垂直信号线的稳定时间延长。

附图说明

15.图1是示出了cmos图像传感器的示意性构造示例的电路图。

16.图2是用于说明在cmos图像传感器中产生的噪声的图。

17.图3a是示出了cmos图像传感器中的单位像素的布置示例的图。

18.图3b是示出了在cmos图像传感器中多个单位像素共用晶体管的情况下的构造示例的图。

19.图4是用于说明寄生在cmos图像传感器的放大晶体管中的电容的图。

20.图5a是示出了源极跟随器读出构造的示例的电路图。

21.图5b是示出了差分型放大读出构造的示例的电路图。

22.图6是示出了根据第一实施例的作为安装在电子设备上的固态摄像装置的cmos图像传感器的示意性构造示例的系统构造图。

23.图7是示出了根据第一实施例的有效像素区域中的单位像素的示意性构造示例的电路图。

24.图8是示出了根据第一实施例的伪差分对形成区域中的伪单元的示意性构造示例的电路图。

25.图9是示出了根据第一实施例的差分型放大读出构造的示意性构造示例的电路图。

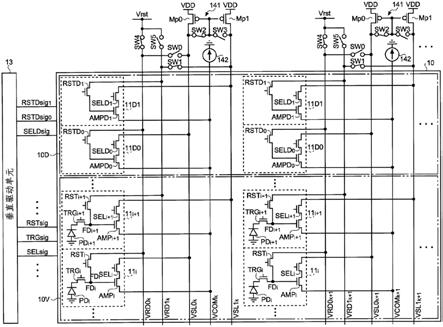

26.图10是示出了根据第一实施例的差分型放大读出构造及其外围电路的示意性构造示例的电路图。

27.图11是用于说明形成根据第一实施例的差分型放大读出构造的单位像素的组合示例的示意图。

28.图12是示出了根据第一实施例的差分型放大读出构造的驱动示例的时序图。

29.图13是示出了在根据第一实施例的包括外围电路中的开关的差分型放大读出时的驱动示例的时序图。

30.图14是用于说明形成根据第二实施例的差分型放大读出构造的单位像素的组合示例的示意图。

31.图15是示出了根据第二实施例的差分型放大读出构造及其外围电路的示意性构造示例的电路图。

32.图16是示出了在根据第二实施例的差分型放大读出时的驱动示例的时序图。

33.图17是示出了根据第二实施例的变形例的差分型放大读出构造及其外围电路的示意性构造示例的电路图。

34.图18是示出了根据第三实施例的差分型放大读出构造及其外围电路的示意性构造示例的电路图。

35.图19是示出了在根据第三实施例的差分型放大读出时的驱动示例的时序图。

36.图20是示出了根据第三实施例的变形例的差分型放大读出构造及其外围电路的示意性构造示例的电路图。

37.图21是示出了根据第四实施例的差分型放大读出构造及其外围电路的示意性构造示例的电路图。

38.图22是示出了根据第五实施例的作为安装在电子设备上的固态摄像装置的cmos图像传感器的示意性构造示例的系统构造图。

39.图23是示出了根据第五实施例的差分型放大读出构造及其外围电路的示意性构造示例的电路图。

40.图24a是示出了根据实施例的第一示例的单位像素的截面结构示例的截面图。

41.图24b是示出了根据实施例的第二示例的单位像素的截面结构示例的截面图。

42.图25a是示出了根据实施例的第一示例的cmos图像传感器的示意性结构示例的示意图。

43.图25b是示出了根据实施例的第二示例的cmos图像传感器的示意性结构示例的示意图。

具体实施方式

44.下面将基于附图详细地描述本发明的实施例。在以下实施例中,相同的部分由相同的附图标记表示,并且将不再重复多余的描述。

45.将按照下述项的顺序说明本发明。

46.1.介绍

47.2.第一实施例

48.2.1cmos图像传感器的系统构造示例

49.2.2单位像素的电路构造示例

50.2.3伪单元的电路构造示例

51.2.4单位像素的基本功能示例

52.2.5差分型放大读出构造的示例

53.2.6差分型放大读出构造的外围电路的示例

54.2.7形成差分型放大读出构造的单位像素的组合示例

55.2.8差分型放大读出构造的驱动示例

56.2.9在差分型放大读出时的驱动示例(在读出像素和参考像素之间切换)

57.2.10作用和效果

58.3.第二实施例

59.3.1形成差分型放大读出构造的单位像素的组合示例

60.3.2差分型放大读出构造的外围电路的示例

61.3.3在差分型放大读出时的驱动示例(在读出像素和参考像素之间切换)

62.3.4作用和效果

63.3.5变形例

64.4.第三实施例

65.4.1差分型放大读出构造的外围电路的示例

66.4.2在差分型放大读出时的驱动示例(在读出像素和参考像素之间切换)

67.4.3作用和效果

68.4.4变形例

69.5.第四实施例

70.5.1差分型放大读出构造的外围电路的示例

71.6.第五实施例

72.6.1cmos图像传感器的系统构造示例

73.6.2差分型放大读出构造的外围电路的示例

74.7.补充说明

75.7.1单位像素的截面结构示例

76.7.1.1第一示例

77.7.1.2第二示例

78.7.2cmos图像传感器的结构示例

79.7.2.1第一示例

80.7.2.2第二示例

81.1.介绍

82.在典型的cmos图像传感器中,如图1所示,通过使用作为光电转换元件的光电二极管pd、浮动扩散区域(浮动扩散部)fd和放大晶体管amp来构造单位像素11,该浮动扩散区域fd将在光电二极管pd中产生的电子转换为电压,该放大晶体管amp使用浮动扩散部fd的电压作为栅极输入。浮动扩散区域(浮动扩散部)fd也称为电荷累积单元。

83.通过由放大晶体管amp构成的源极跟随器电路(以下称为源极跟随器读出构造)从每个单位像素11读出模拟输出电压(像素信号),并且将模拟输出电压转换(模数(ad:analog to digital)转换)为数字电压值。

84.另一方面,作为从单位像素11读出像素信号的构造,除了源极跟随器读出构造之外,还存在其中差分型放大电路(以下简称为差分放大电路)由两个单位像素11构成以通过差分放大电路读出像素信号的构造(以下称为差分型放大读出构造)。

85.在光电二极管pd中产生的电子以与构成浮动扩散部fd的节点的寄生电容对应的每个电子的电压转换效率(μv/e

‑

)被转换为电压。通过放大晶体管amp从每个单位像素11读出与信号电子的数量对应的浮动扩散部fd的电压幅度δvfd。此时,噪声被叠加在读出的像素信号上。

86.噪声的主要产生源的示例包括由单位像素11中的放大晶体管amp产生的像素噪声

vn_pix(μv(微伏)rms)、由模拟电路(模拟前端,afe)产生的afe噪声vn_afe(μvrms)以及由ad转换电路(adc)产生的adc噪声vn_adc(μvrms),该模拟电路例如是对通过垂直信号线vsl从每个单位像素11读出的电压进行放大的电路。

87.在下面的描述中,如图2所示,将输入转换为在浮动扩散部fd中产生的电压噪声的噪声定义为像素噪声vn_pix,将转换为在垂直信号线vsl中产生的电压噪声的噪声定义为afe噪声vn_afe,并且将转换为在adc 20的输入节点处产生的噪声的噪声定义为adc噪声vn_adc。

88.在源极跟随器读出构造中,垂直信号线vsl的电压幅度δvvsl相对于浮动扩散部fd的电压幅度δvfd的增益asf通过δvvsl=asf

×

δvfd获得,并且其值约为0.8至1.0倍。在假设浮动扩散部fd中的电子

‑

电压转换的转换效率(μv/e

‑

)为ηfd的情况下,也就是说,在假设垂直信号线vsl中的电子

‑

电压转换的转换效率(μv/e

‑

)为ηvsl的情况下,满足ηvsl=asf

×

ηfd。

89.在这种情况下,假设从光电二极管pd读出的信号的电子数(也称为信号电子数)为nsig_e,则可以建立δvvsl=ηvsl

×

nsig_e=ηfd

×

asf

×

nsig_e。为了简单起见,假设电压未被afe放大,也就是说,增益为1倍,则当将叠加在adc 20的输出上的噪声转换为在垂直信号线vsl中产生的电压噪声作为vn_total(μvrms)时,总噪声vn_total是adc噪声vn_adc、afe噪声vn_afe和噪声afd

×

vn_pix的总和(平方算术平均值)。这表示总噪声vn_total叠加在基于信号电子数nsig_e的垂直信号线vsl的电压幅度δvvsl上。afd是浮动扩散部fd的增益。

90.从图像质量的角度来看,重要的是,在一定的信号电子数nsig_e上叠加多少噪声量。当将总噪声vn_total转换为浮动扩散部fd中的电子数(单位:e

‑

rms)时,总噪声vn_total的电子数vn_total_e由下面的表达式(1)表示。

91.[数学式1]

[0092][0093]

在表达式(1)中,建立了ηvsl=asf

×

ηfd,因此可以发现,能够通过增大增益asf来降低adc噪声vn_adc和afe噪声vn_afe的影响,并且能够通过提高转换效率ηfd来降低adc噪声vn_adc、afe噪声vn_afe和像素噪声vn_pix的影响。

[0094]

如上所述,增益asf是源极跟随器电路的电压增益,其通常为0.8至1.0,并且理论上为1.0以下。因此,难以提高增益asf。另一方面,转换效率ηfd是基于从浮动扩散部fd观察的寄生电容的总计cfd而确定的,并且建立了ηfd=e/cfd。e表示电子的量子,并且为1.602

×

10

‑

19

库仑的常数。

[0095]

为了降低噪声的电容减小是存在物理限制的。如图3a至图3b所示,在采用在多个单位像素11之间共用晶体管(例如,复位晶体管rst或放大晶体管amp)的结构以减小单位像素11的间距(以下称为像素间距)的情况下,随着从共用像素的多个传输晶体管trg到放大晶体管amp的布线的延伸,浮动扩散部fd的寄生电容cfd增大,并且提高转换效率ηfd变得更加困难。

[0096]

如上所述,在源极跟随器读出构造中,增益asf约为1倍,因此,当由于单位像素11被微细化而不能提高转换效率ηfd时,存在以下问题:不能将转换效率ηvsl设计得很大,并且不能降低噪声。

[0097]

另一方面,在差分型放大读出构造中,基于作为浮动扩散部fd的寄生电容cfd的一部分的相对于垂直信号线vsl的寄生电容cgd来确定垂直信号线vsl的电压幅度δvvsl的增益adif。寄生电容cgd不仅可以包括放大晶体管amp的寄生电容,还可以包括通过布线电容等有意添加的电容以调节增益adif。

[0098]

在假设差分型放大读出构造中的差分放大电路的开环增益为

‑

av的情况下,建立了ηvsl=e/{cgd+cfd/

‑

av}。类似地,当将差分型放大读出构造中的总噪声转换为浮动扩散部fd中的电子数时,总噪声vn_total的电子数vn_total_e由下面的表达式(2)表示。

[0099]

[数学式2]

[0100][0101]

从表达式(2)可以清楚地看出,在差分型放大读出构造中,也可以通过提高转换效率ηvsl和ηfd来降低噪声。

[0102]

基于源极跟随器读出构造的表达式(1)和差分型放大读出构造的表达式(2)之间的比较,关于adc噪声vn_adc和afe噪声vn_afe,表达式(1)中的转换效率ηvsl为asf

×

ηfd,并且增益asf最大为1.0,从而建立了ηvsl≤ηfd=e/cfd。因此,在难以减小寄生电容cfd的情况下,不能提高转换效率ηvsl。

[0103]

另一方面,关于表达式(2)的转换效率ηvsl,建立了e/{cgd+cfd/av},并且开环增益

‑

av通常约为几十到几百,从而可以抑制寄生电容cfd的影响,因此建立了ηvsl≈e/cgd。寄生电容cgd是寄生电容cfd的一部分,从而寄生电容cgd是比寄生电容cfd更小的值。另外,如图4所示,寄生电容cgd是寄生在放大晶体管amp中的电容,从而即使在采用单位像素11共用放大晶体管amp的结构的情况下,也不能防止该电容减小。也就是说,在差分型放大读出构造中,转换效率ηvsl可以为更大的值。这表明,从噪声降低的角度来看,差分型放大读出构造比源极跟随器读出构造有优势。

[0104]

然而,差分型放大读出构造与源极跟随器读出构造相比,像素中放大晶体管的输出阻抗更大,从而垂直信号线vsl的稳定(也称为建立)周期延长。

[0105]

图5a示出了源极跟随器读出构造的示例,图5b示出了差分型放大读出构造的示例,并且将使用这些附图来描述这两种读出构造的输出阻抗。在图5a所示的源极跟随器读出构造中,单位像素11中的放大晶体管amp的输出阻抗由下面的表达式(3)表示。

[0106]

[数学式3]

[0107][0108]

另一方面,在图5b所示的差分型放大读出构造中,放大晶体管amp用作源极接地型放大器,从而其输出阻抗由下面的表达式(4)表示。在表达式(4)中,“//”表示并联电阻。

[0109]

[数学式4]

[0110][0111]

在表达式(3)和表达式(4)中,gm表示通过将漏极电流r

out

的变化除以栅极

‑

源极间电压的变化而获得的值,gds表示放大晶体管amp的漏极电导,c

gd

表示放大晶体管amp的栅极

和漏极之间的反馈电容,并且c

fd

表示与放大晶体管amp的栅极连接的节点的寄生电容(对应于浮动扩散部fd)。在图5a和图5b中,r

vsl

表示垂直信号线vsl的布线电阻,并且c

vsl

表示垂直信号线vsl的寄生电容。

[0112]

从表达式(3)和表达式(4)可以清楚地看出,差分型放大读出构造的输出阻抗是源极跟随器读出构造的输出阻抗的几倍。在这种情况下,垂直信号线vsl的稳定周期是基于垂直信号线vsl的rc时间常数而确定的。因此,与源极跟随器读出构造的情况相比,在差分型放大读出构造中,稳定时间被延迟。结果,在差分型放大读出构造中,存在以下问题:在使要读出的单位像素(以下称为读出像素或信号像素)的行(以下称为读出像素行或信号像素行)过渡到下一个读出像素行时,或者紧接在将电荷从每个单位像素11中的光电二极管pd传输到浮动扩散部fd时之后,产生比通常情况更长的垂直信号线vsl的稳定周期,并且读出时间延长,因此帧速率降低。

[0113]

在使读出像素行过渡到下一个读出像素行(例如,从第i行到第(i+1)行)时,使所有单位像素11的选择晶体管sel处于截止状态,并且消除构成差分型放大读出构造的差分对的电流路径,从而失去流出目的地的电流保留在垂直信号线vsl中,因此垂直信号线vsl的稳定周期延长。

[0114]

在将电荷从每个单位像素11中的光电二极管pd传输到浮动扩散部fd时,作为差分对的反相输入(也称为

‑

输入)的浮动扩散部fd增强,并且差分对的电流平衡崩溃,从而垂直信号线vsl的稳定周期延长。

[0115]

因此,以下实施方式使用示例描述了固态摄像装置和电子设备,即使在采用差分型放大读出构造来抑制图像质量劣化的情况下,该固态摄像装置和电子设备也可以抑制由于垂直信号线vsl的延长的稳定周期而导致的帧速率的降低。

[0116]

2.第一实施例

[0117]

接下来,下面将参考附图详细地描述根据本发明的第一实施例的固态摄像装置和电子设备。

[0118]

2.1cmos图像传感器的系统构造示例

[0119]

图6是示出了根据本实施例的作为安装在电子设备上的固态摄像装置的cmos图像传感器的示意性构造示例的系统构造图。如图6所示,cmos图像传感器1包括像素阵列单元10、垂直驱动单元13、列读出电路单元14、列信号处理单元15、水平驱动单元16、系统控制单元12和信号处理单元17。像素阵列单元10、垂直驱动单元13、列读出电路单元14、列信号处理单元15、水平驱动单元16、系统控制单元12和信号处理单元17被设置在同一半导体基板(芯片)上或彼此电连接的多个层叠的半导体基板(芯片)上。

[0120]

像素阵列单元10包括有效像素区域10v,在有效像素区域10v中,有效单位像素(以下称为单位像素)11以矩阵状二维布置,单位像素11包括光电转换元件(光电二极管pd),该光电转换元件可以对与入射光量对应的电荷量进行光电转换以在该光电转换元件中累积并且作为信号输出。像素阵列单元10可以包括如下的区域:其中,除了单位像素11之外,遮光单位像素等也以行和/或列的形状被布置,在遮光单位像素中,通过对光接收表面进行遮光来遮蔽从外部入射的光。例如,除了对光接收表面进行遮光的结构,遮光单位像素可以具有与有效单位像素11相同的构造。

[0121]

在下面的描述中,可以将具有与入射光量对应的电荷量的光电荷简称为“电荷”,

并且可以将单位像素11简称为“像素”。

[0122]

另外,除了有效像素区域11v之外,像素阵列单元10还包括例如如下的伪差分对形成区域10d:其中,具有与单位像素11相同的构造但没有光电二极管pd和传输晶体管trg的单元(以下称为伪单元或单位单元)11d以行和/或列的形状被布置。

[0123]

在像素阵列单元10中,针对矩阵状的像素阵列(包括伪单元11d)的各行沿着附图的水平方向(像素行中的像素的布置方向)形成像素驱动线ld,并且针对各列沿着附图的垂直方向(像素列中的像素的布置方向)形成垂直像素布线lv。像素驱动线ld的一端连接到垂直驱动单元13的与各行对应的输出端。

[0124]

列读出电路单元14至少包括:针对各列将恒定电流供应给像素阵列单元10内的所选行中的单位像素11或伪单元11d的电路;电流镜像电路;以及用于要读出的单位像素11和伪单元11d的切换开关等,列读出电路单元14与像素阵列单元10中的单位像素11和/或伪单元11d的晶体管一起构成差分放大电路(差分对),并且将光电荷信号转换为电压信号(也称为像素信号)以输出到垂直像素布线lv。

[0125]

例如,垂直驱动单元13包括移位寄存器和地址解码器等,并且同时或以行为单位驱动像素阵列单元10中的单位像素11和伪单元11d。未示出垂直驱动单元13的具体构造,但是垂直驱动单元13具有包括读出扫描系统和清除扫描系统或批量清除和批量传输系统的构造。

[0126]

读出扫描系统以行为单位选择性地扫描像素阵列单元10的单位像素11,以从单位像素11读出像素信号。在行驱动(卷帘式快门操作)的情况下,关于扫描,在对应于快门速度时间的读出扫描之前,对由读出扫描系统执行读出扫描的读出行执行清除扫描。在全局曝光(全局快门操作)的情况下,在对应于快门速度时间的批量传输之前执行批量清除。由于这种清除,从读出行中的单位像素11的光电二极管pd中清除(复位)了不必要的电荷。由于清除(复位)了不必要的电荷,因此能执行所谓的电子快门操作。

[0127]

在这种情况下,电子快门操作是指排出不必要的光电荷并重新开始曝光(开始光电荷的累积)的操作,所述不必要的光电荷是紧接在该操作之前在光电二极管pd中累积的。

[0128]

通过由读出扫描系统执行的读出操作读出的信号对应于在先前的读出操作或电子快门操作之后入射的光量。在行驱动的情况下,从先前的读出操作的读出时序或电子快门操作的扫描时序到当前的读出操作的读出时序的周期为单位像素11中的光电荷的累积时间(曝光时间)。在全局曝光的情况下,从批量清除到批量传输的时间为累积时间(曝光时间)。

[0129]

从垂直驱动单元13选择性地扫描的像素行中的每个单位像素11输出的像素信号通过每条垂直像素布线lv被供应给列信号处理单元15。针对像素阵列单元10的每个像素列,列信号处理单元15对经由垂直像素布线lv从所选行中的每个单位像素11输出的像素信号执行预定的信号处理,并且在信号处理之后暂时保持像素信号。

[0130]

具体地,列信号处理单元15至少执行作为信号处理的噪声消除处理,例如,相关双采样(cds:correlated double sampling)处理。通过由列信号处理单元15执行的cds,消除了诸如复位噪声和放大晶体管amp的阈值变化等的像素特有的固定模式噪声。例如,列信号处理单元15还可以被构造为除了噪声清除处理之外还具有ad转换功能,并且将像素信号作为数字信号输出。

[0131]

水平驱动单元16包括移位寄存器和地址解码器等,并且依次选择列信号处理单元15的对应于像素列的单位电路。通过由水平驱动单元16执行的选择性扫描,将由列信号处理单元15执行了信号处理的像素信号依次输出到信号处理单元17。

[0132]

系统控制单元12包括产生各种时序信号的时序发生器等,并且基于由时序发生器产生的各种时序信号对垂直驱动单元13、列信号处理单元15和水平驱动单元16等执行驱动控制。

[0133]

cmos图像传感器1还包括信号处理单元17和数据存储单元(未示出)。信号处理单元17至少具有加法处理功能,并且对从列信号处理单元15输出的像素信号执行诸如加法处理等各种信号处理。在由信号处理单元17执行的信号处理中,数据存储单元暂时存储处理所需的数据。信号处理单元17和数据存储单元可以是设置在与cmos图像传感器1的基板不同的基板上的外部信号处理单元,例如,可以由数字信号处理器(dsp:digital signal processor)或软件执行处理,或者信号处理单元17和数据存储单元可以安装在与cmos图像传感器1的基板相同的基板上。

[0134]

2.2单位像素的电路构造示例

[0135]

接下来,下面将描述以矩阵状设置在图6的像素阵列单元10的有效像素区域10v中的单位像素11的电路构造示例。

[0136]

图7是示出了根据本实施例的有效像素区域中的单位像素的示意性构造示例的电路图。如图7所示,单位像素11由光电二极管pd、传输晶体管trg、浮动扩散部fd、复位晶体管rst、放大晶体管amp、选择晶体管sel、用作像素驱动线ld的选择晶体管驱动线lsel、复位晶体管驱动线lrst、传输晶体管驱动线ltrg、用作垂直像素布线lv的垂直信号线vsl、垂直复位输入线vrd和垂直电流供应线vcom构成,像素驱动线ld的一端连接到垂直驱动单元13,垂直像素布线lv的一端连接到列读出电路单元14。

[0137]

光电二极管pd对入射光进行光电转换。传输晶体管trg传输在光电二极管pd中产生的电荷。浮动扩散部fd累积由传输晶体管trg传输的电荷。放大晶体管amp使具有与在浮动扩散部fd中累积的电荷对应的电压的像素信号出现在垂直信号线vsl中。复位晶体管rst排出在浮动扩散部fd中累积的电荷。选择晶体管sel选择要读出的单位像素11。

[0138]

光电二极管pd的阳极接地,并且其阴极连接到传输晶体管trg的源极。传输晶体管trg的漏极连接到放大晶体管amp的栅极,并且其连接点构成浮动扩散部fd。复位晶体管rst被设置在浮动扩散部fd和垂直复位输入线vrd之间。

[0139]

复位晶体管rst的漏极连接到垂直复位输入线vrd,并且放大晶体管amp的源极连接到垂直电流供应线vcom。放大晶体管amp的漏极连接到选择晶体管sel的源极,并且选择晶体管sel的漏极连接到垂直信号线vsl。

[0140]

传输晶体管trg的栅极、复位晶体管rst的栅极和选择晶体管sel的栅极中的各者经由像素驱动线lv连接到垂直驱动单元13,并且将作为驱动信号的脉冲trgsig、rstsig和selsig分别供应给上述栅极。

[0141]

2.3伪单元的电路构造示例

[0142]

接下来,下面将描述以行和/或列的形状设置在图6的像素阵列单元10的伪差分对形成区域10d中的伪单元11d的电路构造示例。

[0143]

图8是示出了根据本实施例的伪差分对形成区域中的伪单元的示意性构造示例的

电路图。如图8所示,伪单元11d由复位晶体管rstd、放大晶体管ampd、选择晶体管seld、用作像素驱动线ld的选择晶体管驱动线lsel、复位晶体管驱动线lrst、用作垂直像素布线lv的垂直信号线vsl、垂直复位输入线vrd和垂直电流供应线vcom构成,像素驱动线ld的一端连接到垂直驱动单元13,垂直像素布线lv的一端连接到列读出电路单元14。

[0144]

复位晶体管rstd的漏极连接到垂直复位输入线vrd,并且放大晶体管ampd的源极连接到垂直电流供应线vcom。复位晶体管rstd的源极连接到放大晶体管ampd的栅极。放大晶体管ampd的漏极连接到选择晶体管seld的源极,并且选择晶体管seld的漏极连接到垂直信号线vsl。

[0145]

复位晶体管rstd的栅极和选择晶体管seld的栅极中的各者经由像素驱动线ld连接到垂直驱动单元13,并且将作为驱动信号的脉冲rstdsig和seldsig分别供应给上述栅极。

[0146]

例如,每个晶体管的尺寸可以等于有效像素区域11v中的单位像素11的尺寸。在伪差分对形成区域10d中,针对每条垂直信号线vsl至少设置有一对伪单元11d,这一对伪单元11d包括对应于读出像素(信号像素)的伪单元11d和对应于参考像素的伪单元11d。

[0147]

2.4单位像素的基本功能示例

[0148]

接下来,下面将描述单位像素11的基本功能。复位晶体管rst根据从垂直驱动单元13供应的复位信号rstsig开启/关闭在浮动扩散部fd中累积的电荷的排出。当将高电平的复位信号rstsig输入到复位晶体管rst的栅极时,浮动扩散部fd被钳位到通过垂直复位输入线vrd施加的电压。由此,将在浮动扩散部fd中累积的电荷排出(复位)。当将低电平的复位信号rstsig输入到复位晶体管rst的栅极时,浮动扩散部fd与垂直复位输入线vrd断开电连接,并且使浮动扩散部fd处于悬空状态(floating state)。

[0149]

光电二极管pd对入射光进行光电转换,并且产生对应于光量的电荷。产生的电荷累积在光电二极管pd的阴极侧。传输晶体管trg根据从垂直驱动单元13供应的传输控制信号trgsig开启/关闭电荷从光电二极管pd到浮动扩散部fd的传输。例如,当将高电平的传输控制信号trgsig输入到传输晶体管trg的栅极时,将在光电二极管pd中累积的电荷传输到浮动扩散部fd。另一方面,当将低电平的传输控制信号trgsig供应给传输晶体管trg的栅极时,停止从光电二极管pd的电荷传输。在传输晶体管trg停止将电荷传输到浮动扩散部fd的时段期间,将光电转换后的电荷累积在光电二极管pd中。

[0150]

浮动扩散部fd具有累积从光电二极管pd经由传输晶体管trg传输的电荷并将该电荷转换为电压的功能。因此,在复位晶体管rst截止的悬空状态下,根据在浮动扩散部fd中累积的电荷量来调制每个浮动扩散部fd的电位。

[0151]

放大晶体管amp起到放大器的作用,该放大器使用与其栅极连接的浮动扩散部fd的电位变化作为输入信号,并且放大晶体管amp的输出电压信号作为像素信号经由选择晶体管sel被输出到垂直信号线vsl。

[0152]

选择晶体管sel根据从垂直驱动单元13供应的选择控制信号selsig开启/关闭从放大晶体管amp到垂直信号线vsl的电压信号的输出。例如,当将高电平的选择控制信号selsig输入到选择晶体管sel的栅极时,将来自放大晶体管amp的电压信号输出到垂直信号线vsl,并且当将低电平的选择控制信号selsig输入到选择晶体管sel的栅极时,停止向垂直信号线vsl输出电压信号。由此,在与多个像素连接的垂直信号线vsl中,可以仅提取所选

单位像素11的输出。

[0153]

以这种方式,根据从垂直驱动单元13供应的传输控制信号trgsig、复位信号rstsig和选择控制信号selsig来驱动单位像素11。

[0154]

2.5差分型放大读出构造的示例

[0155]

接下来,下面将描述包括列读出电路单元14和以矩阵状二维布置在像素阵列单元10中的单位像素11的差分型放大读出构造。

[0156]

图9是示出了根据本实施例的差分型放大读出构造的示意性构造示例的电路图。图9所示的差分型放大读出构造由单位像素(以下称为信号像素)11a、单位像素(以下称为参考像素)11b、电流镜像电路141和尾电流源单元142构成,从单位像素11a读出像素信号,单位像素11b给出用于差分放大的参考电压,电流镜像电路141包括设置在列读出电路单元14中的pmos晶体管mp0和mp1,尾电流源单元142将恒定电流供应给信号像素11a和参考像素11b。在这种情况下,参考像素11b优选为如下的单位像素11:其中,复位时浮动扩散部fd0中的电位变化与信号像素11a的浮动扩散部fd1中的电位变化相等地移动,并且参考像素11b例如可以是在要读出的信号像素(也称为读出像素)11a附近的已经读出的非活性有效像素。

[0157]

参考像素11b侧的垂直复位输入线vrd0连接到列读出电路单元14中的预定电源vrst,并且在复位时,将期望的输入电压信号施加给经由垂直复位输入线vrd0选择的参考像素11b的浮动扩散部fd0,即参考像素11b侧的放大晶体管amp0的输入端子。

[0158]

参考像素11b侧的垂直信号线vsl0连接到列读出电路单元14中的电流镜像电路141的参考侧pmos晶体管mp0的漏极和栅极以及读出侧pmos晶体管mp1的栅极。

[0159]

另一方面,读出侧垂直信号线vsl1连接到列读出电路单元14中的电流镜像电路141的读出侧pmos晶体管mp1的漏极,并且经由复位晶体管rst1连接到所选信号像素11a的浮动扩散部fd,即读出侧放大晶体管amp1的输入端子。由此,差分型放大读出构造的输出信号被负反馈。从垂直信号线vsl1提取差分型放大读出构造的输出信号作为像素信号。

[0160]

例如,参考侧和读出侧的垂直电流供应线ccom彼此连接,其后连接到作为恒流源的尾电流源单元142,该恒流源由诸如nmos晶体管等负载mos晶体管构成。

[0161]

2.6差分型放大读出构造的外围电路的示例

[0162]

随后,下面将描述包括外围电路的差分型放大读出构造的构造。图10是示出了根据本实施例的差分型放大读出构造及其外围电路的示意性构造示例的电路图。图10中的差分型放大读出构造类似于图9中例示的差分型放大读出构造。然而,在图10中,以示例的方式,假设图9中的参考像素11b是有效像素区域10v中的单位像素11

i

,并且类似地,假设信号像素11a是有效像素区域10v中的单位像素11

i+1

。

[0163]

如图10所示,作为形成差分型放大读出构造的信号像素11a和参考像素11b,例如,使用的是在列方向上布置的单位像素11之中的两个单位像素11

i+1

和11

i

。也就是说,作为差分型放大读出构造的差分放大电路由用作恒流电路的尾电流源单元142、电流镜像电路141以及相应的两个单位像素11的放大晶体管amp

i

和amp

i+1

构成。

[0164]

单位像素11

i

的复位晶体管rst

i

的源极连接到垂直复位输入线vrd0

k

。另一方面,单位像素11

i+1

的复位晶体管rst

i+1

的源极连接到垂直复位输入线vrd1

k

。

[0165]

单位像素11

i

的选择晶体管sel

i

的源极连接到垂直信号线vsl0

k

。另一方面,单位像

素11

i+1

的选择晶体管sel

i+1

的源极连接到垂直信号线vsl1

k

。

[0166]

另外,单位像素11

i

的放大晶体管amp

i

的源极和单位像素11

i+1

的放大晶体管amp

i+1

的源极都连接到垂直电流供应线vcom

k

。

[0167]

垂直复位输入线vrd0

k

经由开关sw4连接到预定电源vrst,在差分型放大读出时,将高电平的控制信号cntl0输入到开关sw4。类似地,垂直复位输入线vrd1

k

经由开关sw5连接到预定电源vrst,在差分型放大读出时,将高电平的控制信号cntl1输入到开关sw5。

[0168]

垂直信号线vsl0

k

的一端连接到电流镜像电路141。类似地,垂直信号线vsl1

k

的一端连接到电流镜像电路141。

[0169]

垂直电流供应线vcom

k

的一端连接到与电源电压vdd连接的尾电流源单元142。

[0170]

垂直复位输入线vrd0

k

和垂直信号线vsl0

k

经由开关sw0彼此连接,将用于控制在列方向上的信号像素的切换的控制信号cntl0输入到开关sw0。类似地,垂直复位输入线vrd1

k

和垂直信号线vsl1

k

经由开关sw1彼此连接,将用于控制在列方向上的信号像素的切换的控制信号cntl1输入到开关sw1。

[0171]

另外,电流镜像电路141的设置在垂直信号线vsl0

k

中的pmos晶体管mp0的漏极经由开关sw2连接到pmos晶体管mp0和mp1的栅极,将用于控制在列方向上的信号像素的切换的控制信号cntl0输入到开关sw2。类似地,电流镜像电路141的设置在垂直信号线vsl1

k

中的pmos晶体管mp1的漏极经由开关sw3连接到pmos晶体管mp0和mp1的栅极,将用于控制在列方向上的信号像素的切换的控制信号cntl1输入到开关sw3。

[0172]

在如上所述的构造中,可以通过切换每个开关sw的接通/断开来彼此切换构成差分型放大读出中的差分对的信号像素11a和参考像素11b。

[0173]

信号像素11a和参考像素11b的组合不限于有效像素区域10v中的在列方向上彼此相邻的两个单位像素11

i+1

和11

i

。然而,如图10所示,例如,在奇数行中的单位像素11

i

的选择晶体管sel

i

连接到垂直信号线vsl0

k

,同一单位像素11

i

的复位晶体管rst

i

连接到垂直复位输入线vrd0

k

,偶数行中的单位像素11

i+1

的选择晶体管sel

i+1

连接到垂直信号线vsl1

k

,并且同一单位像素11

i+1

的复位晶体管rst

i+1

连接到垂直复位输入线vrd1

k

的情况下,相邻的两个单位像素11

i

和11

i+1

可以彼此组合作为信号像素11a和参考像素11b。

[0174]

在具有这种连接关系的情况下,通过适当地切换开关sw0至sw5,有效像素区域10v中的每个单位像素11可以作为信号像素11a和参考像素11b中的任一者进行操作。因此,在本实施例中,以如下方式执行操作:在改变信号像素11a和参考像素11b的组合的同时,依次切换开关sw0至sw5以扫描地址,并且从二维布置的所有单位像素11依次读出像素信号。例如,在使开关sw0、sw2和sw4处于断开状态并且使开关sw1、sw3和sw5处于接通状态的情况下,可以使奇数行(例如,第i行)成为参考像素行,并且可以使偶数行(例如,第(i+1)行)成为信号像素行。类似地,在使开关sw0、sw2和sw4处于接通状态并且使开关sw1、sw3和sw5处于断开状态的情况下,可以使奇数行(例如,第i行)成为信号像素行,并且可以使偶数行(例如,第(i+1)行)成为参考像素行。

[0175]

然而,实施例不限于此。只要各个单位像素11的选择晶体管sel连接到不同的垂直信号线vsl,并且其复位晶体管rst连接到不同的垂直复位输入线vrd,就可以对两个单位像素11的组合进行各种变形。

[0176]

例如,根据本实施例的伪差分对形成区域10d可以在像素阵列单元10中的与有效

像素区域10v相邻的区域中布置在垂直复位输入线vrd和垂直信号线vsl的一端侧或两端侧。在这种情况下,针对有效像素区域10v中的单位像素11的各列布置有一对伪单元11d。

[0177]

在图10中,伪单元11d0例如是对应于单位像素11

i

的伪单元11d,其选择晶体管seld0的漏极连接到垂直信号线vsl0

k

,并且复位晶体管rst0的漏极连接到垂直复位输入线vrd0

k

。另一方面,伪单元11d1例如是对应于单位像素11

i+1

的伪单元11d,其选择晶体管seld1的漏极连接到垂直信号线vsl1

k

,并且复位晶体管rst1的漏极连接到垂直复位输入线vrd1

k

。

[0178]

当在非选择状态下使有效像素区域10v中的所有单位像素11处于导通状态时,一对伪单元11d0和11d1的选择晶体管seld0和seld1以及复位晶体管rstd0和rstd1构成差分放大电路(差分对)。在这样构造的差分放大电路中,反相输入(放大晶体管ampd1的栅极)和输出(放大晶体管ampd1的漏极)经由选择晶体管seld1、垂直信号线vsl1

k

、开关sw1和复位晶体管rstd1被短路。由此,在使信号像素行过渡到下一个信号像素行时(例如,从第i行到第(i+1)行),可以防止使所有单位像素11的选择晶体管sel处于截止状态的情况,并且消除了用于构成差分型放大读出构造的差分对的电流路径。结果,可以保持电流消耗,从而可以防止垂直信号线vsl的稳定周期延长。

[0179]

在电荷从光电二极管pd传输到浮动扩散部fd的时段内,使一对伪单元11d0和11d1的选择晶体管seld0和seld1以及复位晶体管rstd0和rstd1也处于导通状态,并且类似地,构成反相输入(

‑

输入)和输出被短路的差分放大电路(差分对)。由此,在每个单位像素11中将电荷从光电二极管pd传输到浮动扩散部fd时,可以防止作为差分对的反相输入(也称为

‑

输入)的浮动扩散部fd增强且差分对的电流平衡崩溃的情况,结果,可以防止垂直信号线vsl的稳定周期延长。

[0180]

在本实施例中,伪单元11d0和11d1的复位晶体管rstd不是必不可少的构造,并且可以省略。在这种情况下,放大晶体管ampd的栅极连接到垂直复位输入线vrd。例如,在图10例示的构造中,伪单元11d0中的放大晶体管ampd0的栅极连接到垂直复位输入线vrd0

k

,并且伪单元11d1中的放大晶体管ampd1的栅极连接到垂直复位输入线vrd1

k

。

[0181]

2.7形成差分型放大读出构造的单位像素的组合示例

[0182]

接下来,下面将描述形成根据本实施例的差分型放大读出构造的单位像素11的组合。图11是用于说明根据本实施例的组合示例的示意图。在图11中,如上面参考图10所述,例如,假设奇数行中的单位像素11

i

的选择晶体管sel

i

连接到垂直信号线vsl0

k

,并且假设偶数行中的单位像素11

i+1

的选择晶体管sel

i+1

连接到垂直信号线vsl1

k

。

[0183]

如图11所示,在列方向上布置的单位像素11交替地连接到不同的垂直信号线vsl的情况下,选择在列方向上布置的单位像素11之中的彼此相邻的两个单位像素11作为信号像素11a和参考像素11b。例如,在读出第i行时,选择单位像素11

i

作为信号像素11a,并且选择单位像素11

i

‑1作为参考像素11b。

[0184]

随后,在读出第(i+1)行时,选择单位像素11

i+1

作为信号像素11a,并且选择单位像素11

i

作为参考像素11b。其后,被选为参考像素11b的单位像素11的行(以下称为参考行)随着被选为信号像素11a的单位像素11的行(以下称为读出行)的切换而被切换。在图11所示的示例中,例如,选择与信号像素11a相邻的已读出的单位像素11作为参考像素11b,并且参考行在读出行的过渡之后进行过渡。

[0185]

然而,参考行不限于紧接在读出行之前的作为读出行的行,而是可以是接下来要

被选为读出行的行。

[0186]

2.8差分型放大读出构造的驱动示例

[0187]

接下来,下面将描述差分型放大读出构造的驱动示例。为了清楚起见,基于图9所示的差分型放大读出构造进行下面的描述。图12是示出了根据本实施例的差分型放大读出构造的驱动示例的时序图。

[0188]

如图12所示,在根据本实施例的差分型放大读出中,首先,在从时刻t1到时刻t2的时段内,当输入到信号像素11a的复位信号rstsig1和传输控制信号trgsig1上升到高电平时,经由复位晶体管rst1排出在信号像素11a的光电二极管pd1和浮动扩散部fd1中累积的电荷。由此,清除了在光电二极管pd1中累积的电荷,并且在从时刻t2到时刻t5的时段内,将通过对入射光进行光电转换而重新获得的电荷累积在光电二极管pd1中。

[0189]

接下来,在从时刻t3到时刻t7的时段内,当所选信号像素11a和所选参考像素11b的选择控制信号selsig1和selsig0从低电平上升到高电平时,在从信号像素11a的放大晶体管amp1和参考像素11b的放大晶体管amp0的各自源极到各自漏极的方向上,从尾电流源单元142供应电流。由此,使用信号像素11a的浮动扩散部fd1的电位作为输入电压信号的差分放大电路(差分型放大读出构造)进行操作,结果,将放大后的电压信号输出到垂直信号线vsl。该状态持续到在时刻t7选择控制信号selsig1和selsig0变为低电平为止。

[0190]

在从时刻t1到时刻t3的时段内,参考像素11b的驱动信号selsig0、rstsig0和trgsig0中的各者都未对信号像素11a的信号读出做出贡献。

[0191]

在从时刻t3到时刻t4的时段内,当输入到信号像素11a的复位信号rstsig1和输入到参考像素11b的复位信号rstsig0上升到高电平时,排出在信号像素11a和参考像素11b的浮动扩散部fd1和浮动扩散部fd0中累积的电荷,因此,输出信号电平被初始化(复位)。

[0192]

此时,差分放大电路的输出vout经由信号像素11a侧的垂直复位输入线vrd1和复位晶体管rst1电连接到信号像素11a的作为差分放大电路的一个输入的浮动扩散部fd1。结果,差分放大电路的输出vout被负反馈到信号像素11a的浮动扩散部fd1以处于虚拟接地状态,从而从外部施加以固定到预定电源vrst的参考像素11b的浮动扩散部fd0、信号像素11a的浮动扩散部fd1和输出vout具有相同的电位(电压跟随器电路的构造)。

[0193]

接下来,当输入到信号像素11a的复位信号rstsig1和输入到参考像素11b的复位信号rstsig0从高电平下降到低电平时,信号像素11a和参考像素11b的浮动扩散部fd1和浮动扩散部fd0与各自的垂直复位输入线vrd1和vrd0断开电连接以处于悬空状态。

[0194]

此时,信号像素11a的浮动扩散部fd1和参考像素11b的浮动扩散部fd0的结构基本上彼此等同,从而复位关闭(复位馈通)时的电位变化基本相同,并且信号像素11a的浮动扩散部fd1的电位和参考像素11b的浮动扩散部fd0的电位以基本相同的方式移动。因此,在复位开启时,差分放大电路的输出几乎不会从电源vrst的电压电平改变。该状态是差分型放大读出中的复位(初始)状态,并且该输出电平是差分型放大读出中的复位(初始)电平。这是因为差分放大电路的两个输入的同相信号成分(in

‑

phase signal component)均未被放大。该复位状态持续到在时刻t5传输信号电荷,同时读出电压作为复位电平为止。

[0195]

接下来,在从时刻t5到时刻t6的时段内,当信号像素11a的传输控制信号trgsig1以脉冲形式上升到高电平时,将在信号像素11a的光电二极管pd1中累积的电荷经由传输晶体管trg1传输到浮动扩散部fd1。通过传输的电荷对信号像素11a的浮动扩散部fd1的电位进

行调制。当将调制后的电位作为电压信号输入到信号像素11a的放大晶体管amp1的栅极时,将与累积的电荷量对应的电压信号输出到信号像素11a侧的垂直信号线vsl1。

[0196]

该信号读出状态持续到在时刻t7选择控制信号selsig1变为低电平,同时读出电压作为信号电平为止。

[0197]

通过获取如上所述地读出的复位电平和信号电平之间的差,执行用于消除噪声的cds处理,因此能读出消除了噪声的像素信号。

[0198]

2.9在差分型放大读出时的驱动示例(在读出像素和参考像素之间切换)

[0199]

随后,下面将描述在包括外围电路中的开关sw0至sw5的差分型放大读出时的驱动示例。基于图10所示的差分型放大读出构造进行下面的描述。图10未示出第(i

‑

1)行的构造,但是从第i行和第(i+1)行的构造可以容易地想到该构造,从而将在假设在此示出了第(i

‑

1)行的构造的情况下进行描述。

[0200]

图13是示出了在根据本实施例的包括外围电路中的开关的差分型放大读出时的驱动示例的时序图。在图13所示的驱动示例中,从时序t11到时序t16,使开关sw0、sw2和sw4处于断开状态,使开关sw1、sw3和sw5处于接通状态,使第(i

‑

1)行中的单位像素11

i

‑1成为参考像素11b,并且使第i行中的单位像素11

i

成为信号像素11a。另外,从时序t16到时序t21,使开关sw0、sw2和sw4处于接通状态,使开关sw1、sw3和sw5处于断开状态,使第i行中的单位像素11

i

成为参考像素11b,并且使第(i+1)行中的单位像素11

i+1

成为信号像素11a。

[0201]

如图13所示,在通过使第i行中的单位像素11

i

成为信号像素11a来读出信号电平的时段内(从时序t11到时序t16),使控制信号cntl0处于低电平,使开关sw0、sw2和sw4处于断开状态,使控制信号cntl1处于高电平,并且使开关sw1、sw3和sw5处于接通状态。

[0202]

在该时段内(从时序t11到时序t16),从时序t11到时序t12的时段是垂直驱动单元13使要读出的单位像素11的像素地址过渡到下一个单位像素11的像素地址的时段。因此,在从时序t11到时序t12的时段内,使有效像素区域10v中的所有单位像素11都处于非选择状态。因此,在本实施例中,施加给一对伪单元11d0和11d1的各个选择晶体管seld0和seld1的栅极的选择控制信号seldsig以脉冲形式提高到高电平,并且施加给伪单元11d0和11d1的各个复位晶体管rstd0和rstd1的栅极的复位信号rstdsig0和rstdsig1以脉冲形式提高到高电平。由此,反相输入(

‑

输入)和输出被短路的差分放大电路由一对伪单元11d0和11d1、电流镜像电路141和尾电流源单元142形成,并且形成了用于差分对的电流路径,从而可以保持电流消耗。

[0203]

接下来,在从时序t12到时序t13的时段内,通过以脉冲形式将施加给被选为参考像素11b的单位像素11

i

‑1的复位晶体管rst

i

‑1的栅极的复位信号rstsig

i

‑1以及施加给被选为信号像素11a的单位像素11

i

的复位晶体管rst

i

的栅极的复位信号rstsig

i

提高到高电平,将形成具有负反馈构造的差分对的各个单位像素11

i

‑1和11

i

的浮动扩散fd

i

‑1和浮动扩散fd

i

复位。

[0204]

其后,当复位信号rstsig

i

‑1和rstsig

i

在时序t13下降到低电平时,在从时序t13到时序t14的时段内,列读出电路单元14读出在垂直信号线vsl0

k

中出现的电压电平作为复位电平(p相),并且列信号处理单元15对读出的复位电平进行ad转换。

[0205]

接下来,在从时序t14到时序t15的时段内,通过以脉冲形式将施加给作为信号像素11a的单位像素11

i

的传输晶体管trg

i

的栅极的传输控制信号trgsig

i

提高到高电平,将在

单位像素11

i

的光电二极管pd

i

中产生的电荷传输到浮动扩散部fd

i

。

[0206]

类似地,在从时序t14到时序t15的时段内,使施加给各个单位像素11

i

‑1和11

i

的选择晶体管sel

i

‑1和sel

i

的栅极的选择控制信号selsig

i

‑1和selsig

i

以脉冲形式下降到低电平,并且施加给伪单元11d0和11d1的选择晶体管seld0和seld1的栅极的选择控制信号seldsig以及施加给复位晶体管rstd0和rstd1的栅极的复位信号rstdsig0和rstdsig1以脉冲形式提高到高电平。由此,形成了反相输入(

‑

输入)和输出被短路的差分放大电路,从而可以防止单位像素11

i

的作为差分对的反相输入的浮动扩散部fd

i

增强并且差分对的电流平衡崩溃的情况。

[0207]

其后,当在时序t15使伪单元11d0和11d1的选择控制信号seldsig和复位信号rstdsig0和rstdsig1下降并且单位像素11

i

‑1和11

i

的选择控制信号selsig

i

‑1和selsig

i

上升时,在从时序t15到时序t16的时段期间,列读出电路单元14读出在垂直信号线vsl0

k

中出现的电压电平作为信号电平(d相:像素信号),并且列信号处理单元15对读出的信号电平进行ad转换。

[0208]

在列信号处理单元15或诸如信号处理单元17等外围电路中,从信号电平(d相)的数字值中减去复位电平(p相)的数字值以执行用于获取与光电二极管pd

i

的接收光量对应的信号成分的数字值的cds处理。

[0209]

随后,在通过使第(i+1)行中的单位像素11

i+1

成为信号像素11a来读出信号电平的时段内(从时序t16到时时序t21),使控制信号cntl0处于高电平,使开关sw0、sw2和sw4处于接通状态,使控制信号cntl1处于低电平,并且使开关sw1、sw3和sw5处于断开状态。

[0210]

在该时段内(从时序t16到时序t21),类似于通过使第i行中的单位像素11

i

成为信号像素11a来读出信号电平的时段(从时序t11到时序t16),在使有效像素区域10v中的所有单位像素11都处于非选择状态的从时序t16到时序t17的时段内,通过使伪单元11d0和11d1的选择晶体管seld0和seld1以及复位晶体管rstd0和rstd1处于导通状态,形成了包括一对伪单元11d0和11d1、电流镜像电路141和尾电流源单元142的差分放大电路。

[0211]

在从时序t17到时序t18的时段内,使作为参考像素11b的单位像素11

i

和作为信号像素11a的单位像素11

i+1

的复位晶体管rst

i

和rst

i+1

处于导通状态,以将浮动扩散部fd

i

和浮动扩散部fd

i+1

复位,并且在从时序t18到时序t19的时段内,读出在垂直信号线vsl1

k

中出现的复位电平并且对其进行ad转换。

[0212]

其后,在从时序t19到时序t20的时段内,通过使传输晶体管trg

i+1

处于导通状态,将光电二极管pd

i+1

的电荷传输到浮动扩散部fd

i+1

,并且使伪单元11d0和11d1的选择晶体管seld0和seld1以及复位晶体管rstd0和rstd1处于导通状态来形成反相输入(

‑

输入)和输出被短路的差分放大电路,从而可以防止单位像素11

i+1

的作为差分对的反相输入的浮动扩散部fd

i+1

增强并且差分对的电流平衡崩溃的情况。

[0213]

在从时序t20到时序t21的时段内,读出在垂直信号线vsl1

k

中出现的信号电平并且对其进行ad转换。

[0214]

其后,在列信号处理单元15或诸如信号处理单元17等外围电路中,从信号电平(d相)的数字值中减去复位电平(p相)的数字值以执行用于获取与光电二极管pd的接收光量对应的信号成分的数字值的cds处理。

[0215]

2.10作用和效果

[0216]

如上所述,根据本实施例,在使有效像素区域10v中的所有单位像素11都处于非选择状态的时段(图13中的从时序t11到时序t12和从时序t16到时序t17的时段)期间,反相输入(

‑

输入)和输出被短路的差分放大电路由伪单元11d0和11d1的放大晶体管ampd0和ampd1、电流镜像电路141以及尾电流源单元142形成,并且保持了电流消耗,从而能够保持电源电压vdd和接地电压的下降量。由此,可以防止垂直信号线vsl0

k

和vsl1

k

的稳定时间延长。

[0217]

在将电荷从光电二极管pd传输到浮动扩散部fd的传输时段(图13中的从时序t14到时序t15和从时序t19到时序t20的时段)内,垂直信号线vsl与单位像素11分离,并且垂直信号线vsl的电压电平保持在复位电平,从而可以防止由于传输晶体管trg和浮动扩散部fd的电容耦合引起的馈通而在垂直信号线vsl中产生较大幅度的情况,因此可以防止垂直信号线vsl的稳定时间延长。

[0218]

3.第二实施例

[0219]

接下来,下面将参考附图详细地描述根据第二实施例的固态摄像装置和电子设备。在下面的描述中,将不会通过引用而重复关于与上述实施例中的构造和操作相同的构造和操作的多余描述。

[0220]

在上述的第一实施例中,作为形成差分型放大读出构造的单位像素的组合示例,例示了如下情况:以差分对由有效像素区域10v中的两个单位像素11形成的方式选择用于形成差分对的一对单位像素11,并且参考像素11b跟随信号像素11a的切换(参考图11)。另一方面,第二实施例以示例的方式描述了将参考像素11b固定为特定行(以下称为参考专用行)中的单位像素11的情况。

[0221]

3.1形成差分型放大读出构造的单位像素的组合示例

[0222]

图14是用于说明根据本实施例的组合示例的示意图。如图14所示,在该组合示例中,将参考行固定为特定行(参考专用行)。例如,参考专用行可以是以矩阵状布置的单位像素11的末端行。可替代地,参考专用行可以是像素阵列单元10的除有效像素区域10v中的行以外的行。

[0223]

参考专用行中的参考像素11r连接到垂直信号线vsl0

k

,并且有效像素区域10v中的可以被选为信号像素11a的所有单位像素11都连接到垂直信号线vsl1

k

。

[0224]

类似于参考像素11b,参考像素11r可以具有与常规单位像素11相同的构造。使参考像素11r在读出时段期间始终处于选择状态,也就是说,使选择晶体管trg始终处于导通状态。

[0225]

3.2差分型放大读出构造的外围电路的示例

[0226]

随后,下面将描述包括外围电路的差分型放大读出构造的构造。图15是示出了根据本实施例的差分型放大读出构造及其外围电路的示意性构造示例的电路图。图15中的差分型放大读出构造具有与图14中例示的差分型放大读出构造相同的构造。然而,在图15中,以示例的方式,使图14中的参考像素11r成为有效像素区域10v外部的参考像素区域10r中的单位像素11,并且使信号像素11a成为有效像素区域10v中的单位像素11

i

。

[0227]

例如,在图15所示的构造中,有效像素区域11v中的单位像素11

i

可以具有与第一实施例中参考图10所述的构造相同的构造。然而,在本实施例中,有效像素区域11v中的单位像素11

i

的选择晶体管sel

i

的所有漏极都连接到垂直信号线vsl1

k

,并且复位晶体管rst

i

的所有漏极都连接到垂直复位输入线vrd1

k

。

[0228]

例如,参考像素区域10r中的参考像素11r具有与有效像素区域11v中的单位像素11

i

的构造相同的构造。然而,参考像素11r的选择晶体管sel

r

的漏极连接到垂直信号线vsl0

k

,并且复位晶体管rst

r

的漏极连接到垂直复位输入线vrd0

k

。

[0229]

除了省略了复位晶体管rstd0和rstd1,伪差分对形成区域10d中的一对伪单元11d2和11d3具有与图10所示的一对伪单元11d0和11dl的构造相同的构造。伪单元11d2的放大晶体管ampd0的栅极连接到垂直复位输入线vrd0

k

,并且伪单元11d3的放大晶体管ampd1的栅极连接到垂直复位输入线vrd1

k

。

[0230]

以这种方式,在将参考像素11r固定为特定的参考专用行的单位像素11的构造中,可以省略一对伪单元11d2和11d3的复位晶体管rstd0和rstd1。例如,信号像素11a和参考像素11r不需要彼此切换,从而可以省略图10中例示的开关sw0至sw5。

[0231]

3.3在差分型放大读出时的驱动示例(在读出像素和参考像素之间切换)

[0232]

随后,下面将描述在差分型放大读出时的驱动示例。基于图15所示的差分型放大读出构造进行下面的描述。

[0233]

图16是示出了在根据本实施例的差分型放大读出时的驱动示例的时序图。在图16所示的驱动示例中,从时序t31到时序t36,使第i行中的单位像素11

i

成为信号像素11a,并且从时序t36到时序t41,使第(i+1)行中的单位像素11

i+1

成为信号像素11a。

[0234]

如图16所示,在通过使第i行中的单位像素11

i

成为信号像素11a来读出信号电平的时段内(从时序t31到时序t36),从时序t31到时序t32的时段是垂直驱动单元13使要读出的单位像素11的像素地址过渡到下一个单位像素11的像素地址的时段。因此,在从时序t31到时序t32的时段内,使有效像素区域10v中的所有单位像素11都处于非选择状态。因此,在本实施例中,施加给一对伪单元11d2和11d3的选择晶体管seld0和seld1的栅极的选择控制信号seldsig以脉冲形式提高到高电平。由此,反相输入(

‑

输入)和输出被短路的差分放大电路由一对伪单元11d0和11d1、电流镜像电路141和尾电流源单元142形成,并且形成了用于差分对的电流路径,从而可以防止失去流出目的地的电流累积在垂直信号线vsl中。

[0235]

接下来,在从时序t32到时序t33的时段内,通过将施加给参考像素11r的复位晶体管rst

r

的栅极的复位信号rstsig

r

和施加给被选为信号像素11a的单位像素11

i

的复位晶体管rst

i

的栅极的复位信号rstsig

i

提高到高电平,将形成具有负反馈构造的差分对的各个参考像素11r和单位像素11

i

的浮动扩散部fd

r

和浮动扩散部fd

i

复位。

[0236]

其后,当在时序t33复位信号rstsig

r

和rstsig

i

下降到低电平时,在从时序t33到时序t34的时段期间,列读出电路单元14读出在垂直信号线vsl0

k

中出现的电压电平作为复位电平(p相),并且通过列信号处理单元15对读出的复位电平进行ad转换。

[0237]

接下来,在从时序t34到时序t35的时段内,通过以脉冲形式将施加给作为信号像素11a的单位像素11

i

的传输晶体管trg

i

的栅极的传输控制信号trgsig

i

提高到高电平,将在单位像素11

i

的光电二极管pd

i

中产生的电荷传输到浮动扩散部fd

i

。

[0238]

类似地,在从时序t34到时序t35的时段内,使施加给各个参考像素11r和单位像素11

i

的选择晶体管sel

r

和sel

i

的栅极的选择控制信号selsig

r

和selsig

i

以脉冲形式下降到低电平,并且施加给伪单元11d2和11d3的选择晶体管seld0和seld1的栅极的选择控制信号seldsig以脉冲形式提高到高电平。由此,形成了反相输入(

‑

输入)和输出被短路的差分放大电路,从而可以防止单位像素11

i

的作为差分对的反相输入的浮动扩散部fd

i

增强且差分

对的电流平衡崩溃的情况。

[0239]

其后,在时序t35,使伪单元11d2和11d3的选择控制信号seldsig下降,并且参考像素11r和单位像素11

i

的选择控制信号selsig

r

和selsig

i

提高,在从时序t35到时序t36的时段期间,通过列读出电路单元14读出在垂直信号线vsl0

k

中出现的电压电平作为信号电平(d相:像素信号),并且通过列信号处理单元15对读出的信号电平进行ad转换。

[0240]

在列信号处理单元15或诸如信号处理单元17等外围电路中,从信号电平(d相)的数字值中减去复位电平(p相)的数字值以执行用于获取与光电二极管pd

i

的接收光量对应的信号成分的数字值的cds处理。

[0241]

随后,在通过使第(i+1)行中的单位像素11

i+1

成为信号像素11a来读出信号电平的时段内(从时序t36到时序t41),类似于通过使第i行中的单位像素11

i

成为信号像素11a来读出信号电平的时段(从时序t11到时序t16),通过在使有效像素区域10v中的所有单位像素11都处于非选择状态的从时序t36到时序t37的时段内使伪单元11d2和11d3的选择晶体管seld0和seld1处于导通状态,形成了包括一对伪单元11d2和11d3、电流镜像电路141和尾电流源单元142的差分放大电路。

[0242]

在从时序t37到时序t38的时段内,使参考像素11r和作为信号像素11a的单位像素11

i+1

的复位晶体管rst

r

和rst

i+1

处于导通状态,将浮动扩散部fd

r

和浮动扩散部fd

i+1

复位,并且在从时序t38到时序t39的时段内,读出在垂直信号线vsl1

k

中出现的复位电平,并且对其进行ad转换。

[0243]

其后,在从时序t39到时序t40的时段内,通过使传输晶体管trg

i+1

处于导通状态,将光电二极管pd

i+1

的电荷传输到浮动扩散部fd

i+1

并且使伪单元11d2和11d3的选择晶体管seld0和seld1处于导通状态,形成了反相输入(

‑

输入)和输出被短路的差分放大电路,从而可以防止单位像素11

i+1

的作为差分对的反相输入的浮动扩散部fd

i+1

增强且差分对的电流平衡崩溃的情况。

[0244]

在从时序t40到时序t41的时段内,读出在垂直信号线vsl1

k

中出现的信号电平并且对其进行ad转换。

[0245]

其后,在列信号处理单元15或诸如信号处理单元17等外围电路中,从信号电平(d相)的数字值中减去复位电平(p相)的数字值以执行用于获取与光电二极管pd的接收光量对应的信号成分的数字值的cds处理。

[0246]

3.4作用和效果

[0247]

如上所述,根据本实施例,类似于第一实施例,在使有效像素区域10v中的所有单位像素11都处于非选择状态的时段(图16中的从时序t31到时序t32和从时序t36到时序t37的时段)期间,反相输入(

‑

输入)和输出被短路的差分放大电路由伪单元11d2和11d3的放大晶体管ampd0和ampd1、电流镜像电路141以及尾电流源单元142形成,并且保持了电流消耗,从而可以保持电源电压vdd和接地电压的下降量。由此,可以防止垂直信号线vsl0

k

和vsl1

k

的稳定时间延长。

[0248]

在将电荷从光电二极管pd传输到浮动扩散部fd的传输时段(图16中的从时序t34到时序t35和从时序t39到时序t40的时段)内,垂直信号线vsl与单位像素11分离,并且垂直信号线vsl的电压电平保持在复位电平,从而可以防止由于传输晶体管trg和浮动扩散部fd的电容耦合引起的馈通而在垂直信号线vsl中产生较大幅度的情况,因此可以防止垂直信

号线vsl的稳定时间延长。

[0249]

其他构造、操作(包括驱动)和效果可以与上述实施例中的构造、操作和效果相同,从而在此将不再重复其详细描述。

[0250]

3.5变形例

[0251]

随后,下面将描述第二实施例的变形例。图17是示出了根据本实施例的变形例的差分型放大读出构造及其外围电路的示意性构造示例的电路图。

[0252]

如图17所示,可以用其中放大晶体管ampd1的栅极连接到放大晶体管ampd1的漏极的伪单元11d4取代上面在第二实施例中参考图15所述的一对伪单元11d2和11d3之中的与信号像素11a对应的伪单元11d3。换句话说,由一对伪单元11d2和11d4形成的伪差分对可以具有反相输入(

‑

输入)和输出被短路的构造。

[0253]

使用这种构造,可以表现出与上述第二实施例相同的效果。其他构造、操作(包括驱动)和效果可以与上述实施例中的构造、操作和效果相同,从而在此将不再重复其详细描述。

[0254]

4.第三实施例

[0255]

接下来,下面将参考附图详细地描述根据第三实施例的固态摄像装置和电子设备。在下面的描述中,将不会通过引用而重复关于与上述实施例中的构造和操作相同的构造和操作的多余描述。

[0256]

上述实施例例示了将形成伪差分对的一对伪单元11d0和11d1、或11d2和11d3/11d4设置在伪差分对形成区域10d中的情况。然而,伪差分对的构造不限于使用一对伪单元11d0和11d1、或11d2和11d3/11d4的放大晶体管ampd0和ampd1的构造。例如,在如第二实施例中所述的将参考像素11r固定为参考专用行中的单位像素11的情况下,可以通过使用参考像素11r代替用于形成伪差分对的两个伪单元11d2和11d3之中的与参考像素11r对应的伪单元11d2来形成伪差分对。

[0257]

4.1差分型放大读出构造的外围电路的示例

[0258]

图18是示出了根据本实施例的差分型放大读出构造及其外围电路的示意性构造示例的电路图。图18中的差分型放大读出构造具有与第二实施例的图14中例示的差分型放大读出构造相同的构造。然而,在图18中,以示例的方式,使图14中的参考像素11r成为有效像素区域10v外部的参考像素区域10r中的单位像素11,并且使信号像素11a成为有效像素区域10v中的单位像素11

i

。

[0259]

如图18所示,除了省略了伪差分对形成区域10d中的与参考像素对应的伪单元11d0,根据本实施例的差分型放大读出构造及其外围电路具有与第二实施例的图15中例示的差分型放大读出构造及其外围电路相同的构造。

[0260]

在该构造中,伪差分对由伪单元11d3的放大晶体管ampd1和参考像素11r的放大晶体管amp

r

构成。

[0261]

4.2在差分型放大读出时的驱动示例(在读出像素和参考像素之间切换)

[0262]

随后,下面将描述在差分型放大读出时的驱动示例。基于图18所示的差分型放大读出构造进行下面的描述。

[0263]

图19是示出了在根据本实施例的差分型放大读出时的驱动示例的时序图。在图19所示的驱动示例中,从时序t51到时序t56,使第i行中的单位像素11

i

成为信号像素11a,并

且从时序t56到时序t61,使第(i+1)行中的单位像素11

i+1

成为信号像素11a。

[0264]

如图19所示,在根据本实施例的差分型放大读出时的驱动中,类似于上面在第二实施例中参考图16所述的驱动示例,输入到参考像素11r的选择晶体管sel

r

的栅极的选择控制信号selsig

r

在驱动中始终保持在高电平。由此,使参考像素11r始终处于选择状态。

[0265]

4.3作用和效果

[0266]

如上所述,根据本实施例,通过使参考像素11r始终处于选择状态,在使有效像素区域10v中的所有单位像素11都处于非选择状态的时段(图19中的从时序t51到时序t52和从时序t56到时序t57的时段)期间,反相输入(

‑

输入)和输出被短路的差分放大电路由伪单元11d3的放大晶体管ampd1、参考像素11r的放大晶体管amp

r

、电流镜像电路141和尾电流源单元142形成,并且保持了电流消耗,从而能够保持电源电压vdd和接地电压的下降量。因此,可以防止垂直信号线vsl0

k

和vsl1

k

的稳定时间延长。

[0267]

在将电荷从光电二极管pd传输到浮动扩散部fd的传输时段(图19中的从时序t54到时序t55和从时序t59到时序t60的时段)内,垂直信号线vsl与单位像素11分离,并且垂直信号线vsl的电压电平保持在复位电平,从而可以防止由于传输晶体管trg和浮动扩散部fd的电容耦合引起的馈通而在垂直信号线vsl中产生较大幅度的情况,因此可以防止垂直信号线vsl的稳定时间延长。

[0268]

其他构造、操作(包括驱动)和效果可以与上述实施例中的构造、操作和效果相同,从而在此将不再重复其详细描述。

[0269]

4.4变形例

[0270]

随后,下面将描述第三实施例的变形例。图20是示出了根据本实施例的变形例的差分型放大读出构造及其外围电路的示意性构造示例的电路图。

[0271]

如图20所示,可以用伪单元11d4取代上面在第三实施例中参考图18所述的与信号像素11a对应的伪单元11d3,在伪单元11d4中,如上面参考图17所述的第二实施例的变形例一样,放大晶体管ampd1的栅极连接到放大晶体管ampd1的漏极。也就是说,由伪单元11d4和参考像素11r形成的伪差分对可以具有反相输入(

‑

输入)和输出被短路的构造。

[0272]

使用这种构造,可以表现出与上述第三实施例相同的效果。其他构造、操作(包括驱动)和效果可以与上述实施例中的构造、操作和效果相同,从而在此将不再重复其详细描述。

[0273]

5.第四实施例

[0274]

接下来,下面将参考附图详细地描述根据第四实施例的固态摄像装置和电子设备。在下面的描述中,将不会通过引用而重复关于与上述实施例中的构造和操作相同的构造和操作的多余描述。

[0275]

5.1差分型放大读出构造的外围电路的示例

[0276]

图21是示出了根据本实施例的差分型放大读出构造及其外围电路的示意性构造示例的电路图。如图21所示,在本实施例中,例如,在与图10中例示的构造相同的构造中,有效像素区域11v中的每个单位像素11具有其中多个(在图21中为两个)光电二极管pd共用一个浮动扩散部fd的构造。传输晶体管trg分别设置在每个光电二极管pd和浮动扩散部fd之间。

[0277]

例如,在图21的单位像素11

i

中,光电二极管pd

m

经由传输晶体管trg

m

连接到浮动扩

散部fd

i

,并且光电二极管pd

m+1

经由传输晶体管trg

m+1

连接到浮动扩散部fd

i

。类似地,在单位像素11

i+1

中,光电二极管pd

m+2

经由传输晶体管trg

m+2

连接到浮动扩散部fd

i+1

,并且光电二极管pd

m+3

经由传输晶体管trg

m+3

连接到浮动扩散部fd

i+1

。

[0278]

以这种方式,即使在有效像素区域10v中的每个单位像素11具有其中光电二极管pd共用一个浮动扩散部fd的构造的情况下,伪差分对形成区域10d中的伪单元11d0和11d1也可以具有与图10中例示的构造相同的构造。

[0279]

本实施例例示了基于上面在第一实施例中参考图10所述的差分型放大读出构造及其外围电路的构造的情况,但是本实施例不限于此。本实施例可以基于上面在第二实施例中参考图15所述的构造或其变形例(参考图17)以及上面在第三实施例中参考图18所述的构造或其变形例(参考图20)等。

[0280]

其他构造、操作(包括驱动)和效果可以与上述实施例中的构造、操作和效果相同,从而在此将不再重复其详细描述。

[0281]

6.第五实施例

[0282]

接下来,下面将参考附图详细地描述根据第五实施例的固态摄像装置和电子设备。在下面的描述中,将不会通过引用而重复关于与上述实施例中的构造和操作相同的构造和操作的多余描述。

[0283]

上述实施例例示了将伪差分对形成区域10d设置在像素阵列单元10中的情况。然而,伪差分对形成区域10d的设置位置不限于像素阵列单元10内部,并且可以例如以将伪差分对形成区域10d设置在诸如列读出电路单元14等外围电路中的方式进行各种变形。

[0284]

6.1cmos图像传感器的系统构造示例

[0285]

图22是示出了根据本实施例的作为安装在电子设备上的固态摄像装置的cmos图像传感器的示意性构造示例的系统构造图。如图22所示,例如,除了伪差分对形成区域10d被设置在列读出电路单元14中,根据本实施例的cmos图像传感器2具有与上面在第一实施例中参考图6所述的cmos图像传感器1的构造相同的构造。

[0286]

6.2差分型放大读出构造的外围电路的示例

[0287]

图23是示出了根据本实施例的差分型放大读出构造及其外围电路的示意性构造示例的电路图。如图23所示,在本实施例中,例如,在与图10中例示的构造相同的构造中,系统控制单元12将选择控制信号seldsig以及复位信号rstdsig0和rstdsig1供应给布置在列读出电路单元14中的伪差分对形成区域10d的伪单元11d0和11d1。

[0288]

以这种方式,伪差分对形成区域10d的设置位置不限于与有效像素区域10v相同的像素阵列单元10内部,并且可以进行各种变形。本实施例例示了基于第一实施例的情况,但是本实施例不限于此。本实施例可以基于第二实施例或其变形例以及第三实施例或其变形例等。

[0289]

7.补充说明

[0290]

7.1单位像素的截面结构示例

[0291]

接下来,下面使用几个示例来描述根据上述实施例的单位像素11的截面结构。

[0292]

7.1.1第一示例

[0293]

第一示例使用示例描述了表面照射型的单位像素11的截面结构。在本说明书中,假设表面照射型为如下结构:其中,假设半导体基板上的元件形成表面为表面,并且光从该

表面侧入射在光电二极管pd上。

[0294]

图24a是示出了根据第一示例的单位像素的截面结构示例的截面图。在图24a中,假设上侧为表面(也称为上表面)。图24a示出了垂直于该表面的表面的截面。

[0295]

如图24a所示,表面照射型的单位像素11包括半导体基板120和设置在半导体基板120的上表面上的布线层110。在半导体基板120的上表面附近,形成有以矩阵状二维布置的光电二极管pd。

[0296]

布线层110具有如下结构:其中,诸如氧化硅膜等绝缘膜112覆盖传输晶体管trg和布线111等,传输晶体管trg电连接到半导体基板120上的每个光电二极管pd,布线111将传输晶体管trg连接到其他像素晶体管(诸如复位晶体管rst、放大晶体管amp和选择晶体管sel等)。传输晶体管trg和布线111被设置在从光电二极管pd的上侧偏移的位置处,因此光接收单元开口区域ap被设置在光电二极管pd的上侧,光通过光接收单元开口区域ap入射在光电二极管pd上。

[0297]

在布线层110的平坦的上表面上,针对每个单位像素11设置有滤色器102和片上透镜101,滤色器102选择性地透射具有特定波长的光,片上透镜101将入射光收集到光电二极管pd。

[0298]

尽管未示出,但是在半导体基板120上的除光电二极管pd的形成区域以外的区域和/或与该区域对应的布线层110中,可以设置有除传输晶体管trg以外的像素晶体管(诸如复位晶体管rst、放大晶体管amp和选择晶体管sel等)、列读出电路单元14、列信号处理单元15或其他外围电路等。

[0299]

例如,这种表面照射型具有易于设计和降低生产成本的优点。

[0300]

7.1.2第二示例

[0301]

第二示例使用示例描述了背面照射型的单位像素11的截面结构。在本说明书中,假设背面照射型为如下结构:其中,假设半导体基板上的元件形成表面的相反侧为背面,并且光从该背面侧入射在光电二极管pd上。

[0302]

图24b是示出了根据第二示例的单位像素的截面结构示例的截面图。在图24b中,假设上侧为背面。图24b示出了垂直于背面的表面的截面。

[0303]

如图24b所示,背面照射型的单位像素11包括半导体基板220、设置在半导体基板220的表面侧的布线层110以及设置在布线层110的上表面上的支撑基板130。

[0304]

在半导体基板220的表面附近,类似于图24a所示的半导体基板120,形成有以矩阵状二维布置的光电二极管pd。然而,通过化学机械抛光(cmp:chemical mechanical polishing)等从背面侧刮削半导体基板220以使其变薄,从而光电二极管pd也设置在背面附近。

[0305]

类似于图24a所示的布线层110,布线层110具有其中绝缘膜112覆盖传输晶体管trg和布线111等的结构。然而,在背面照射型的情况下,不必在布线层110中设置使光入射在光电二极管pd上的光接收开口ap。

[0306]

在半导体基板220的平坦的背面上,针对每个单位像素11设置有选择性地透射具有特定波长的光的滤色器102和将入射光收集到光电二极管pd的片上透镜101。

[0307]

支撑基板130被接合到布线层110的平坦的上表面。例如,支撑基板130可以是诸如硅基板等半导体基板。在支撑基板130上,例如,可以形成有除传输晶体管trg以外的像素晶

体管(诸如复位晶体管rst、放大晶体管amp和选择晶体管sel等)、列读出电路单元14、列信号处理单元15或其他外围电路等。

[0308]

以这种方式,通过使单位像素11具有背面照射型的像素结构,使光入射在光电二极管pd上的开口可以大于表面照射型的开口。因此,可以改善诸如灵敏度和满阱容量(full well capacity)等像素特性。

[0309]

7.2cmos图像传感器的结构示例

[0310]

接下来,下面将使用几个示例来描述根据上述实施例的cmos图像传感器的结构。

[0311]

7.2.1第一示例

[0312]

图25a是示出了根据第一示例的cmos图像传感器的示意性结构示例的示意图。如图25a所示,根据第一示例的cmos图像传感器1a具有半导体基板200被接合到支撑基板210的层叠结构。

[0313]

在半导体基板200上,设置有像素阵列单元10、列读出电路单元14、列信号处理单元15、其他外围电路201(诸如系统控制单元12、垂直驱动单元13、水平驱动单元16、信号处理单元17、像素驱动线ld和垂直像素布线lv等)。例如,像素阵列单元10中的每个单位像素11可以是图24a所示的表面照射型或图24b所示的背面照射型。

[0314]

支撑基板210是用于增强cmos图像传感器1a的强度的构件,并且可以是包括诸如硅基板等半导体基板和诸如陶瓷基板等绝缘基板等的各种基板。在像素阵列单元10中的每个单位像素11是表面照射型的情况下,不必设置支撑基板210。

[0315]

7.2.2第二示例

[0316]

图25b是示出了根据第二示例的cmos图像传感器的示意性结构示例的示意图。如图25b所示,根据第二示例的cmos图像传感器1b具有例如第一半导体基板300和第二半导体基板310通过等离子体接合和cu

‑

cu键合等彼此接合的层叠结构。

[0317]

例如,像素阵列单元10被设置在第一半导体基板300上。另一方面,在第二半导体基板310上,设置有列读出电路单元14、列信号处理单元15和其他外围电路201。例如,像素阵列单元10中的每个单位像素11可以是图24a所示的表面照射型或图24b所示的背面照射型。

[0318]

以这种方式,通过将除像素阵列单元10以外的构造设置在与设置有像素阵列单元10的第一半导体基板300不同的第二半导体基板310上来形成层叠构造,cmos图像传感器1b可以缩小尺寸。另外,像素阵列单元10和其他电路构造可以通过单独的生产工艺形成,从而可以容易地实现生产成本的降低和性能的提高等。

[0319]

上面已经描述了本发明的实施例,但是本发明的技术范围实际上不限于上述实施例,并且在不脱离本发明的主旨的情况下可以进行各种变形。贯穿不同实施例和变形例的组成元件可以适当地彼此组合。

[0320]

在此描述的各个实施例的效果仅为示例,并且效果不限于此。可以表现出其他效果。

[0321]

本技术可以采用如下所述的构造。

[0322]

(1)一种固态摄像装置,其包括:

[0323]

第一垂直信号线和第二垂直信号线;

[0324]

电流镜像电路,其连接到所述第一垂直信号线和所述第二垂直信号线;

[0325]

第一单位像素,其连接到所述第一垂直信号线;

[0326]

第二单位像素,其连接到所述第二垂直信号线;

[0327]

第一单位单元,其连接到所述第一垂直信号线;

[0328]

第二单位单元,其连接到所述第二垂直信号线;

[0329]

电流供应线,其连接到所述第一单位像素和所述第二单位像素以及所述第一单位单元和所述第二单位单元;以及

[0330]

恒流电路,其连接到所述电流供应线,其中,

[0331]

所述第一单位像素的第一放大晶体管、所述第二单位像素的第二放大晶体管、所述电流镜像电路和所述恒流电路构成第一差分放大电路,并且

[0332]

所述第一单位单元的第三放大晶体管、所述第二单位单元的第四放大晶体管、所述电流镜像电路和所述恒流电路构成第二差分放大电路。

[0333]

(2)根据(1)所述的固态摄像装置,其中,所述第一单位单元和所述第二单位单元中的各者不包括对入射光进行光电转换的光电转换元件。

[0334]

(3)根据(1)或(2)所述的固态摄像装置,其中,在所述第二差分放大电路中,构成反相输入的所述第四放大晶体管的栅极和构成输出的所述第四放大晶体管的漏极短路。

[0335]

(4)根据(1)至(3)中任一项所述的固态摄像装置,其包括:

[0336]

多个所述第一单位像素和多个所述第二单位像素,其中,

[0337]

所述多个第一单位像素和所述多个第二单位像素以矩阵状二维布置,

[0338]

所述第一单位像素和所述第二单位像素在列方向上交替地布置,并且

[0339]

所述第二差分放大电路是通过下述方式构造的:在将要读出的单位像素从某个第一单位像素切换到与该第一单位像素相邻的第二单位像素或者从某个第二单位像素切换到与该第二单位像素相邻的第一单位像素时,使所述第一单位单元的选择晶体管和所述第二单位单元的选择晶体管处于导通状态。

[0340]

(5)根据(1)至(3)中任一项所述的固态摄像装置,其包括:

[0341]

多个所述第一单位像素和多个所述第二单位像素,其中,

[0342]

所述多个第一单位像素和所述多个第二单位像素以矩阵状二维布置,

[0343]

在所述多个第一单位像素和所述多个第二单位像素的所述布置中,所述第一单位像素被设置在预定的参考专用行中,并且

[0344]

所述第二差分放大电路是通过下述方式构造的:在将要读出的单位像素从某个第二单位像素切换到与该第二单位像素相邻的另一个第二单位像素时,使所述第一单位单元的选择晶体管和所述第二单位单元的选择晶体管处于导通状态。

[0345]

(6)根据(1)至(5)中任一项所述的固态摄像装置,其中,

[0346]

所述第一单位像素和所述第二单位像素中的各者包括:

[0347]

光电转换元件,其被构造为对入射光进行光电转换;

[0348]

传输晶体管,其被构造为传输在所述光电转换元件中产生的电荷;以及

[0349]

电荷累积单元,其被构造为累积通过所述传输晶体管传输的所述电荷,并且

[0350]

所述第二差分放大电路是通过下述方式构造的:在经由所述传输晶体管将在所述光电转换元件中产生的所述电荷传输到所述电荷累积单元时,使所述第一单位单元的选择晶体管和所述第二单位单元的选择晶体管处于导通状态。

[0351]

(7)根据(1)至(4)中任一项所述的固态摄像装置,其中,

[0352]

所述第一单位像素包括:

[0353]

第一光电转换元件,其被构造为对入射光进行光电转换;

[0354]

第一传输晶体管,其被构造为传输在所述第一光电转换元件中产生的电荷;

[0355]

第一电荷累积单元,其被构造为累积通过所述第一传输晶体管传输的所述电荷;

[0356]

第一复位晶体管,在所述第一复位晶体管中,源极连接到所述第一电荷累积单元,所述第一复位晶体管被构造为排出在所述第一电荷累积单元中累积的所述电荷;

[0357]

所述第一放大晶体管,在所述第一放大晶体管中,漏极连接到所述第一垂直信号线并且源极连接到所述电流供应线,所述第一放大晶体管被构造为使得与在所述第一电荷累积单元中累积的所述电荷对应的电压出现在所述第一垂直信号线中;以及

[0358]

第一选择晶体管,其被构造为切换所述第一放大晶体管的所述漏极和所述第一垂直信号线之间的连接,并且

[0359]

所述第二单位像素包括:

[0360]

第二光电转换元件,其被构造为对入射光进行光电转换;

[0361]

第二传输晶体管,其被构造为传输在所述第二光电转换元件中产生的电荷;

[0362]

第二电荷累积单元,其被构造为累积通过所述第二传输晶体管传输的所述电荷;

[0363]

第二复位晶体管,在所述第二复位晶体管中,源极连接到所述第二电荷累积单元,所述第二复位晶体管被构造为排出在所述第二电荷累积单元中累积的所述电荷;

[0364]

所述第二放大晶体管,在所述第二放大晶体管中,漏极连接到所述第二垂直信号线并且源极连接到所述电流供应线,所述第二放大晶体管被构造为使得与在所述第二电荷累积单元中累积的所述电荷对应的电压出现在所述第二垂直信号线中;以及

[0365]

第二选择晶体管,其被构造为切换所述第二放大晶体管和所述第二垂直信号线之间的连接。

[0366]

(8)根据(7)所述的固态摄像装置,其还包括:

[0367]

第一复位输入线,其连接到所述第一复位晶体管的漏极;

[0368]

第二复位输入线,其连接到所述第二复位晶体管的漏极;

[0369]

第一开关,其被构造为切换所述第一垂直信号线和所述第一复位输入线之间的连接;以及

[0370]

第二开关,其被构造为切换所述第二垂直信号线和所述第二复位输入线之间的连接。

[0371]

(9)根据(1)至(4)中任一项所述的固态摄像装置,其中,

[0372]

所述第一单位单元包括:

[0373]

所述第三放大晶体管,在所述第三放大晶体管中,源极连接到所述电流供应线;以及

[0374]

第三选择晶体管,在所述第三选择晶体管中,源极连接到所述第三放大晶体管的漏极,并且漏极连接到所述第一垂直信号线,并且

[0375]

所述第二单位单元包括:

[0376]

所述第四放大晶体管,在所述第四放大晶体管中,源极连接到所述电流供应线;以及

[0377]

第四选择晶体管,在所述第四选择晶体管中,源极连接到所述第四放大晶体管的漏极,并且漏极连接到所述第二垂直信号线。

[0378]

(10)根据(9)所述的固态摄像装置,其中,

[0379]

所述第一单位单元还包括第三复位晶体管,在所述第三复位晶体管中,源极连接到所述第三放大晶体管的栅极,并且

[0380]

所述第二单位单元还包括第四复位晶体管,在所述第四复位晶体管中,源极连接到所述第四放大晶体管的栅极。

[0381]

(11)根据(10)所述的固态摄像装置,其还包括:

[0382]

第一复位输入线,其连接到所述第三复位晶体管的漏极;

[0383]

第二复位输入线,其连接到所述第四复位晶体管的漏极;

[0384]

第一开关,其被构造为切换所述第一垂直信号线和所述第一复位输入线之间的连接;以及

[0385]

第二开关,其被构造为切换所述第二垂直信号线和所述第二复位输入线之间的连接。

[0386]

(12)根据(9)所述的固态摄像装置,其还包括:

[0387]

第一复位输入线,其连接到所述第三放大晶体管的栅极;以及

[0388]

第二复位输入线,其连接到所述第四放大晶体管的栅极。

[0389]

(13)根据(9)所述的固态摄像装置,其还包括:

[0390]

第一复位输入线,其连接到所述第三放大晶体管的栅极,其中,

[0391]

所述第四放大晶体管的栅极连接到所述第四放大晶体管的所述漏极和所述第四选择晶体管的所述源极。

[0392]

(14)根据(12)或(13)所述的固态摄像装置,其还包括:

[0393]

多个单位像素,其包括所述第一单位像素和所述第二单位像素,其中,

[0394]

所述多个单位像素以矩阵状二维布置,并且

[0395]

在所述多个单位像素的所述布置中,所述第一单位像素被设置在预定的参考专用行中。

[0396]

(15)根据(1)至(14)中任一项所述的固态摄像装置,其还包括:

[0397]

像素阵列单元;以及

[0398]

外围电路,其经由所述第一垂直信号线和所述第二垂直信号线连接到所述像素阵列单元,其中,

[0399]

所述像素阵列单元包括:

[0400]

第一区域,在所述第一区域中,包括所述第一单位像素和所述第二单位像素的多个单位像素以矩阵状二维布置;以及

[0401]

第二区域,在所述第二区域中,包括所述第一单位单元和所述第二单位单元的多个单位单元以行和/或列的形状被布置。

[0402]

(16)根据(1)至(14)中任一项所述的固态摄像装置,其还包括:

[0403]

像素阵列单元;以及

[0404]

外围电路,其经由所述第一垂直信号线和所述第二垂直信号线连接到所述像素阵列单元,其中,

[0405]

所述像素阵列单元包括第一区域,在所述第一区域中,包括所述第一单位像素和所述第二单位像素的多个单位像素以矩阵状二维布置,并且

[0406]

所述外围电路包括第二区域,在所述第二区域中,包括所述第一单位单元和所述第二单位单元的多个单位单元以行和/或列的形状被布置。

[0407]

(17)根据(16)所述的固态摄像装置,其中,所述外围电路是被构造为经由所述第一垂直信号线或所述第二垂直信号线从所述第一单位像素或所述第二单位像素读出像素信号的读出电路单元。

[0408]

(18)根据(15)至(17)中任一项所述的固态摄像装置,其包括:

[0409]

第一芯片,其包括所述像素阵列单元;以及

[0410]

第二芯片,其接合到所述第一芯片,并且包括所述外围电路。

[0411]

(19)一种固态摄像装置,其包括:

[0412]

第一垂直信号线和第二垂直信号线;

[0413]

电流镜像电路,其连接到所述第一垂直信号线和所述第二垂直信号线;

[0414]

参考像素,其连接到所述第一垂直信号线;

[0415]

单位像素,其连接到所述第二垂直信号线;

[0416]

单位单元,其连接到所述第二垂直信号线;

[0417]

电流供应线,其连接到所述单位像素、所述参考像素和所述单位单元;以及

[0418]

恒流电路,其连接到所述电流供应线,其中,

[0419]

所述参考像素的第一放大晶体管、所述单位像素的第二放大晶体管、所述电流镜像电路和所述恒流电路构成第一差分放大电路,并且

[0420]

所述参考像素的所述第一放大晶体管、所述单位单元的第三放大晶体管、所述电流镜像电路和所述恒流电路构成第二差分放大电路。

[0421]

(20)一种电子设备,其包括:

[0422]

第一垂直信号线和第二垂直信号线;

[0423]

电流镜像电路,其连接到所述第一垂直信号线和所述第二垂直信号线;

[0424]

第一单位像素,其连接到所述第一垂直信号线;

[0425]

第二单位像素,其连接到所述第二垂直信号线;

[0426]

第一单位单元,其连接到所述第一垂直信号线;

[0427]

第二单位单元,其连接到所述第二垂直信号线;

[0428]

电流供应线,其连接到所述第一单位像素和所述第二单位像素以及所述第一单位单元和所述第二单位单元;

[0429]

恒流电路,其连接到所述电流供应线;以及

[0430]

转换单元,其连接到所述第一垂直信号线和所述第二垂直信号线,并且被构造为将出现在所述第一垂直信号线或所述第二垂直信号线中的模拟电压转换为数字电压值,其中,

[0431]

所述第一单位像素的第一放大晶体管、所述第二单位像素的第二放大晶体管、所述电流镜像电路和所述恒流电路构成第一差分放大电路,并且

[0432]

所述第一单位单元的第三放大晶体管、所述第二单位单元的第四放大晶体管、所述电流镜像电路和所述恒流电路构成第二差分放大电路。

[0433]

(21)一种电子设备,其包括:

[0434]

第一垂直信号线和第二垂直信号线;

[0435]

电流镜像电路,其连接到所述第一垂直信号线和所述第二垂直信号线;

[0436]

参考像素,其连接到所述第一垂直信号线;

[0437]

单位像素,其连接到所述第二垂直信号线;

[0438]

单位单元,其连接到所述第二垂直信号线;

[0439]

电流供应线,其连接到所述单位像素、所述参考像素和所述单位单元;

[0440]

恒流电路,其连接到所述电流供应线;以及

[0441]

转换单元,其连接到所述第二垂直信号线,并且被构造为将出现在所述第二垂直信号线中的模拟电压转换为数字电压值,其中,

[0442]

所述参考像素的第一放大晶体管、所述单位像素的第二放大晶体管、所述电流镜像电路和所述恒流电路构成第一差分放大电路,并且

[0443]

所述参考像素的所述第一放大晶体管、所述单位单元的第三放大晶体管、所述电流镜像电路和所述恒流电路构成第二差分放大电路。

[0444]

附图标记列表

[0445]

1、1a、1b、2

ꢀꢀ

cmos图像传感器

[0446]

10

ꢀꢀ

像素阵列单元

[0447]

10v

ꢀꢀ

有效像素区域

[0448]

10d

ꢀꢀ

伪差分对形成区域

[0449]

10r

ꢀꢀ

参考像素区域

[0450]

11

ꢀꢀ

单位像素

[0451]

11a

ꢀꢀ

信号像素

[0452]

11b、11r

ꢀꢀ

参考像素

[0453]

11d、11d0至11d4

ꢀꢀ

伪单元

[0454]

12

ꢀꢀ

系统控制单元

[0455]

13

ꢀꢀ

垂直驱动单元

[0456]

14

ꢀꢀ

列读出电路单元

[0457]

15

ꢀꢀ

列信号处理单元

[0458]

16

ꢀꢀ

水平驱动单元

[0459]

17

ꢀꢀ

信号处理单元

[0460]

20

ꢀꢀ

adc

[0461]

101

ꢀꢀ

片上透镜

[0462]

102

ꢀꢀ

滤色器

[0463]

110

ꢀꢀ

布线层

[0464]

111

ꢀꢀ

布线

[0465]

112

ꢀꢀ

绝缘膜

[0466]

120、220、200

ꢀꢀ

半导体基板

[0467]

130、210

ꢀꢀ

支撑基板

[0468]

141

ꢀꢀ

电流镜像电路

[0469]

142

ꢀꢀ

尾电流源单元

[0470]

201

ꢀꢀ

外围电路

[0471]

300

ꢀꢀ

第一半导体基板

[0472]

310

ꢀꢀ

第二半导体基板

[0473]

amp、ampd

ꢀꢀ

放大晶体管

[0474]

ap

ꢀꢀ

光接收单元开口区域

[0475]

fd

ꢀꢀ

浮动扩散部

[0476]

ld

ꢀꢀ

像素驱动线

[0477]

lv

ꢀꢀ

垂直像素布线

[0478]

lrst

ꢀꢀ

复位晶体管驱动线

[0479]

lsel

ꢀꢀ

选择晶体管驱动线

[0480]

ltrg

ꢀꢀ

传输晶体管驱动线

[0481]

mp0、mp1

ꢀꢀ

pmos晶体管

[0482]

pd

ꢀꢀ

光电二极管

[0483]

rst、rstd

ꢀꢀ

复位晶体管

[0484]

sel、seld

ꢀꢀ

选择晶体管

[0485]

sw、sw0至sw5

ꢀꢀ

开关

[0486]

trg

ꢀꢀ

传输晶体管

[0487]

vcom

ꢀꢀ

垂直电流供应线

[0488]

vrd

ꢀꢀ

垂直复位输入线

[0489]

vsl、vsl0、vsl1

ꢀꢀ

垂直信号线

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1