高电子迁移率晶体管及其制作方法与流程

1.本发明涉及一种高电子迁移率晶体管及其制作方法。

背景技术:

2.以氮化镓基材料(gan-based materials)为基础的高电子迁移率晶体管具有于电子、机械以及化学等特性上的众多优点,例如宽能隙、高击穿电压、高电子迁移率、大弹性模数(elastic modulus)、高压电与压阻系数(high piezoelectric and piezoresistive coefficients)等与化学钝性。上述优点使氮化镓基材料可用于如高亮度发光二极管、功率开关元件、调节器、电池保护器、面板显示驱动器、通讯元件等应用的元件的制作。

技术实现要素:

3.本发明一实施例揭露一种制作高电子迁移率晶体管(high electron mobility transistor,hemt)的方法。首先形成一缓冲层于一基底上,然后形成一第一阻障层于该缓冲层上,形成一第一硬掩模于该第一阻障层上,去除该第一硬掩模以及该第一阻障层以形成一凹槽,形成一第二阻障层于该凹槽内,再形成一p型半导体层于该第二阻障层上。

4.本发明另一实施例揭露一种制作高电子迁移率晶体管(high electron mobility transistor,hemt)的方法。首先形成一缓冲层于一基底上,形成一阻障层于该缓冲层上,形成一第一硬掩模于该阻障层上,形成一第二硬掩模于该第一硬掩模上,去除该第二硬掩模以及该第一硬掩模以形成一凹槽,再形成一p型半导体层于该阻障层上。

5.本发明又一实施例揭露一种高电子迁移率晶体管(high electron mobility transistor,hemt),其主要包含一缓冲层设于一基底上、一p型半导体层设于该阻障层上、一第一阻障层设于该阻障层及该p型半导体层之间、一第二阻障层设于该第一阻障层两侧且第一阻障层及第二阻障层包含不同厚度、一栅极电极设于该p型半导体层上以及一源极电极以及一漏极电极设于该栅极电极两侧的该阻障层上。

附图说明

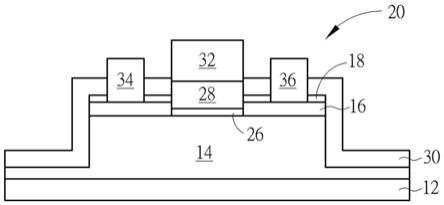

6.图1至图5为本发明一实施例制作一高电子迁移率晶体管的方法示意图;

7.图6至图10为本发明一实施例制作一高电子迁移率晶体管的方法示意图。

8.主要元件符号说明

9.12

ꢀꢀꢀꢀꢀ

基底

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

14

ꢀꢀꢀꢀ

缓冲层

10.16

ꢀꢀꢀꢀꢀ

第一阻障层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

18

ꢀꢀꢀꢀ

第一硬掩模

11.20

ꢀꢀꢀꢀꢀ

mesa区域

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

22

ꢀꢀꢀꢀ

第二硬掩模

12.24

ꢀꢀꢀꢀꢀ

凹槽

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

26

ꢀꢀꢀꢀ

第二阻障层

13.28

ꢀꢀꢀꢀꢀ

p型半导体层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

30

ꢀꢀꢀꢀ

保护层

14.32

ꢀꢀꢀꢀꢀ

栅极电极

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

34

ꢀꢀꢀꢀ

源极电极

15.36

ꢀꢀꢀꢀꢀ

漏极电极

16.42

ꢀꢀꢀꢀꢀ

基底

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

44

ꢀꢀꢀꢀ

缓冲层

17.46

ꢀꢀꢀꢀꢀ

阻障层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

48

ꢀꢀꢀꢀ

第一硬掩模

18.50

ꢀꢀꢀꢀꢀ

第二硬掩模

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

52

ꢀꢀꢀꢀ

mesa区域

19.54

ꢀꢀꢀꢀꢀ

第三硬掩模

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

56

ꢀꢀꢀꢀ

凹槽

20.58

ꢀꢀꢀꢀꢀ

p型半导体层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

60

ꢀꢀꢀꢀ

保护层

21.62

ꢀꢀꢀꢀꢀ

栅极电极

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

64

ꢀꢀꢀꢀ

源极电极

22.66

ꢀꢀꢀꢀꢀ

漏极电极

具体实施方式

23.请参照图1至图5,图1至图5为本发明一实施例制作一高电子迁移率晶体管的方法示意图。如图1所示,首先提供一基底12,例如一由硅、碳化硅或氧化铝(或可称蓝宝石)所构成的基底,其中基底12可为单层基底、多层基底、梯度基底或上述的组合。依据本发明其他实施例基底12又可包含一硅覆绝缘(silicon-on-insulator,soi)基底。

24.然后于基底12表面形成一缓冲层14。在一实施例中,缓冲层14包含iii-v族半导体例如氮化镓,其厚度可介于0.5微米至10微米之间。在一实施例中,可利用分子束外延制作工艺(molecular-beam epitaxy,mbe)、有机金属气相沉积(metal organic chemical vapor deposition,mocvd)制作工艺、化学气相沉积(chemical vapor deposition,cvd)制作工艺、氢化物气相外延(hydride vapor phase epitaxy,hvpe)制作工艺或上述组合于基底12上形成缓冲层14。

25.接着形成一第一阻障层16于缓冲层14表面。在本实施例中第一阻障层16较佳包含iii-v族半导体例如氮化铝镓(al

x

ga

1-x

n),其中0<x<1,x较佳小于等于20%,且第一阻障层16较佳包含一由外延成长制作工艺所形成的外延层。如同上述形成缓冲层14的方式,可利用分子束外延制作工艺(molecular-beam epitaxy,mbe)、有机金属气相沉积(metal organic chemical vapor deposition,mocvd)制作工艺、化学气相沉积(chemical vapor deposition,cvd)制作工艺、氢化物气相外延(hydride vapor phase epitaxy,hvpe)制作工艺或上述组合于缓冲层14上形成第一阻障层16。需注意的是,本实施例中第一阻障层16虽直接设置于缓冲层14表面,但依据本发明另一实施例又可选择于缓冲层14与第一阻障层16之间额外形成一金属氮化层(图未示)包含例如但不局限于氮化铝,此变化型也属本发明所涵盖的范围。随后形成一第一硬掩模18于第一阻障层16表面。在本实施例中,第一硬掩模18较佳包含氮化硅且其厚度约略5纳米,但不局限于此。

26.随后如图2所示,进行一平台隔离(mesa isolation)制作工艺定义出mesa区域20与主动区域,使元件之间可独立运作而不致受到彼此交互影响。在本实施例中,平台隔离制作工艺可利用一光刻暨蚀刻制作工艺图案化或以蚀刻去除部分第一硬掩模18、部分第一阻障层16以及部分缓冲层14,其中被图案化的第一硬掩模18、第一阻障层16以及缓冲层14较佳具有相同宽度且三者之间的边缘较佳相互切齐,而剩余且未被图案化的部分缓冲层14则与基底12包含相同宽度。

27.然后如图3所示,先全面性形成一第二硬掩模22于第一硬掩模18上,包括第一硬掩模18上表面与侧壁、第一阻障层16侧壁、缓冲层14侧壁以及设于mesa区域20两侧的缓冲层14表面,再进行一光刻暨蚀刻制作工艺去除部分第二硬掩模22、部分第一硬掩模18以及部

分第一阻障层16以形成一凹槽24并同时暴露出缓冲层14表面。

28.如图4所示,接着形成一第二阻障层26于凹槽24内,形成一p型半导体层28于第二阻障层26上,再去除第二硬掩模22暴露出下方的第一硬掩模18。在本实施例中,第一阻障层16与第二阻障层26较佳包含不同铝浓度或更具体而言第二阻障层26的铝浓度较佳小于第一阻障层16的铝浓度。举例来说,若第一阻障层16包含iii-v族半导体例如氮化铝镓(al

x

ga

1-x

n),则其中0<x<1,x较佳介于15~50%。第二阻障层26若同样包含iii-v族半导体例如氮化铝镓(al

x

ga

1-x

n),则其中0<x<1,x较佳介于5~15%。p型半导体层28则较佳包含p型氮化镓。

29.另外,第二阻障层26厚度较佳小于第一阻障层16厚度,例如第一阻障层16厚度较佳介于15纳米至50纳米而第二阻障层26厚度则较佳介于5纳米至15纳米。如同上述形成第一阻障层16的方式,可利用分子束外延制作工艺(molecular-beam epitaxy,mbe)、有机金属气相沉积(metal organic chemical vapor deposition,mocvd)制作工艺、化学气相沉积(chemical vapor deposition,cvd)制作工艺、氢化物气相外延(hydride vapor phase epitaxy,hvpe)制作工艺或上述组合于凹槽内的缓冲层14表面形成第二阻障层26及p型半导体层28。

30.随后如图5所示,先形成一保护层30于第一硬掩模18、p型半导体层28及mesa区域20两侧的缓冲层14表面,再形成一栅极电极32于p型半导体层28上以及源极电极34与漏极电极36于栅极电极32两侧。在本实施例中,可先进行一光刻暨蚀刻制作工艺去除p型半导体层28正上方的部分保护层30形成凹槽(图未示),形成一栅极电极32于凹槽内,去除栅极电极32两侧的部分保护层30及部分第一硬掩模18形成二凹槽,再分别形成源极电极34与漏极电极36于栅极电极32两侧。

31.在本实施例中,栅极电极32、源极电极34以及漏极电极36较佳由金属所构成,其中栅极电极32较佳由萧特基金属所构成而源极电极34与漏极电极36较佳由欧姆接触金属所构成。依据本发明一实施例,栅极电极32、源极电极34及漏极电极36可各自包含金、银、铂、钛、铝、钨、钯或其组合。在一些实施例中,可利用电镀制作工艺、溅镀制作工艺、电阻加热蒸镀制作工艺、电子束蒸镀制作工艺、物理气相沉积(physical vapor deposition,pvd)制作工艺、化学气相沉积制作工艺(chemical vapor deposition,cvd)制作工艺、或上述组合于上述凹槽内形成导电材料,然后再利用单次或多次蚀刻将电极材料图案化以形成栅极电极32、源极电极34以及漏极电极36。至此即完成本发明一实施例的一高电子迁移率晶体管的制作。

32.请在参照图5,图5另揭露本发明一实施例的一高电子迁移率晶体管的结构示意图。如图5所示,高电子迁移率晶体管主要包含缓冲层14设于基底12上,p型半导体层28设于缓冲层14上,第一阻障层16设于p型半导体层28两侧,第二阻障层26设于缓冲层14及p型半导体层28之间,栅极电极32设于p型半导体层28上以及源极电极34以及一漏极电极36设于栅极电极32两侧的第一阻障层16上,其中p型半导体层28侧壁较佳切齐第二阻障层26侧壁。

33.在本实施例中,第一阻障层16与第二阻障层26较佳包含不同厚度,例如第二阻障层26厚度较佳小于第一阻障层16厚度。另外第一阻障层16与第二阻障层26较佳包含不同铝浓度或更具体而言第二阻障层26的铝浓度较佳小于第一阻障层16的铝浓度。举例来说,若第一阻障层16包含iii-v族半导体例如氮化铝镓(al

x

ga

1-x

n),则其中0<x<1,x较佳介于15~

50%。第二阻障层26若同样包含iii-v族半导体例如氮化铝镓(al

x

ga

1-x

n),则其中0<x<1,x较佳介于5~15%。p型半导体层28则较佳包含p型氮化镓。

34.请参照图6至图10,图6至图10为本发明一实施例制作一高电子迁移率晶体管的方法示意图。如图6所示,首先提供一基底42,例如一由硅、碳化硅或氧化铝(或可称蓝宝石)所构成的基底,其中基底42可为单层基底、多层基底、梯度基底或上述的组合。依据本发明其他实施例基底42又可包含一硅覆绝缘(silicon-on-insulator,soi)基底。

35.然后于基底42表面形成一缓冲层44。在一实施例中,缓冲层44包含iii-v族半导体例如氮化镓,其厚度可介于0.5微米至10微米之间。在一实施例中,可利用分子束外延制作工艺(molecular-beam epitaxy,mbe)、有机金属气相沉积(metal organic chemical vapor deposition,mocvd)制作工艺、化学气相沉积(chemical vapor deposition,cvd)制作工艺、氢化物气相外延(hydride vapor phase epitaxy,hvpe)制作工艺或上述组合于基底42上形成缓冲层44。

36.接着形成一阻障层46于缓冲层44表面。在本实施例中阻障层46较佳包含iii-v族半导体例如氮化铝镓(al

x

ga

1-x

n),其中0<x<1,且阻障层46较佳包含一由外延成长制作工艺所形成的外延层。如同上述形成缓冲层14的方式,可利用分子束外延制作工艺(molecular-beam epitaxy,mbe)、有机金属气相沉积(metal organic chemical vapor deposition,mocvd)制作工艺、化学气相沉积(chemical vapor deposition,cvd)制作工艺、氢化物气相外延(hydride vapor phase epitaxy,hvpe)制作工艺或上述组合于缓冲层44上形成阻障层46。如同前述实施例,本实施例中阻障层46虽直接设置于缓冲层44表面,但依据本发明另一实施例又可选择于缓冲层44与阻障层46之间额外形成一金属氮化层(图未示)包含例如但不局限于氮化铝,此变化型也属本发明所涵盖的范围。

37.随后依序形成一第一硬掩模48以及一第二硬掩模50于阻障层46表面。在本实施例中,第一硬掩模48与第二硬掩模50较佳包含不同材料,其中第一硬掩模48较佳包含氮化硅且其厚度约略5纳米,第二硬掩模50较佳包含氧化硅,但不局限于此。

38.如图7所示,接着进行一平台隔离(mesa isolation)制作工艺定义出mesa区域52与主动区域,使元件之间可独立运作而不致受到彼此交互影响。在本实施例中,平台隔离制作工艺可利用一光刻暨蚀刻制作工艺图案化或以蚀刻去除部分第二硬掩模50、部分第一硬掩模48、部分阻障层46以及部分缓冲层44,其中被图案化的第二硬掩模50、第一硬掩模48、阻障层46以及缓冲层44较佳具有相同宽度且四者之间的边缘较佳切齐,而剩余且未被图案化的部分阻障层44则与基底42包含相同宽度。

39.如图8所示,先形成一第三硬掩模54于第二硬掩模50上,包括第二硬掩模50顶部、第二硬掩模50侧壁、第一硬掩模48侧壁、阻障层46侧壁以及缓冲层44侧壁,再进行一光刻暨蚀刻制作工艺去除部分第三硬掩模54、部分第二硬掩模50以及部分第一硬掩模48形成凹槽56暴露出阻障层46表面但不去除任何阻障层46。换句话说本实施例于形成凹槽56后凹槽56正下方的阻障层46与凹槽56两侧的阻障层46较佳具有相同厚度。在本实施例中,第三硬掩模54与第二硬掩模50较佳包含相同材料,例如两者均由氧化硅所构成,但不局限于此。

40.随后如图9所示,先形成一p型半导体层58于凹槽56内的阻障层46上,再去除第三硬掩模54与第二硬掩模50暴露出下方的第一硬掩模48。如同前述实施例,p型半导体层58较佳包含p型氮化镓,且如同上述形成阻障层46的方式,可利用分子束外延制作工艺

(molecular-beam epitaxy,mbe)、有机金属气相沉积(metal organic chemical vapor deposition,mocvd)制作工艺、化学气相沉积(chemical vapor deposition,cvd)制作工艺、氢化物气相外延(hydride vapor phase epitaxy,hvpe)制作工艺或上述组合于凹槽56内的阻障层46表面形成p型半导体层58。

41.最后如图10所示,先形成一保护层60于第一硬掩模48上以及mesa区域52两侧的缓冲层44表面,再形成一栅极电极62于p型半导体层58上以及源极电极64与漏极电极66于栅极电极62两侧。在本实施例中,可先进行一光刻暨蚀刻制作工艺去除p型半导体层58正上方的部分保护层60形成凹槽,形成一栅极电极62于凹槽内,去除栅极电极62两侧的部分保护层60及部分第一硬掩模48形成二凹槽,再分别形成源极电极64与漏极电极66于栅极电极62两侧。

42.在本实施例中,栅极电极62、源极电极64以及漏极电极66较佳由金属所构成,其中栅极电极62较佳由萧特基金属所构成而源极电极64与漏极电极66较佳由欧姆接触金属所构成。依据本发明一实施例,栅极电极62、源极电极64及漏极电极66可各自包含金、银、铂、钛、铝、钨、钯或其组合。在一些实施例中,可利用电镀制作工艺、溅镀制作工艺、电阻加热蒸镀制作工艺、电子束蒸镀制作工艺、物理气相沉积(physical vapor deposition,pvd)制作工艺、化学气相沉积制作工艺(chemical vapor deposition,cvd)制作工艺、或上述组合于上述凹槽内形成导电材料,然后再利用单次或多次蚀刻将电极材料图案化以形成栅极电极62、源极电极64以及漏极电极66。至此即完成本发明一实施例的一高电子迁移率晶体管的制作。

43.综上所述,本发明主要先形成一由例如氮化硅所构成的硬掩模于algan阻障层表面,去除部分硬掩模与阻障层形成凹槽,再形成p型半导体层及栅极电极于凹槽内。依据本发明的优选实施例,覆盖于algan阻障层表面的硬掩模可于凹槽形成时用来保护algan阻障层,避免阻障层受到蚀刻剂伤害并改善后续形成保护层后可能产生的应力损害(stress degradation)。

44.以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1