压敏电阻的制作方法

[0001]

本申请涉及电子元器件领域,具体而言涉及压敏电阻。

背景技术:

[0002]

现有的压敏电阻中,压敏电阻内部一般采用多层电极并联或者串联的结构,但是因为制造工艺的影响,电极层间的厚度极差以及各电极之间对位准确性不足,这导致电极之间的间距以及平行电容板之间的面积存在一定偏差,所以对压敏电阻的电性一致性影响非常大,而电性的分散直接影响产品在实际电路中的保护精度;对于小电容压敏电阻而言,当采用多层串联电极结构时,压敏电压可以做得非常高,但是电性一致性也非常分散,导致在低压电路环境中不适用,在高压电路环境保护精度不足等问题。

[0003]

申请内容

[0004]

基于此,本申请提供一种压敏电阻,以解决目前压敏电阻保护精度低、应用范围不广的问题。其申请内容为:

[0005]

一种压敏电阻,所述压敏电阻包括压敏电阻本体、端电极、侧电极和内电极;所述压敏电阻本体包括压敏电阻层,所述端电极包括左端电极和右端电极,所述侧电极包括左侧电极和右侧电极,所述内电极包括左内电极和右内电极;所述左端电极和右端电极分别设置于所述压敏电阻本体的两端;所述压敏电阻层开设有两个孔槽,所述两个孔槽内分别安装有左内电极和右内电极,所述左内电极的部分或者全部落入所述右内电极的正投影涵盖范围之内而与所述右内电极形成电容结构;所述左侧电极的一端与所述左内电极电连接,另一端则与所述左端电极电连接;所述右侧电极的一端与所述右内电极连接,另一端则与所述右端电极电连接。

[0006]

在某些实施方式中,所述左内电极和所述右内电极相互平行。

[0007]

在某些实施方式中,所述左内电极和所述右内电极尺寸相同。

[0008]

在某些实施方式中,所述孔槽开设于所述压敏电阻层的侧表面。

[0009]

在某些实施方式中,所述孔槽开设于所述压敏电阻层的内部。

[0010]

在某些实施方式中,所述左端电极与所述左侧电极一体成型,和/或所述右端电极与所述右侧电极一体成型。

[0011]

在某些实施方式中,所述左侧电极与所述左内电极一体成型,和/或所述右侧电极与所述右内电极一体成型。

[0012]

在某些实施方式中,所述压敏电阻本体包括多个压敏电阻层,所述多个压敏电阻层层叠设置。

[0013]

在某些实施方式中,所述压敏电阻还包括上基板和下基板,所述压敏电阻本体设置于所述上基板和下基板的中间。

[0014]

本实施例的压敏电阻,利用两孔槽的内电极形成平行板电容结构,利用两槽间距形成压敏电性,可以避免传统制造工艺造成的电极对位准确性问题,从而提高压敏电阻的电性一致性,一方面使得压敏电阻具备更高的保护精度,另一方面,在小电容压敏电阻中,

因为该结构电性一致性好,因此可以做到更低的压敏电压,使得该压敏电阻可适用于更低工作电压的电路环境。

附图说明

[0015]

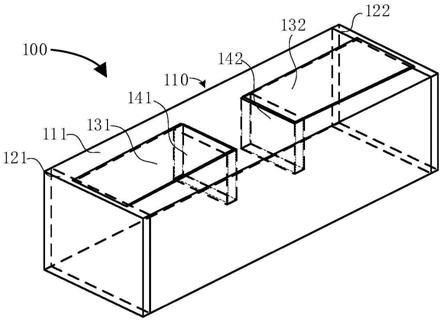

图1为本申请一实施例提供的一种压敏电阻的立体结构示意图;

[0016]

图2为本申请一实施例提供的一种压敏电阻的压敏电阻本体的立体结构示意图;

[0017]

图3为本申请一实施例提供的一种压敏电阻结构的俯视图;

[0018]

图4为本申请另一实施例提供的一种压敏电阻结构的俯视图;

[0019]

图5为本申请另一实施例提供的一种压敏电阻的压敏电阻本体的立体结构示意图;

[0020]

图6为本申请另一实施例提供的一种压敏电阻的立体结构示意图;

[0021]

图7为本申请另一实施例提供的一种压敏电阻的a-a剖面图。

具体实施方式

[0022]

为了使本申请的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本申请进行进一步详细说明。在不冲突的情况下,下述各个实施例及其技术特征可以相互组合。应当理解,此处所描述的具体实施例仅用以解释本申请,并不用于限定本申请。

[0023]

本申请提供一种压敏电阻,该压敏电阻可以是片式压敏电阻等多种形态,具体不做限定。参见图1,为本申请一实施例中该压敏电阻的结构示意图,在该实施例中,压敏电阻100包括压敏电阻本体110、端电极、侧电极和内电极,所述压敏电阻本体110包括压敏电阻层111,所述端电极包括左端电极121和右端电极122,所述侧电极包括左侧电极131和右侧电极132,所述内电极包括左内电极141和右内电极142;所述左端电极121和右端电极122分别设置于所述压敏电阻本体110的两端。参见图2,所述压敏电阻层111开设有两个孔槽151和152,所述两个孔槽内分别安装有左内电极141和右内电极142,所述左内电极141的部分或者全部落入所述右内电极142的正投影涵盖范围之内,则左内电极141和右内电极142则可以形成电容结构,当该左内电极141和该右内电极142平行时,该电容结构是平行板电容,当然,在其他情况下,也可以是其他结构电容,此外该左内电极141和该右内电极142的尺寸可以是相同的,以保证更好的电性特征,所述左内电极和所述右内电极可以采用浆料填充的方式形成于所述孔槽内。

[0024]

在本实施例中,参见图3,压敏电阻层111上的孔槽151和152可以开设在压敏电阻层111的表面,开槽方式可以是机械开孔、激光开孔、光刻、蚀刻中的一种或者多种,在此不做限定。作为一种可选的孔槽尺寸,两条槽的大小可以一致,开槽深度可以小于或者等于压敏电阻层的厚度,开槽宽度可以在1-20μm之间,开槽长度可以在50-500μm之间,槽间距离可以在10-800μm之间。此外,在这种方案中,两个孔槽相对设置,槽内分别安装有左内电极141和右内电极142,两个内电极可以形成一个平行板的电容结构。作为一种可选的实施方式,上述两个内电极可以采用电极浆料填充的方式形成。参见图4,而左侧电极131和右侧电极132则安装于压敏电阻层111的表面,左右两侧电极的成型方式可以是丝网印刷、钢板印刷、光刻、蚀刻的一种或者多种。左侧电极131的一端与左内电极141电连接,另一端则与左端电极121电连接,从而实现左端电极121与左内电极141的电连接;右侧电极132的一端与右内

电极142连接,另一端则与所述右端电极122电连接,从而实现右端电极122与右内电极142的电连接。此外,上述左侧电极和右侧电极与槽内电极的宽度可以一致,并且左侧电极132不超过左侧孔槽151的右边界,右侧电极131不超过右侧孔槽152的左边界。

[0025]

本申请另一实施例中,除上述实施例所述的结构之外,压敏电阻的结构还可以参见图5和图6,其中,压敏电阻层111上的孔槽151和152可以开设在压敏电阻层111的内部,开槽方式可以是机械开孔、激光开孔、光刻、蚀刻中的一种或者多种。此外,在这种方案中,两个孔槽相对设置,槽内分别安装有左内电极141和右内电极142,两个内电极可以形成一个电容结构,作为一种可选的实施方式,上述两个内电极还可以采用电极浆料填充的方式形成。参见图7,左侧电极131和右侧电极132则可以安装于压敏电阻层111的内部,左侧电极131的一端与左内电极141电连接,另一端则与左端电极121电连接,从而实现左端电极121与左内电极141的电连接;右侧电极132的一端与右内电极142连接,另一端则与所述右端电极122电连接,从而实现右端电极122与右内电极142的电连接。

[0026]

在本实施例中,参见图7,两个孔槽可以分别与所述左端电极121和右端电极122平行设置,而所述两个孔槽或者两个内电极(左内电极和右内电极)则可以相互平行设置,孔槽或者两个内电极(左内电极和右内电极)的尺寸也可以相同。所述左端电极121可以与左侧电极131一体成型,相同的,所述右端电极122可以与右侧电极132一体成型。此外,左侧电极131与所述左内电极141一体成型,所述右侧电极132还可以与所述右内电极142一体成型。

[0027]

在本实施例中,压敏电阻本体110还可以包括多个压敏电阻层,多个压敏电阻层成叠设置组成压敏电阻本体,其中各个压敏电阻层可以采用图2或者图5所示的孔槽设置方案,即在一个压敏电阻中的压敏电阻层可以采用表面开孔槽或者内部孔槽等方式,并且组成由不同开孔结构的压敏电阻层组成的压敏电阻本体110。此外,参见图7,压敏电阻100还可以包括上基板161和下基板162,所述压敏电阻本体110则可以作为中间电极层基板设置于所述上基板161和下基板162的中间。上基板161和下基板162则可以用于使该压敏电阻与外界绝缘,或者保护盖压敏电阻本体等。

[0028]

在本实施例中,通过提供在压敏电阻内部开孔槽安装内电极和侧电极的技术方案,以及提供多个压敏电阻层所组成的压敏电阻结构,提供更多的实施可能方案。此外还通过完善压敏电阻的上、下基板,使得压敏电阻能有更好的性能。

[0029]

为更好的说明本申请的有益效果,发明人分别进行了以下实验:

[0030]

实验一:

[0031]

采用本申请上述实施例中的压敏电阻作为发明产品1,该发明产品1的外形尺寸为(1.0

±

0.15)*(0.5

±

0.15)*(0.5

±

0.15)mm,压敏电压vb的参考范围为22-28v,电容cp的参考范围为2.5-7.5pf。此外采用现有技术串联或者并联结构的压敏电阻作为对比产品1,该对比产品1与上述发明产品1的尺寸、压敏电压vb的参考范围和电容cp的参考范围都相同。此外,保证发明产品1与对比产品1采用同种压敏电阻材料制作而成,保证材料参数相同,两个压敏电阻中的两个电极的相交面积和上下两个电极间距相同,以保证发明产品1与对比产品1的压敏电压vb与电容cp设计范围一致。

[0032]

分别对发明产品1和对比产品1进行测试,测试结果表明:发明产品1的压敏电压vb的实测范围为24-24.6v,电容cp的实测范围为4.89-5.25pf;而对比产品1的压敏电压vb的

实测范围为22.7-27.2v,电容cp的实测范围为3.28-6.63pf。以上实验结果可以表明,在相同电性设计参考范围内,发明产品1的各项电性精度均优于对比产品1,使该压敏电阻在相同参考范围的产品中具有更高的保护精度。

[0033]

实验二:

[0034]

采用本申请上述实施例中的压敏电阻作为发明产品2,该发明产品2的外形尺寸为(1.0

±

0.15)*(0.5

±

0.15)*(0.5

±

0.15)mm,电容值cp参考范围为0.25-1pf。此外采用传统串联结构小电容压敏电阻作为对比产品2,对比产品2的尺寸与上述发明产品2的尺寸、电容cp的参考范围都相同,此外两者采用同种压敏电阻材料制作而成,保证材料参数一致;两者的压敏电压vb则在100-160v之间。

[0035]

测试以上发明产品2与对比产品2中压敏电阻的压敏电压vb以及电容cp的分布,测试结果表面:发明产品2的压敏电压vb的实测范围为11.85-12.69v,电容cp的实测范围为0.47-0.66pf,对比产品2的压敏电压vb的实测范围为105.1-158.6v,电容cp的实测范围为0.23-1.35pf。

[0036]

以上实验结果表明,相比于传统串联结构设计的小电容压敏电阻,采用相同材料,本发明的压敏电阻的压敏电压可以做到更低,使得小电容产品可以应用于更低电压的电路工作环境,同时压敏电压vb和电容cp的精度可以做到更高,使该压敏电阻在相同参考范围的产品中具有更高的保护精度。

[0037]

综上,本实施例的压敏电阻,利用两孔槽的内电极形成平行板电容结构,利用两槽间距形成压敏电性,可以避免传统制造工艺造成的电极对位准确性问题,从而提高压敏电阻的电性一致性,一方面使得压敏电阻具备更高的保护精度,另一方面,在小电容压敏电阻中,因为该结构电性一致性好,可以做到更低的压敏电压,使得该压敏电阻可适用于更低工作电压的电路环境。

[0038]

尽管已经相对于一个或多个实现方式示出并描述了本申请,但是本领域技术人员基于对本说明书和附图的阅读和理解将会想到变型和修改。本申请包括所有这样的修改和变型,并且仅由所附权利要求的范围限制。特别地关于由上述组件执行的各种功能,用于描述这样的组件的术语旨在对应于执行所述组件的指定功能(例如其在功能上是等价的)的任意组件(除非另外指示),即使在结构上与执行本文所示的本说明书的示范性实现方式中的功能的公开结构不等同。此外,尽管本说明书的特定特征已经相对于若干实现方式中的仅一个被公开,但是这种特征可以与如可以对给定或特定应用而言是期望和有利的其他实现方式的一个或多个其他特征组合。而且,就术语“包括”、“具有”、“含有”或其变形被用在具体实施方式或权利要求中而言,这样的术语旨在以与术语“包含”相似的方式包括。进一步地,应当理解的是,在本文中提及的“多个”是指两个或两个以上。对于本文中提及的步骤,其通过数字后缀仅仅是为了清晰表述实施例,便于理解,并不完全代表步骤执行的先后顺序,应当以逻辑关系的先后设定为思考

[0039]

以上所述仅为本申请的实施例,并非因此限制本申请的专利范围,凡是利用本申请说明书及附图内容所作的等效结构或等效流程变换,例如各实施例之间技术特征的相互结合,或直接或间接运用在其他相关的技术领域,均同理包括在本申请的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1