一种具有凹陷沟槽的场效应晶体管的制作方法

1.本发明涉及场效应晶体管,具体公开了一种具有凹陷沟槽的场效应晶体管。

背景技术:

2.场效应晶体管属于电压控制型半导体器件,具有输入电阻高、噪声小、功耗低、动态范围大、易于集成、没有二次击穿、安全工作区域宽等优点,场效应晶体管可应用于开关器件。

3.如图1所示,传统的场效应晶体管为以下结构:在衬底中设置两个间隔的漏极和源极,栅极设置于漏极和源极之间的上方,栅极与衬底之间设置金属氧化物层以确保绝缘性能,衬底分别与漏极和源极的导电型极性相反,漏极和源极之间的衬底中可形成导电沟道,但这种结构的场效应晶体管阻抗较大,为降低阻抗,部分场效应晶体管设置栅极陷入到衬底中,但这种场效应晶体管的栅极容易被击穿而导致失效。

技术实现要素:

4.基于此,有必要针对现有技术问题,提供一种具有凹陷沟槽的场效应晶体管,具有较高的抗击穿电压,整体结构稳定可靠,使用寿命长。

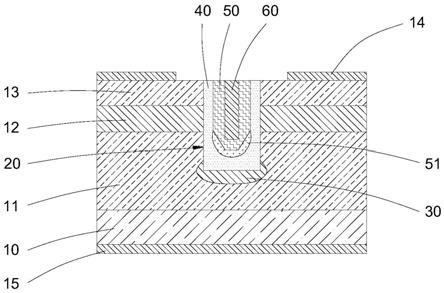

5.为解决现有技术问题,本发明公开一种具有凹陷沟槽的场效应晶体管,包括衬底,衬底上依次层叠有外延层、沟道掺杂层、源极层和源极金属层,沟道掺杂层和源极层的厚度之和为d,衬底下设有漏极金属层,外延层中设有贯穿沟道掺杂层、源极层和源极金属层的凹槽;凹槽的底部设有位于外延层中的保护层,保护层呈u形包裹于凹槽的底部,保护层与沟道掺杂层之间形成有间隔;凹槽中填充有栅极电介质层,栅极电介质层中设有栅极沉积层,栅极沉积层的底部设有抗击层,栅极沉积层中设有栅极金属层,栅极金属层、栅极沉积层和栅极电介质层的顶面共面,栅极金属层的高度为h,h>d;栅极电介质层的介电常数大于10,抗击层的介电常数小于4;衬底、外延层和源极层均为掺杂有第一导电型离子的半导体材料层,沟道掺杂层和保护层均为掺杂有第二导电型离子的半导体材料层,第一导电型和第二导电型的极性相反。

6.进一步的,衬底、外延层和源极层均为掺杂有磷离子的单晶硅层,沟道掺杂层和保护层均为掺杂有硼离子的单晶硅层。

7.进一步的,保护层的宽度为r,凹槽的宽度为l,1.2l≤r≤1.8l。

8.进一步的,栅极电介质层为氧化镧层或二氧化钛层。

9.进一步的,栅极沉积层为氮化钛层或氮化钽层。

10.进一步的,栅极沉积层的底部为向下收窄的圆台状。

11.进一步的,抗击层为二氧化硅层或ptfe层。

12.进一步的,栅极金属层为钨层或铝层。

13.本发明的有益效果为:本发明公开一种具有凹陷沟槽的场效应晶体管,通过将栅极区域设置在凹槽中,可有效降低场效应晶体管的阻抗,栅极区域对导电沟道的调节迅速且可靠,此外,具有低介电常数的抗击层具有良好的强电场抵抗能力,可有效提高抗击穿电压,保护层与外延层之间形成的pn结可削弱抗击层处形成的电场,能够进一步提高抗击穿电压,整体结构耐压性能好、稳定性强,使用寿命长。

附图说明

14.图1为传统场效应晶体管的结构示意图。

15.图2为本发明的结构示意图。

16.附图标记:衬底10、外延层11、沟道掺杂层12、源极层13、源极金属层14、漏极金属层15、凹槽20、保护层30、栅极电介质层40、栅极沉积层50、抗击层51、栅极金属层60。

具体实施方式

17.为能进一步了解本发明的特征、技术手段以及所达到的具体目的、功能,下面结合附图与具体实施方式对本发明作进一步详细描述。

18.参考图2。

19.本发明实施例公开一种具有凹陷沟槽的场效应晶体管,包括衬底10,衬底10上沿纵向依次层叠有外延层11、沟道掺杂层12、源极层13和源极金属层14,沟道掺杂层12的厚度和源极层13的厚度之和为d,衬底10下设有漏极金属层15,外延层11中设有依次贯穿沟道掺杂层12、源极层13和源极金属层14的凹槽20,凹槽20的开口向上;凹槽20的底部设有延展位于外延层11中的保护层30,保护层30呈u形包裹于凹槽20的底部,保护层30与沟道掺杂层12之间形成有间隔,能够避免保护层30对狗到处造成影响;凹槽20中的结构都属于栅极区域,凹槽20中填充有栅极电介质层40,栅极电介质层40中设有贯穿其顶面的栅极沉积层50,栅极沉积层50能够有效提高场效应晶体管中栅极区域的储电能力,从而提高场效应晶体管的性能,栅极沉积层50的底部设有抗击层51,抗击层51位于栅极沉积层50与栅极电介质层40之间,栅极沉积层50中设有贯穿其顶面的栅极金属层60,栅极金属层60的顶面、栅极沉积层50的顶面和栅极电介质层40的顶面共面,栅极金属层60的纵向高度为h,h>d,确保栅极金属层60能够配合栅极沉积层50对沟道掺杂层12中的导电沟道实现可靠的调节;栅极电介质层40的介电常数大于10,使用高介电常数的材料制作栅极电介质层40,能够提高对整体栅极区域对沟道掺杂层12中导电沟道调节的响应速度,栅极对导电沟道的调节效果好,且栅极金属层60分别与外延层11、沟道掺杂层12、源极层13的绝缘效果可靠,抗击层51的介电常数小于4,使用低介电常数的材料制作抗击层51,能够有效提高该区域的强电场抵抗能力,耐压性能好,抗击穿能力好,可有效提高场效应晶体管的可靠性;栅极沉积层50为功函数金属层,衬底10、外延层11和源极层13均为掺杂有第一导电型离子的半导体材料层,沟道掺杂层12和保护层30均为掺杂有第二导电型离子的半导体材料层,第一导电型和第二导电型的极性相反,即当第一导电型为p型时第二导电型则为n

型,当第一导电型为n型时第二导电型则为p型,保护层30与外延层11之间形成有pn结,能够有效削弱抗击层51区域的电场,从而有效提高场效应晶体管的抗击穿电压,能够有效避免场效应晶体管的栅极区域被击穿。优选地,外延层11的掺杂浓度大于衬底10的掺杂浓度。

20.本发明中沟道掺杂层12中能够形成纵向的导电沟道,从而令源极金属层14和漏极金属层15实现导通,而栅极沉积层50配合具有高介电常数的栅极电介质层40,能够有效提高对导电沟道的调节效果及调节的可靠性;栅极沉积层50末端的设置具有低介电常数的抗击层51,具有优异的强电场抵抗能力,场效应晶体管耐压性能好、抗击穿能力强;此外,具备相反极性的保护层30与外延层11之间形成有pn结,能够有效削弱抗击层51区域的电场,从而进一步提高场效应晶体管的抗击穿性能。

21.在本实施例中,衬底10、外延层11和源极层13均为掺杂有磷离子的单晶硅层,掺杂有磷离子的单晶硅层的导电型为n型,沟道掺杂层12和保护层30均为掺杂有硼离子的单晶硅层,掺杂硼离子的单晶硅层的导电型为p型;或衬底10、外延层11和源极层13均掺杂有硼离子的单晶硅层,沟道掺杂层12和保护层30均为掺杂有磷离子的单晶硅层。

22.在本实施例中,保护层30的横向宽度为r,凹槽20的横向宽度为l,1.2l≤r≤1.8l,能够有效确保保护层30对栅极电介质层40底部的包覆效果,确保该区域所形成的pn结的跨越范围足够大,从而有效提高其对抗击层51区域电场的削弱能力。

23.在本实施例中,栅极电介质层40为氧化镧层或二氧化钛层,二氧化钛的介电常数为48。

24.在本实施例中,栅极沉积层50为氮化钛层或氮化钽层。

25.在本实施例中,栅极沉积层50的底部为向下收窄的圆台状,即栅极沉积层50的截面形状为上底位于下方的等腰梯形,栅极沉积层50底部收窄的区域配合抗击层51能够有效提高电场分布的均匀性,从而提高场效应晶体管中栅极区域的抗击穿能力。

26.在本实施例中,抗击层51为二氧化硅层或ptfe层,二氧化硅的介电常数为3.9,ptfe全称聚四氟乙烯,介电常数为2.55。

27.在本实施例中,栅极金属层60为钨层或铝层,钨和铝的电阻都较低,能够有效提高栅极金属层60的导电性能,从而有效提高场效应晶体管的性能,漏极金属层15和源极金属层14也可以为钨层或铝层。

28.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1