一种基于多层凹嵌式基板的多器件封装单体化结构的制作方法

1.本发明涉及利用基板的多器件封装设计技术领域,具体涉及一种基于多层凹嵌式基板的多器件封装单体化结构,尤其是一种基于多层凹嵌式基板不同工艺的多芯片cib(chip in board)封装的单体化集成结构。

背景技术:

2.至今各种涉及电子信息系统的设备及终端,根据应用,大多需要小型化、集成化和多芯片集成化。至今为止不同工艺的多个器件或多个芯片采用sip(system in package)封装结构来实现,外表如同一颗芯片。sip封装需要以封装基板和树脂成型模具。在多个(一般情况数百只)sip单体注塑成面积较大的sip集合体过程中,为了不易翘曲剥离,要求封装基板与封装树脂的热膨胀系数较接近,由于这正是保障切割成单体sip封装体品质的必要条件之一。但封装基板比常规塑封用的引线框架成本高,加之sip模具费用昂贵,难以实现低成本的多器件集成化封装。

3.例如,中国专利授权号zl201920060815.7揭示了一种基于多层凹嵌式基板的芯片天线单体化结构。以超小型基板为基础的基板的上表面布局天线、基板下面的开口凹嵌空间内封装芯片、基板下表面电极焊装在母版上的超小型化集成封装与天线一体化的结构。芯片和天线的单体化集成结构在多层基板面的表层可设计加工出所需天线结构,在多层基板的背层一部分形成凹嵌空间,使多层基板作为封装母框体,将裸芯片以点胶形式封装在凹嵌空间内。该发明的最主要的封装就是表面天线与凹嵌空间的芯片形成一体化集成结构。

4.在许多场合,并不使用表面天线与凹嵌空间的芯片形成一体化集成结构,因此,需要去掉上述表面天线,仅仅利用多层基板作为多器件的封装载体。因此本发明与上述专利不同。仅仅针对如何利用多层基板的凹嵌空间,使得不同工艺制作出来的器件,在凹嵌空间内实现封装集成。

技术实现要素:

5.在不同制作工艺多器件的集成化过程中,诞生了诸如mcm、sip和芯片堆叠等多种封装形态。mcm裸片点胶的外形不规则、高度比较高;sip虽然具有线条布线细及高密度pin点多的特点,但封装基板和模具成本高限制了其低成本的推广;芯片堆叠封装虽然体积小,但成本也高,封装的高技术要求带来成品率难以保证。而本发明的一种基于多层凹嵌式基板的多器件封装单体化结构,恰恰可以解决上述问题,实现低成本和短周期的灵活设计加工和大规模化工业生产。

6.因此,本发明针对上述需求,创新性地设计一种满足终端小型化、可满足灵活设计、低成本和薄型化需要,将多器件在基板内部形成小型化的立体集成封装结构,形成单一的封装外表。本发明的目的是通过以下技术方案实现的。

7.具体的,根据本发明的一个方面,本发明公开了一种基于多层凹嵌式基板的多器

件封装单体化结构,包括:

8.多层基板、多层基板信号线、多层基板接地线、底层电极、接地电极;其中,

9.所述多层基板的下表面具有凹嵌空间,所述凹嵌空间内放置至少一颗芯片和至少一个有源或无源器件,所述芯片和器件通过焊接层材料焊接在多层基板的凹嵌空间内层基板衬底上;

10.所述器件的第一电极通过所述多层基板信号线与底层电极连接,所述器件的第二电极通过芯片电极引线连接所述芯片;

11.所述芯片通过芯片电极引线分别连接所述器件的第二电极和连接电极,并通过所述连接电极连接所述多层基板接地线。

12.优选的,所述芯片为裸芯片。

13.优选的,所述凹嵌空间内进一步填充有封装树脂,以覆盖所述裸芯片。

14.优选的,所述封装树脂不超过所述多层基板的下表面水平线。

15.优选的,所述芯片为封装芯片,所述芯片电极引线替换为芯片管脚,所述封装芯片通过芯片管脚焊接固定到所述器件的第二电极和连接电极。

16.优选的,所述无源器件包括以下中的至少一种:表贴电容、电感、电阻、晶体振荡器、敏感材料器件、厚膜、薄膜。

17.优选的,在所述凹嵌空间的顶部涂敷有一层保护胶。

18.优选的,所述多层基板信号线通过对应的层间连线孔连接底层电极,多层基板接地线通过对应的层间连线孔连接接地电极。

19.本发明的优点在于:本发明利用廉价的电路基板,设计出了一种基于多层凹嵌式基板的芯片与其他器件封装集成的单体化结构,这种结构多芯片器件集成体封装在多层基板的凹嵌内部。此外该封装基板背面槽外框设定各种电极,因此可以简单焊接在其他母板表面。

20.另外,本发明利用传统低成本的pcb多层基板,设计出一种基于多层凹嵌式基板的多器件封装单体化结构,凹嵌式基板内部可设计出以pcb基板为灵活布线的连接方式,在凹嵌式空间来实现表贴各种不同工艺的器件互联与集成,在凹嵌空间内点胶加热成型。该结构有以下特点:

21.1、sip采用下部是树脂,上部是封装基板的布局结构。基于多层凹嵌式基板的外框结构,器件表贴在凹嵌空间内,之后点胶密封。因此多层凹嵌式基板的外框结构中,点胶固化后,普通的多层pcb板也不易发生翘曲剥离现象。

22.2、避免了高昂的sip模具加工费用和新结构的加工周期。基于多层凹嵌式基板的多器件封装单体化结构只需普通pcb加工工艺即可实现其基板框架。设计灵活、成本低和加工周期短(数天),而定制sip模具一般长达数月。

23.3、成本低。一种基于多层凹嵌式基板的多器件单体化结构封装的成本只有同等sip结构封装的几分之一。

附图说明

24.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本发明

的限制。而且在整个附图中,用相同的参考符号表示相同的部件。在附图中:

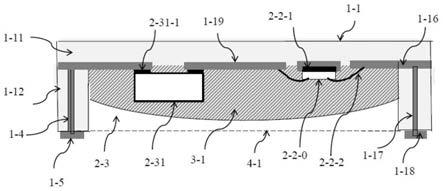

25.图1

‑

1一种基于多层凹嵌式基板的第一实施例的多器件封装单体化结构示意图;

26.图1

‑

2一种基于多层凹嵌式基板的多器件封装单体化结构的上表面俯视示意图;

27.图1

‑

3一种基于多层凹嵌式基板的多器件封装单体化结构的上底面仰视示意图;

28.图2一种基于多层凹嵌式基板的第二实施例的已封装芯片的多器件封装单体化结构示意图;

29.图3一种基于多层凹嵌式基板的第三实施例的已封装芯片的多器件封装单体化结构示意图。

具体实施方式

30.下面将参照附图更详细地描述本公开的示例性实施方式。虽然附图中显示了本公开的示例性实施方式,然而应当理解,可以以各种形式实现本公开而不应被这里阐述的实施方式所限制。相反,提供这些实施方式是为了能够更透彻地理解本公开,并且能够将本公开的范围完整的传达给本领域的技术人员。

31.在不同制作工艺多器件的集成化过程中,诞生了诸如mcm、sip和芯片堆叠等多种封装形态。mcm裸片点胶的外形不规则、高度比较高;sip虽然具有线条布线细及高密度pin点多的特点,但封装基板和模具成本高限制了其低成本的推广;芯片堆叠封装虽然体积小,但成本也高,封装的高技术要求带来成品率难以保证。本发明提供的一种基于多层凹嵌式基板的多器件封装单体化结构,恰恰可以解决上述问题,实现低成本和短周期的灵活设计加工和大规模化工业生产。

32.因此,本发明针对上述需求,创新性地设计一种满足终端小型化、可满足灵活设计、低成本和薄型化需要,将多器件在基板内部形成小型化的立体集成封装结构,形成单一的封装外表。本发明的目的是通过以下技术方案实现的。

33.该系统结构发明思路为如何设计一种低成本的小型化芯片与多器件载体结构,实现不同芯片器件间电路低成本灵活可配置功能。

34.如图1

‑

1所示,图1

‑

1是一种基于多层凹嵌式基板的多器件封装单体化结构示意图,本发明的意图是在多层基板1

‑

1底面加工出一个凹嵌空间2

‑

3。把裸芯片2

‑2‑

0借助芯片焊接层材料2

‑2‑

1焊接在多层基板的内层基板衬底上。根据设计布线要求,通过芯片电极引线2

‑2‑

2、电极1

‑

16和层间连线孔1

‑

17,接入到基板电极线1

‑

18(也是接地电极)。裸芯片2

‑2‑

0与器件2

‑

31通过链接多层基板连线1

‑

19相连接。当然,电极1

‑

16、电极1

‑

19、层间连线孔1

‑

17(孔内具有多层基板接地线)和外围基板电极1

‑

18(也是接地电极)等可以根据芯片器件的系统要求,在基板底面自由设计。1

‑

11、1

‑

12为绝缘层,1

‑

4为层间连线孔(孔内具有多层基板信号线)连接底层电极1

‑

5和器件的电极。2

‑

31

‑

1为器件焊接层材料,将器件2

‑

31焊接在多层基板的内层基板衬底上。

35.完成芯片和器件的装配及器件贴装后,在基板的凹嵌空间内填充封装树脂3

‑

1,并加热使树脂固化。

36.此外,要强调的是,该多层基板的凹嵌空间内的封装树脂3

‑

1不得超过凹嵌空间界面4

‑

1。

37.结构图如图1

‑

2和1

‑

3所示,表示了芯片天线一体化基板结构的实际在设备中的上

面图和底面图。上表面是平整基板,基板的底层电极1

‑

5、接地电极1

‑

18等与其他母板焊接,当然,底层的电极1

‑

5和接地电极1

‑

18等多个基板外围电极,可以根据芯片器件的信号线、接地线和电源线的系统要求,在基板底面自由设计。

38.在本发明的系统实际设计中,芯片也可以采购封装好的芯片,如一种基于多层凹嵌式基板的含有已封装芯片的多器件封装单体化结构示意图,即图2所示,器件可以是封装芯片2

‑2‑

0,通过芯片管脚2

‑2‑

1焊接固定到基板内部凹嵌部金属连接线1

‑

16和1

‑

19上,然后填装树脂3

‑

1。

39.在本发明的系统实际设计中,芯片也采购封装好的芯片,如一种基于多层凹嵌式基板的含有已封装芯片的多器件封装单体化结构示意图,即图3所示,器件可以是封装芯片2

‑2‑

3,通过芯片管脚2

‑2‑

4焊接固定到基板内部凹嵌部金属连接线1

‑

16和1

‑

19上,不用额外填装树脂3

‑

1。此外为了防止表贴好的smt芯片和器件在母版上再次smt表贴装配时,由于芯片和器件的重量原因可能会发生脱落,可在多层凹嵌涂敷一层保护胶5

‑

1。

40.本实施例利用廉价的电路基板,设计出了一种基于多层凹嵌式基板的多器件封装单体化结构。这种结构芯片和器件装配在多层基板的凹嵌内部,可以在利用基板进行芯片和器件间的辅助电路布设,不用每次新的结构封装的引线框架和封装模具的制作,把包含芯片的多器件放入普通基板凹嵌内部,多基板衬底及引线设计灵活。封装凹嵌式基板内的芯片,可以是裸芯片、也可以是树脂封装好的芯片。可降低费用和制作周期,这是本发明的基本特点和优点。

41.本发明可以低成本地进行灵活的少量试料测试(pilot)。并可以进行快速的系统级的功能和性能的初期、中试评估。各批次芯片的性能离散的特性进行调节,通过安装在凹嵌内部的芯片外围电路器件选择,灵活进行参数配置调节来实现其优化功能。

42.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1