一种基于多阻变层的阻变存储器件及其制备方法与流程

1.本发明属于半导体和cmos混合集成电路技术领域,具体涉及一种基于多阻变层的阻变存储器及制备方法。

背景技术:

2.随着摩尔定律极限的逼近,冯诺依曼结构的弊端越来越明显,表现为低存储效率和高功耗。与此同时,伴随互联网技术的迭代更新,人工智能技术对于存储器件提出了更高的要求。非冯诺依曼结构,具体表现为近存和存算一体化技术对新型非易失性器件的需求逐渐上升,其中电阻型阻变存储器(rram)凭借其简单三层结构(上电极,阻变层,下电极),低功耗,高密度集成,读写速度快等优势成为代替传统闪存的有力竞争者。在低操作电压的情况下,界面型rram拥有两个状态“高电阻hrs”,“低电阻lrs”,对应数字电路中的“1”和“0”状态,相应的物理图像为电场作用下,氧空位(氧离子)发生迁移运动形成非金属性导电区域;当电极和功能层存在肖特基势垒,氧空位在界面处的积累就会导致势垒高度的变化从而影响阻变开关过程,近似于氧空位导电细丝控制开关过程。界面型的rram拥有诸多特点,例如高擦写次数10

12

,开关速度小于1ns等。随着工艺与设计的优化,multi-bit rram也逐渐广泛流通,状态数从1bit上升到2bit等。

3.不过对于界面型rram器件,其可靠度一直是研究的问题,例如器件的retention特性,表现为器件的状态(例如“0”和“1”状态)保持时间长短。在存储阵列中,当通过字线和位线施加电压改变器件的电阻,富氧区变宽,氧空位导电丝形成,界面处势垒下降,器件从hrs变成lrs。但随着时间的流逝、工艺误差以及周围环境的影响,例如层层间接触不佳,相近器件传来的热量、周围被选通的存储器件提供的漏电流等,会导致器件阻变层中离子的迁移复合氧空位以及相应的导电丝变化,严重的是可能会导致filament的断裂,使存储信息改变。

4.为了解决阻变存储器阵列面临的retention问题,目前的研究主要是停留在变化材料或者调整阻变层厚度上。例如在工艺中改变阻变层材料与氧气混合比(改变ao

x

中x的数值),尝试多种不同的材料比如(sio

x

,hfo

x

,tao

x

,vo

x

等)或者加厚加粗阻变层(例如从10a加厚到100a等),或者在器件周围增加包裹层(sinx等),以达到retention提高的目的。但是多种材料的选择会带来各自的缺陷,例如状态数的下降(某些材料大部分只能达到少于2bit状态数),retention的提高并不明显等问题。

技术实现要素:

5.鉴于上述不足,本发明提出了一种阻变存储器件,利用传统cmos工艺来实现具有高retention的阻变存储器件,通过调整界面处势垒以期降低甚至消除阻变存储器的crossbar结构中存在的阻变层离子迁移问题。

6.为了解决上述技术问题,本发明采用的技术方案如下:

7.一种阻变存储器,其特征在于,该阻变存储器的阻变层由拦截特性薄膜和具有阻

变特性的阻变材料薄膜交替叠加构成,形成n层阻变层结构,n≥3。

8.所述阻变材料薄膜采用具有阻变特性的过渡金属氧化物,厚度为5nm-100nm;或采用有机材料,厚度为200nm-500nm;所述过渡金属氧化物为tao

x

、hfo

x

、sio

x

或srtio3等一类材料,所述有机材料为parylene。

9.所述拦截特性薄膜采用sio

x

,bn,石墨烯,石墨等,厚度为1nm~10nm。

10.一种阻变存储器的制备方法,包括如下步骤:

11.1)定义底电极图形,按照该图形在衬底上制备底电极;

12.2)采用pvd(物理气相淀积)、ald(原子层淀积)或cvd(化学气相沉积)的方法在底电极上淀积阻变材料薄膜;

13.3)采用pvd或ald的方法在阻变材料薄膜上淀积拦截特性薄膜,并根据材料属性进行相应的退火处理工序;

14.4)重复2)和3)步骤

15.5)定义底电极引出孔图形,按照该图形在阻变材料薄膜和拦截特性薄膜刻蚀出底电极引出孔;

16.6)定义顶电极图形,按照该图形在修饰层上制备顶电极。

17.进一步地,所述步骤1)、5)和6)中定义图形的方法是,利用光刻技术在光刻胶上定义图形。

18.进一步地,所述底电极和顶电极的制备方法包括pvd和蒸发淀积方法。

19.进一步地,所述衬底采用硅或玻璃;所述底电极和顶电极采用活性材料或者惰性材料,例如w,au,tin,pt等,厚度为10nm-400nm。

20.进一步地,所述阻变材料薄膜采用具有阻变特性的过渡金属氧化物,厚度为5nm-50nm;或采用有机材料,厚度为200nm-500nm。

21.进一步地,所述拦截特性薄膜采用石墨烯,bn,siox等,厚度为1nm-10nm。

22.本发明提出了一种基于多阻变层的阻变存储器及其制备方法,通过调控层与层界面势垒用于优化氧空位迁移问题,通过合理设计阻变材料薄膜、拦截特性薄膜和电极材料的结合,可以实现对阻变存储器件的电流-电压特性进行优化,使该阻变存储器展现出高状态保持的特性。该阻变存储器在结合界面性rram多重优势的基础上也具有高可靠度特性,使用多拦截特性薄膜将原本形成少量/单一导电丝的阻变层,分割为多节导电丝,并通过调高界面处离子迁移的能量势垒降低氧空位迁移概率;优化原本由于氧空位迁移导致电阻状态变化的问题,所以可以有效地抑制器件的低保持力。同时,器件多阻变层结构也有利于增加器件的状态数。本发明为实现阻变存储器大规模集成以及商业化铺平了道路。

附图说明

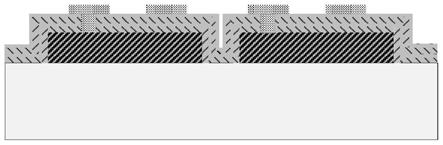

23.图1-7对应于各实施例的实施步骤。

24.图8为图1-7的图例说明。

具体实施方式

25.为使本发明的上述特征和优点能更明显易懂,下文特举实施实例,并配合所附图作详细说明如下。

26.本实施例提供一种基于多阻变层的阻变存储器及其制备方法,该阻变存储器采用硅衬底,采用tin作为底电极材料,采用tao2(或其非化学配比的氧化物)作为阻变材料薄膜,采用石墨烯和薄层sio2作为拦截特性薄膜,采用tin作为顶电极材料。

27.sio2和tao2均是与标准cmos工艺相兼容的材料。基于tao2的阻变存储器具有超快的开关速度,高的开关比,多状态数,良好的保持特性,其制备简单且非常可控。石墨烯和sio2能在垂直于平面方向上对离子移动进行限制,这几种材料的优势相结合,加上合理的物理机制层面的设计,势垒高度的调整,既满足兼容cmos工艺的要求,又能实现阻变存储器良好的性能以及可靠度特性,对于阻变存储器crossbar结构阵列集成密度的提升和大规模生产有着重要的意义。

28.该阻变存储器的制备方法如下:

29.1)利用光刻技术在光刻胶上定义底电极图形,采用pvd方法在硅衬底上淀积tin底电极材料,厚度为70nm,再去除光刻胶,如图1所示;

30.2)采用ald方法在底电极上淀积一层tao2阻变材料薄膜,厚度为6nm,如图2所示;

31.3)采用ald方法在阻变材料薄膜上淀积一层sio2拦截特性薄膜用于界面势垒的调整,厚度为3nm,如图3所示;

32.4)采用ald方法在底电极上淀积一层tao2阻变材料薄膜,厚度为6nm,如图4所示;

33.5)采用ald方法在阻变材料薄膜上淀积一层多层石墨烯拦截特性薄膜用于界面势垒的调整,大约厚度为2~10层,如图5所示;

34.6)先用光刻技术在光刻胶上定义出来的底电极引出孔图形,并去除光刻胶,如图6所示;

35.7)利用光刻技术在光刻胶上定义顶电极图形,采用pvd方法在能带修饰层上淀积tin顶电极材料,厚度为100nm,再去除光刻胶即得到该阻变存储器,如图7所示。

36.由上述实施例可知,制备过渡金属氧化物阻变材料薄膜和拦截特性薄膜,既可以采用pvd方法,也可以采用ald方法,与pvd方法相比,ald方法能够制备更薄;制备有机材料作阻变材料薄膜采用cvd方法。

37.以上实施例仅用以说明本发明的技术方案而非对其进行限制,本领域的普通技术人员可以对本发明的技术方案进行修改或者等同替换,而不脱离本发明的精神和范围,本发明的保护范围应以权利要求所述为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1