基板和集成封装器件的制作方法

1.本实用新型属于led封装技术领域,具体涉及一种基板和集成封装器件。

背景技术:

2.随着照明技术的发展,将led光源像素化,实现智慧型矩阵式照明成为发展趋势,特别是在车用智能照明及显示领域上,对能兼容更高像素的封装结构的需求日益迫切。现有技术大多采用将多个芯片分别进行独立封装后再贴装在pcb上的技术,或采用cob(板上芯片封装技术)技术,通过引线将芯片与线路板键合,再用封装胶将芯片与引线进行封装。

3.将多个芯片进行独立封装后再贴装在pcb板上,一方面由于封装后的led结构尺寸较大,进而限制了整个pcb板的尺寸;另一方面,贴装后不同像素之间间距较大,较难实现高分辨率像素显示,出光不均匀。

4.而采用cob(板上芯片封装技术)技术,通过引线将芯片与线路板键合,再用封装胶将芯片与引线进行封装,由于需保留引线焊接位置,故封装尺寸较大。

5.因此,需要一种新的技术以解决现有技术中封装器件难以实现高分辨率、封装尺寸较大扰的问题。

技术实现要素:

6.为解决现有技术中的封装器件难以实现高分辨率、封装尺寸较大的问题,本实用新型提供了一种基板和集成封装器件。

7.本实用新型采用了以下技术方案:

8.一种基板,用于集成封装器件,包括图形化的导电层、隔绝结构层和芯片焊盘单元;

9.所述导电层设有至少三层并叠层排列;

10.所述隔绝结构层设有若干层并分别插设在相邻两所述导电层之间并与导电层连接固定,所述隔绝结构层包括一基体层和至少一绝缘层;

11.所述芯片焊盘单元用于连接发光芯片,所述芯片焊盘单元设有若干个并在顶层的隔绝结构层上排列成矩阵;非底层的各导电层分别与至少一行芯片焊盘单元对应,且一行芯片焊盘单元仅对应一导电层;

12.所述芯片焊盘单元设有若干类且分别与各所述导电层对应,各类芯片焊盘单元均设置在顶层的隔绝结构层上;

13.底层导电层与其上方的各非底层导电层分别通过导通孔连接;顶层导电层与对应的芯片焊盘单元连接;非顶层导电层分别与对应的芯片焊盘单元通过连通孔连接。

14.在一些实施例中,所述顶层导电层包括若干第一边缘焊盘和若干第一图形引线,所述第一图形引线的一端连接所述第一边缘焊盘,另一端连接对应的所述芯片焊盘单元,所述第一边缘焊盘通过所述导通孔与所述底层导电层连接。

15.在一些实施例中,位于顶层导电层和底层导电层之间的导电层均为内层导电层,

各所述内层导电层均包括若干第二边缘焊盘、若干第二图形引线和若干第二连接焊盘,所述第二连接焊盘通过所述第二图形引线与所述第二边缘焊盘连接,所述第二连接焊盘与对应的所述芯片焊盘单元通过连通孔连接,所述第二边缘焊盘通过所述导通孔与所述底层导电层连接;

16.所述第二边缘焊盘与所述第一边缘焊盘的位置上下错开,所述第二连接焊接与对应的所述芯片焊盘单元上下相对。

17.在一些实施例中,所述底层导电层包括若干第三边缘焊盘,所述第三边缘焊盘与所述第一边缘焊盘或所述第二边缘焊盘通过所述导通孔连接;所述第三边缘焊盘和与自身连接的所述第一边缘焊盘或所述第二边缘焊盘上下相对。

18.在一些实施例中,与所述顶层导电层对应的所述芯片焊盘单元的行位于所述矩阵的最外行。

19.在一些实施例中,还包括阻焊层和导热层;所述阻焊层设置在顶层的隔绝结构层上并覆盖所述隔绝结构层上除所述顶层导电层、所述芯片焊盘单元以外的区域;所述导热层设置在底层的隔绝结构层上。

20.在一些实施例中,所述的基体层的材料为陶瓷材料,包括al2o3陶瓷、aln陶瓷、si3n4陶瓷或beo陶瓷。

21.在一些实施例中,每一所述芯片焊盘单元包括正极焊盘和负极焊盘,所述矩阵划分为若干矩形的功能区,同一功能区内,若干所述芯片焊盘单元依次排列,相邻的两个所述芯片焊盘单元中的一者的正极焊盘,与另一者的负极焊盘连接。

22.一种集成封装器件,包括如上所述的基板,所述集成封装器件还包括若干发光芯片、与所述发光芯片一一对应的光转换层、连接胶层、填充胶和围坝;

23.各所述发光芯片分别与各所述芯片焊盘单元连接;在同一所述功能区中,各所述发光芯片依次相邻设置无空位;

24.所述光转换层通过所述连接胶层固定在所述发光芯片上,所述围坝固定在顶层的所述隔绝结构层上并包围所述矩阵;所述填充胶充满所述围坝内并填充在各所述发光芯片、各光转换层、连接胶层之间的缝隙。

25.与现有技术相比,本实用新型的有益效果为:

26.1、本实用新型的基板中,针对各芯片焊盘单元设置了不同的导电层,将各个图像化的导电层与芯片焊盘单元通过通孔连接,无需连接外部引线,因此,其各芯片焊盘单元的间距可以更加紧密,用于集成封装器件时,发光芯片的间距更小,从而可实现更高像素的集成封装器件,且封装后尺寸结构更小;

27.2、本实用新型的集成封装器件中,采用了以上的基板,芯片焊盘单元的矩阵划分为若干矩形的功能区,同一功能区内,若干所述芯片焊盘单元依次排列,各所述发光芯片依次相邻设置无空位,可实现小间距且不规则矩阵像素封装;减小封装尺寸,简化电路排布,利于下游贴装。

附图说明

28.下面结合附图和具体实施方式对本实用新型的技术作进一步地详细说明:

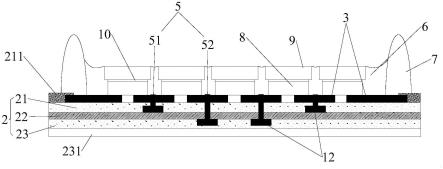

29.图1是本实用新型的集成封装器件的正视图;

30.图2是本实用新型的集成封装器件的剖视图;

31.图3是顶层导电层、芯片焊盘单元在第一绝缘层上的示意图;

32.图4是图3中沿a-a的剖视图;

33.图5是图3中沿b-b的剖视图;

34.图6是图3中e处的芯片焊盘单元的示意图;

35.图7是内层导电层一在基体层的正面上的示意图;

36.图8是图7中沿c-c的剖视图;

37.图9是内层导电层二在基体层的背面上示意图;

38.图10是图9中沿d-d的剖视图;

39.图11是底层导电层在第二绝缘层上的示意图;

40.图12是本实用新型的集成封装器件的制作步骤示意图。

41.附图标记:

42.1-导电层;11-顶层导电层;111-第一边缘焊盘;112-第一图形引线;12-内层导电层;121-内层导电层一;122-内层导电层二;1201-第二边缘焊盘;1202-第二图形引线;1203-第二连接焊盘;13-底层导电层;131-第三边缘焊盘;

43.2-隔绝结构层;21-顶层隔绝结构层;211-阻焊层;22-中层隔绝结构层;23-底层隔绝结构层;231-导热层;201-基体层;202-第一绝缘层;203-第二绝缘层;

44.3-芯片焊盘单元;31-正极焊盘;32-负极焊盘;

45.41-导通孔一;42-导通孔二;43-导通孔三;

46.5-连通孔;51-连导通孔一;52-连导通孔二;

47.6-填充胶;7-围坝;8-发光芯片;9-光转换层;10-连接胶层。

具体实施方式

48.以下将结合实施例和附图对本实用新型的构思、具体结构及产生的技术效果进行清楚、完整的描述,以充分地理解本实用新型的目的、方案和效果。需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。附图中各处使用的相同的附图标记指示相同或相似的部分。

49.需要说明的是,如无特殊说明,当某一特征被称为“固定”、“连接”在另一个特征,它可以直接固定、连接在另一个特征上,也可以间接地固定、连接在另一个特征上。此外,本实用新型中所使用的上、下、左、右等描述仅仅是相对于附图中本实用新型各组成部分的相互位置关系来说的。

50.实施例1:

51.参照图2至图11,一种基板,用于集成封装器件,包括图形化的导电层1、隔绝结构层2和芯片焊盘单元3。

52.参照图4、5、8和10,其中,所述导电层1设有至少三层并叠层排列,即导电层1可以是三层或三层以上。本实施例中,导电层1具有4层,由上到下分别为顶层导电层11、内层导电层一121、内层导电层二122和底层导电层13。

53.参照图2、4、5、8和10,所述隔绝结构层2设有若干层并分别插设在相邻两所述导电层1之间并与导电层1连接固定,从该结构可知,隔绝结构层2的数量比导电层1的数量少一

层,若导电层1的数量为n(n为大于或等于3的自然数),则隔绝结构层2的数量为n-1。具体地,所述隔绝结构层2包括一基体层201和至少一绝缘层。

54.本实施例中,参照图4、5、8和10,导电层1具有4层,则隔绝结构层2共有3层,分别为顶层隔绝结构层21、中层隔绝结构层22和底层隔绝结构层23,其中,中层隔绝结构层22为基体层201,顶层隔绝结构层21和底层隔绝结构层23为绝缘层,分别为第一绝缘层202和第二绝缘层203。内层导电层一121和内层导电层二122分别设置在基体层201的上下两面,第一绝缘层202和第二绝缘层203分别在基体层201的上下两面将内层导电层一121和内层导电层二122覆盖,顶层导电层11位于第一绝缘层202上。

55.参照图3,所述芯片焊盘单元3用于连接发光芯片8,所述芯片焊盘单元3设有若干个并在顶层的隔绝结构层2上排列成矩阵,即在本实施例中,芯片焊盘单元3的矩阵设置在第一绝缘层202上。

56.参照图3,非底层的各导电层1分别与至少一行芯片焊盘单元3对应,且一行芯片焊盘单元3仅对应一导电层1。所述芯片焊盘单元3设有若干类且分别与各所述导电层1对应,各类芯片焊盘单元3均设置在顶层的隔绝结构层2上。从该对应关系可知,芯片焊盘单元3的行分为n-1类,每一类与一层非底层的导电层1对应,每一类具有至少一行,可以是多行。在本实施例中,共有4层导电层,则非底层的导电层1有3层,对应的芯片焊盘单元3的行有3类,每一类有2行,共6行。

57.参照图4、5、8和10,底层导电层13与其上方的各非底层导电层13分别通过导通孔连接,即将各个非底层导电层13都连接到了底层导电层13,可以理解的,由于各个非底层导电层13与底层导电层13的间距不同,各个导通孔的长度也不同,各个导通孔贯通的结构也不相同。在本实施例中,导通孔分别为导通孔一41、导通孔二42、导通孔三43,顶层导电层11通过导通孔一41与底层导电层13连接,内层导电层一121通过导通孔二42与底层导电层13连接,内层导电层二122通过导通孔三43与底层导电层13连接,对应地,导通孔一41贯通顶层隔绝结构层21、中层隔绝结构层22和底层隔绝结构层23,导通孔二42贯通中层隔绝结构层22和底层隔绝结构层23,导通孔三43贯通底层隔绝结构层23。

58.参照图4,顶层导电层11与对应的芯片焊盘单元3连接;参照图5、8和10,非顶层导电层11分别与对应的芯片焊盘单元3通过连通孔5连接。即将各类芯片焊盘单元3分别与各个非底层的导电层1连接,而各个非底层的导电层1均连接到了底层导电层13上,从而各类芯片焊盘单元3都与底层导电层13连接。在本实施例中,共有4层导电层,则非底层的导电层1有3层,对应的芯片焊盘单元3的行有3类,每一类有2行,共6行。其中第1行和第6行为一类,均与顶层导电层11对应连接;第2行和第5行为一类,均与内层导电层一121对应连接;第3行和第4行为一类,均与内层导电层二122对应连接。

59.基于以上的结构,本实用新型的基板中,采用导电层1将设置在顶层隔绝结构层21上的各个芯片焊盘单元3接到最底层的导电层1上,可实现各个芯片焊盘单元3的供电而无需另外焊接外部的引线,在进行集成封装时,发光芯片8可以与芯片焊盘单元3焊接以供电,也无需外接引线,从而可以将各个芯片焊盘单元3的间距、发光芯片8的间距设置的更小、更加紧密,从而可实现更高像素的集成封装器件,且封装后尺寸结构更小。

60.具体地,参照图3至图5,所述顶层导电层11包括若干第一边缘焊盘111和若干第一图形引线112,所述第一图形引线112的一端连接所述第一边缘焊盘111,另一端连接对应的

所述芯片焊盘单元3,所述第一边缘焊盘111通过所述导通孔与所述底层导电层13连接。通过以上的结构,将第一边缘焊盘111与底层导电层13连接在一起。其中,与顶层导电层11对应的一类芯片焊盘单元3有多个,每一个芯片焊盘单元3都对应设有一个第一边缘焊盘111和一条第一图形引线112。在本实施例中,与顶层导电层11对应的一类芯片分为2行,为第1行和第6行,每一行有7个芯片焊盘单元3,共14个,对应的,第一边缘焊盘111设有14个,第一图形引线112也设有14条。各个第一边缘焊盘111设置在顶层隔绝结构层21的外边缘。

61.类似地,参照图7至图10,位于顶层导电层11和底层导电层13之间的导电层1均为内层导电层,各所述内层导电层均包括若干第二边缘焊盘1201、若干第二图形引线1202和若干第二连接焊盘1203,所述第二连接焊盘1203通过所述第二图形引线1202与所述第二边缘焊盘1201连接,所述第二连接焊盘1203与对应的所述芯片焊盘单元3通过连通孔5连接,所述第二边缘焊盘1201通过所述导通孔与所述底层导电层13连接。所述第二边缘焊盘1201与所述第一边缘焊盘111的位置上下错开,以导通孔贯穿时发生相互接触造成短路,所述第二连接焊接与对应的所述芯片焊盘单元3上下相对,以方便与导通孔连接上,无需另外设置引线。即通过以上的结构,将与内层导电层对应的芯片焊盘单元3与底层导电层13连接。

62.在本实施例中,参照图7和图8,内层导电层有2层,分别为内层导电层一121和内层导电层二122,连通孔5分为连导通孔一51和连导通孔二52。第2行和第5行的芯片焊盘单元3为一同类,均与内层导电层一121对应,因此,第2行和第5行的芯片焊盘单元3总共14个,内层导电层一121的第二连接焊盘1203、第二图形引线1202、第二边缘焊盘1201均为17个,第二连接焊盘1203与对应的芯片焊盘单元3通过连导通孔一51连接,第二边缘焊盘1201通过导通孔二42与底层导电层13连接。

63.参照图9和图10,第3行和第4行的芯片焊盘单元3为一同类,均与内层导电层二122对应,因此,第3行和第4行的芯片焊盘单元3总共14个,内层导电层二122的第二连接焊盘1203、第二图形引线1202、第二边缘焊盘1201均为17个,第二连接焊盘1203与对应的芯片焊盘单元3通过连导通孔二52连接,第二边缘焊盘1201通过导通孔三43与底层导电层13连接。

64.可以理解的,各个导电层1为图形化的导电层1,因此,各个边缘焊盘、图形引线也都是图形化的结构,相比于外部引线,占据的体积、空间更小,均附在基体层201上、嵌入绝缘层上或附在绝缘层上。

65.具体地,参照图4、8、10和11,所述底层导电层13包括若干第三边缘焊盘131,所述第三边缘焊盘131与所述第一边缘焊盘111或所述第二边缘焊盘1201通过所述导通孔连接;所述第三边缘焊盘和与自身连接的所述第一边缘焊盘111或所述第二边缘焊盘1201上下相对。底层导电层13与其他导电层1是通过导通孔连接,因此需要上下对正,避免再采用引线连接。在本实施例中,由于芯片焊盘单元3共有42个,第一边缘焊盘111和所述第二边缘焊盘1201的总数也为42个,因此,第三边缘焊盘131也共有42个。

66.在一些实施例中,参照图3,与所述顶层导电层11对应的所述芯片焊盘单元3的行位于所述矩阵的最外行。由于顶层导电层11与芯片焊盘单元3都位于顶层隔绝结构层21上,没有采用导通孔连接,因此,将与顶层导电层11对应的所述芯片焊盘单元3的行设置在所述矩阵的最外行,在最外侧即可以直接与顶层导电层11连接,避免其它的芯片焊盘单元3对二者的连接造成干扰,而增大芯片焊盘单元3的之间的间距。在本实施例中,即使第1行和第6行的芯片焊盘单元3与顶层导电层11对应。

67.优选地,参照图4和图11,本实用新型的基板还包括阻焊层211和导热层231;所述阻焊层211设置在顶层的隔绝结构层2上并覆盖所述隔绝结构层2上除所述顶层导电层11、所述芯片焊盘单元3以外的区域;所述导热层231设置在底层的隔绝结构层2上。阻焊层211的设置,是为了避免后续焊接造成短路。导热层231是为了将基板工作时的产生的热量加快排出,导热层231为金属层。

68.其中,所述的基体层201的材料为陶瓷材料,包括al2o3陶瓷、aln陶瓷、si3n4陶瓷或beo陶瓷。所述导电层1的材料为cu、ni、pd、w、ag、au中的一种或几种。

69.具体地,参照图3和6,每一所述芯片焊盘单元3包括正极焊盘31和负极焊盘32,所述矩阵划分为若干矩形的功能区,同一功能区内,若干所述芯片焊盘单元3依次排列,相邻的两个所述芯片焊盘单元3中的一者的正极焊盘31,与另一者的负极焊盘32连接。在焊接时,将发光芯片8的正负极分别与正极焊盘31和负极焊盘32焊接,在同一功能区内,由于相邻的两个所述芯片焊盘单元3中的一者的正极焊盘31,则焊接后,同一区内的发光单元形成串联。通过各个边缘焊盘连接外部电路进行输入,每个发光芯片8都可以独立进行点亮或一个功能区共同点亮。例如图3中,每一行为一个功能区,该行的每个发光芯片8都可以独立进行点亮或一个功能区共同点亮。也可以将上下相邻的若干行划在一个功能区中,在每行的末端的正极焊盘31或负极焊盘32与下一行的相反电极的焊盘连接在一起。

70.实施例2:

71.参照图1至图11,一种集成封装器件,包括如实施例1所述的基板,所述集成封装器件还包括若干发光芯片8、与所述发光芯片8一一对应的光转换层9、连接胶层10、填充胶6和围坝7。

72.参照图1和图2,各所述发光芯片8分别与各所述芯片焊盘单元3连接;在同一所述功能区中,各所述发光芯片8依次相邻设置无空位,以实现所述功能区中的发光芯片8的串联。通过各个边缘焊盘连接外部电路进行输入,每个发给芯片都可以独立进行点亮或一个功能区共同点亮。

73.所述光转换层9通过所述连接胶层10固定在所述发光芯片8上,所述围坝7固定在顶层的所述隔绝结构层2上并包围所述矩阵;所述填充胶6充满所述围坝7内并填充在各所述发光芯片8、各光转换层9、连接胶层10之间的缝隙。

74.本实用新型的集成封装器件中,采用了实施例1的基板,芯片焊盘单元3的矩阵划分为若干矩形的功能区,同一功能区内,若干所述芯片焊盘单元3依次排列,各所述发光芯片8依次相邻设置无空位,可实现小间距且不规则矩阵像素封装;减小封装尺寸,简化电路排布,利于下游贴装。

75.参照图1至图12,为本集成封装器件的制作方法,采用实施例1所述的基板,包括以下步骤:

76.s1、参照图12,将若干发光芯片8与各所述芯片焊盘单元3焊接,并且在同一所述功能区中,各所述发光芯片8依次相邻设置无空位;

77.s2、参照图12,通过连接胶层10将各光转换层9分别固定在各发光芯片8上;

78.s3、参照图12,采用胶体在顶层的隔绝结构层2上形成包围所述矩阵的围坝7;

79.s4、参照图12,在围坝7内填充填充胶6,使所述填充胶6充满所述围坝7内并填充在各所述发光芯片8、各光转换层9、连接胶层10之间的缝隙。

80.其中,围坝7、连接胶层10和填充胶6都为硅胶。

81.本实用新型的制作方法采用了实施例1的基板,制作过程中无需采用外接引线来焊接发光芯片8,操作更加简单,发光芯片8的间距更小,制成的集成封装器件像素更高,且封装后尺寸结构更小。

82.本实用新型所述的基板和集成封装器件的其它内容参见现有技术,在此不再赘述。

83.以上所述,仅是本实用新型的较佳实施例而已,并非对本实用新型作任何形式上的限制,故凡是未脱离本实用新型技术方案内容,依据本实用新型的技术实质对以上实施例所作的任何修改、等同变化与修饰,均仍属于本实用新型技术方案的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1