一种LDMOSFET、制备方法及芯片和电路与流程

一种ldmosfet、制备方法及芯片和电路

技术领域

1.本发明涉及半导体领域,具体地涉及一种ldmosfet、制备方法及芯片和电路。

背景技术:

2.ldmosfet器件常常被用于各种应用,例如汽车应用中。现有技术中常常通过降低ldmosfet器件中的表面电场(resurf)结构来防止高压施加于漏极造成击穿。但是现有ldmosfet器件的结构是平面结构,在提高击穿电压与减少ldmosfet面积,降低成本之间存在矛盾。

技术实现要素:

3.本发明实施例的目的是提供一种ldmosfet、制备方法及芯片和电路,该ldmosfet不仅有效的缩小了器件的尺寸,还大大提升了器件的性能。

4.为了实现上述目的,本发明实施例提供一种ldmosfet,包括:衬底,所述衬底上设有埋层;所述埋层上方设有外延层;所述外延层上方设有高压p型阱和高压n型阱;所述高压n型阱上方依次设有第一n型漂移区、p型体区和第二n型漂移区,其中,所述第一n型漂移区、p型体区和第二n型漂移区中的至少一者的上表面有凸起。

5.可选的,所述第一n型漂移区和第二n型漂移区在同一横向维度彼此分开。

6.可选的,所述第一n型漂移区呈反l型立体图形,所述p型体区呈凹型立体图形,所述第二n型漂移区呈l型立体图形,三者边缘处相接,共同组成一个新的凹形立体图形。

7.可选的,所述第一n型漂移区的外侧和第二n型漂移区的外侧均设有侧墙;所述侧墙为氧化物,用于隔离。

8.可选的,所述高压p型阱设于所述高压n型阱两侧,且所述高压n型阱的深度大于所述高压p型阱。

9.可选的,所述高压p型阱与所述高压n型阱相接的上侧设有场氧结构;所述场氧结构为凸起形状,用于隔离。

10.可选的,所述第一n型漂移区的深度、p型体区的深度和第二n型漂移区的深度均小于所述高压n型阱的深度。

11.可选的,所述第一n型漂移区和第二n型漂移区的最外层设有多晶硅。

12.可选的,所述衬底为p型衬底。

13.另一方面,本发明提供一种ldmosfet的制备方法,包括:形成衬底,所述衬底上设有埋层;所述埋层上方形成外延层;所述外延层上方形成高压p型阱和高压n型阱;所述高压n型阱上方依次形成第一n型漂移区、p型体区和第二n型漂移区,其中,所述第一n型漂移区、p型体区和第二n型漂移区中的至少一者的上表面有凸起。

14.可选的,所述第一n型漂移区的外侧和第二n型漂移区的外侧均形成侧墙;所述侧墙为氧化物,用于隔离。

15.可选的,所述高压p型阱形成于所述高压n型阱两侧,且所述高压n型阱的深度大于

所述高压p型阱。

16.可选的,所述高压p型阱与所述高压n型阱相接的上侧形成场氧结构;所述场氧结构为凸起形状,用于隔离。

17.另一方面,本发明还提供一种芯片,该芯片包括上述所述的ldmosfet。

18.另一方面,本发明还提供一种电路,该电路包括上述所述的ldmosfet。

19.本发明提供的一种ldmosfet,包括:衬底,所述衬底上设有埋层;所述埋层上方设有外延层;所述外延层上方设有高压p型阱和高压n型阱;所述高压n型阱上方依次设有第一n型漂移区、p型体区和第二n型漂移区,其中,所述第一n型漂移区、p型体区和第二n型漂移区中的至少一者的上表面有凸起。所述ldmosfet通过对第一n型漂移区、p型体区和第二n型漂移区中至少一者进行三维立体设计,缩小了器件的尺寸,增大了击穿电压,减小了表面电场。

20.本发明实施例的其它特征和优点将在随后的具体实施方式部分予以详细说明。

附图说明

21.附图是用来提供对本发明实施例的进一步理解,并且构成说明书的一部分,与下面的具体实施方式一起用于解释本发明实施例,但并不构成对本发明实施例的限制。在附图中:图1-图2是本发明的ldmosfet的制备方法示意图。

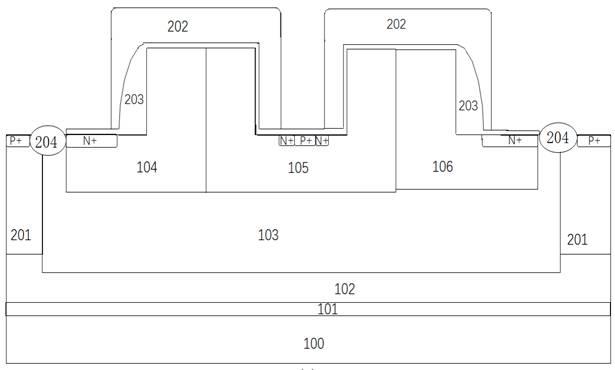

22.附图标记说明100-衬底;101-埋层;102-外延层;103-高压n型阱;104-第一n型漂移区;105-p型体区;106-第二n型漂移区;201-高压p型阱;202-多晶硅;203-侧墙;204-场氧结构。

具体实施方式

23.以下结合附图对本发明实施例的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明实施例,并不用于限制本发明实施例。

24.本发明提供了一种ldmosfet,如图2所示,所述ldmosfet包括:衬底100,所述衬底100优选为p型衬底。所述衬底100上设有埋层101;所述埋层101上方设有外延层102;所述外延层102上方设有高压p型阱201和高压n型阱103;所述高压n型阱103上方依次设有第一n型漂移区104、p型体区105和第二n型漂移区106,其中,所述第一n型漂移区104、p型体区105和第二n型漂移区106中的至少一者的上表面有凸起,如图2所示,所述第一n型漂移区104呈反

l型立体图形,所述p型体区105呈凹型立体图形,所述第二n型漂移区106呈l型立体图形,三者边缘处相接,共同组成一个新的凹形立体图形,所述第一n型漂移区和第二n型漂移区在同一横向维度彼此分开。

25.所述第一n型漂移区104的外侧和第二n型漂移区106的外侧均设有侧墙203,所述侧墙203优选氧化物,具有隔离的作用,有效的减少了器件表面电场。

26.所述高压p型阱201设于所述高压n型阱103两侧,且所述高压n型阱103的深度大于所述高压p型阱201。所述高压p型阱201与所述高压n型阱103相接的上侧设有场氧结构204;所述场氧结构204为凸起形状,用于隔离。

27.所述第一n型漂移区104的深度、p型体区105的深度和第二n型漂移区106的深度均小于所述高压n型阱103的深度,这些漂移区都是在高压n型阱上制作,n型漂移区与p型漂移区可以不同深度所述第一n型漂移区104和第二n型漂移区106的最外层设有多晶硅202。

28.本发明还提供一种ldmosfet的制备方法,包括:形成衬底100,所述衬底100上设有埋层101;所述埋层101上方形成外延层102;所述外延层102上方形成高压p型阱201和高压n型阱103;所述高压n型阱103上方依次形成第一n型漂移区104、p型体区105和第二n型漂移区106,其中,所述第一n型漂移区104、p型体区105和第二n型漂移区106中的至少一者的上表面有凸起。所述第一n型漂移区104的外侧和第二n型漂移区106的外侧均形成侧墙;所述侧墙为氧化物,用于隔离。所述高压p型阱201形成于所述高压n型阱103两侧,且所述高压n型阱103的深度大于所述高压p型阱201。所述高压p型阱201与所述高压n型阱103相接的上侧形成场氧结构204;所述场氧结构204为凸起形状,用于隔离。

29.具体的,图1-图2是本发明的ldmosfet的制备方法示意图。如图1所示,先在p型衬底上制作n+埋层(bl),然后在埋层101添加外延层102(epi),在外延层102上面离子注入,依次形成高压n型阱103(hvnw),高压p型阱201(hvpw),第一n型漂移区104,p型体区105,第二n型漂移区106;然后对第一n型漂移区104、p型体区105、第二n型漂移区106进行3d 沟道区光刻,具体包括涂胶、曝光、显影等,然后干法刻蚀p型体区105和第一n型漂移区104、第二n型漂移区106的部分硅,然后进行去胶清洗。

30.如图2所示,对图1所示的ldmosfet进行其他工艺操作,包括:首先做场氧结构204(locos),具体流程为:衬垫氧化层制作(pad oxide)、lpcvd sin(氮化硅)、光刻、干法刻蚀sin和pad ox(衬垫氧化层)、场氧结构204(locos)氧化,然后湿法去除sin;其次为侧墙203的形成,包括:cvd sio2, 然后干法刻蚀sio2,形成侧墙203;再次光刻,干法刻蚀掉p型体区105(p-body)的侧墙203,形成单边nrf侧墙;然后,栅氧化、gate polysilicon deposition(多晶硅栅淀积)、多晶硅202(poly)扩散掺杂、poly gate(多晶硅栅)光刻、干法刻蚀多晶硅;最后形成源漏离子注入掺杂,形成源漏。

31.本发明的一种ldmosfet,包括:包括:形成衬底100,所述衬底100上设有埋层101;所述埋层101上方形成外延层102;所述外延层102上方形成高压p型阱201和高压n型阱103;所述高压n型阱103上方依次形成第一n型漂移区104、p型体区105和第二n型漂移区106,其中,所述第一n型漂移区104、p型体区105和第二n型漂移区106中的至少一者的上表面有凸起。所述ldmosfet通过对第一n型漂移区、p型体区和第二n型漂移区中至少一者进行三维立体设计,缩小了器件的尺寸,增大了击穿电压,减小了表面电场。

32.以上结合附图详细描述了本发明实施例的可选实施方式,但是,本发明实施例并

不限于上述实施方式中的具体细节,在本发明实施例的技术构思范围内,可以对本发明实施例的技术方案进行多种简单变型,这些简单变型均属于本发明实施例的保护范围。

33.另外需要说明的是,在上述具体实施方式中所描述的各个具体技术特征,在不矛盾的情况下,可以通过任何合适的方式进行组合。为了避免不必要的重复,本发明实施例对各种可能的组合方式不再另行说明。

34.还需要说明的是,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、商品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、商品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括要素的过程、方法、商品或者设备中还存在另外的相同要素。

35.以上仅为本技术的实施例而已,并不用于限制本技术。对于本领域技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本技术的权利要求范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1