一种半导体外延结构及其制备方法与功率及射频器件与流程

1.本发明属于半导体制作技术领域,涉及一种半导体外延结构,尤其涉及一种半导体外延结构及其制备方法与功率及射频器件。

背景技术:

2.氮化镓被认为是继硅之后最重要的半导体材料。氮化镓是一种宽禁带半导体材料,它的光谱覆盖了整个可见光区域,可以制成蓝光和白光发光二极管,用于显示、电视背光和普通照明;可以制成绿光/蓝光发光二极管,和algainp基的红光发光二极管一起,用于全色显示;还可以制成紫外光激光器,用于数据存储。除了优异的光学性能,氮化镓的电学性能也十分出色:氮化镓具有禁带宽度大、高临界击穿电场、高导热性及高电子漂移饱和速度等特性,且具高自发与压电极化效应,在制作外延异质结构可产生高迁移率、高面浓度的二维电子气,基于以上特性可使器件具高电流密度、低导通电阻、高工作频率、高热稳定性及体积小等特点。因此,氮化镓也可以用于微波器件與高功率开关器件等。其中,氮化镓半导体材料的耐受电压能力与电子迁移率是其性能的主要指标。

3.现有技术中,一般水平面式器件工艺掺杂过程中使得在半导体材料表面下形成有一定曲率的杂质扩散结,这种结承受电压的能力往往比没有曲率的理想平行平面结所能承受的电压低很多,这将影响半导体器件最终的工作电压。因此出现了许多提高平面工艺产生的曲率结击穿电压的方法,一般统称为结终端技术。

4.cn 108428741a公开了一种氮化镓半导体器件及其制作方法,该方法包括:在基底的第一表面生长含铟的缓冲层,该缓冲层包括含铟的al

x

ga

1-x

n层,其中,0≤x≤1;在缓冲层背离基底一侧表面形成非有意掺杂的第一氮化镓层;在第一氮化镓层背离缓冲层一侧表面形成含碳掺杂的第二氮化镓层;在第二氮化镓层背离第一氮化镓层一侧形成非有意掺杂的第三氮化镓层;在第三氮化镓层背离第二氮化镓层一侧形成alygan

1-y

n层,其中,0<y≤1。利用该方法制的氮化镓半导体器件可提高所述氮化镓半导体器件的击穿电压,降低所述氮化镓半导体器件在制作过程中,出现裂纹的概率,提高所述氮化镓半导体器件的性能。

5.cn 101330097公开了一种增加击穿电压的半导体结构及制造方法。所述半导体结构包括半导体材料、主扩散结、耐压层、耗尽终止区和介质层共5个部分。其中,主扩散结、耐压层、耗尽终止区都处于半导体材料中,主扩散结和耐压层的导电类型与半导体材料相反,耗尽终止区与半导体材料的导电类型相同。这种结构可以将主扩散结的击穿电压提高25%以上,能够使主扩散结击穿电压达到半导体材料理想平行平面结最大雪崩击穿电压75%以上。该发明可以应用于数十伏到数千伏的半导体器件结终端中,特别适合浅结低温工艺的高压半导体器件和集成电路的结构及制造。

6.以上技术方案中虽然改进了半导体结构,并且提高了耐受电压,但是存在衬底与顶部的飘移层之间因晶格常数失配率与热膨胀系数差异所引起的外延晶体质量问题,从而影响半导体器件的性能。

7.因此,如何改善衬底与顶部的飘移层之间因晶格常数失配率与热膨胀系数差异所

引起的外延晶体质量问题,保障高的耐受电压能力与电子迁移率,并提升半导体器件的性能,是半导体制造技术领域亟需解决的技术问题。

技术实现要素:

8.鉴于现有技术中存在的问题,本发明提供了一种半导体外延结构及其制备方法与功率及射频器件,通过生长一层应力调节层在缓冲层上,减缓了衬底与飘移层之间因晶格常数失配率与热膨胀系数差异所引起的外延晶体质量问题,从而提升了器件能力。

9.为达此目的,本发明采用以下技术方案:

10.第一方面,本发明提供了一种半导体外延结构,所述半导体外延结构包括层叠设置的衬底、缓冲层、应力调节层和飘移层;

11.所述应力调节层包括半导体材料和掺杂材料;

12.所述半导体材料包括aln、gan、al

x

ga

1-x

n或inbalaga

1-a-b

n中的任意一种或至少两种的组合,其中0<x<1,0<a<1,0<b<1。

13.本发明通过在缓冲层和飘移层之间生长一层应力调节层,所述应力调节层中含有半导体材料并添加掺杂材料,使得衬底与缓冲层间因差异晶格常数与热膨胀系数不同而产生的螺旋型与刀刃型位错,利用应力调节层调节外延层呈現应变张力效应,以致位错缓减与倾斜转移,並使後續成長飘移层内的位错减少,进而提升氮化鎵基外延晶体品质。

14.所述半导体材料包括aln、gan、al

x

ga

1-x

n或inbalaga

1-a-b

n中的任意一种或至少两种的组合,典型但非限制性的组合包括aln和gan的组合,gan和al

x

ga

1-x

n的组合,al

x

ga

1-x

n和inbalaga

1-a-b

n的组合,aln、gan和al

x

ga

1-x

n的组合,gan、al

x

ga

1-x

n和inbalaga

1-a-b

n的组合,或aln、gan和al

x

ga

1-x

n或inbalaga

1-a-b

n的组合。

15.0<x<1,例如可以是0.01、0.03、0.05、0.1、0.3、0.5、0.7或0.9,但不限于所列举的数值,数值范围内其它未列举的数值同样适用,其数值范围可从大至小或从小至大,优选为从大至小。

16.0<a<1,例如可以是0.01、0.03、0.05、0.1、0.3、0.5、0.7或0.9,例如可以是,但不限于所列举的数值,数值范围内其它未列举的数值同样适用,其数值范围可从大至小或从小至大,但优选为从大至小。

17.0<b<1,例如可以是0.01、0.03、0.05、0.1、0.3、0.5、0.7或0.9,例如可以是,但不限于所列举的数值,数值范围内其它未列举的数值同样适用,其数值范围可从大至小或从小至大,但优选为从小至大。

18.优选地,所述应力调节层包括单层结构或复合层结构。

19.优选地,所述单层结构中半导体材料包括aln、gan、al

x

ga

1-x

n或inbalaga

1-a-b

n中的任意一种。

20.优选地,所述复合层结构包括至少两层,例如可以是2层、4层、10层、40层或50层,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

21.优选地,所述复合层结构中每相邻两层呈周期性层叠。

22.优选地,所述相邻两层中的半导体材料包括aln、gan、al

x

ga

1-x

n或inbalaga

1-a-b

n中任意两种的组合,例如可以是aln和gan的组合,gan和al

x

ga

1-x

n的组合,al

x

ga

1-x

n和inbalaga

1-a-b

n的组合,aln和al

x

ga

1-x

n的组合,aln和inbalaga

1-a-b

n的组合,或gan和

inbalaga

1-a-b

n的组合。

23.优选地,所述周期的个数为1~100,例如可以是1、5、10、40、50、60、80或100,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

24.本发明提供的应力调节层的复合层结构,以每两层为单元以周期性层叠的方式分布,每层中仅有一种半导体材料,相邻两层的半导体材料不同。利用调试不同的外延生长条件,在应力调节层上调制出不同材料组分及其相对应的晶格常数,最后在此层可调制出符合下一层的外延晶格常数。

25.优选地,所述掺杂材料中的掺杂元素包括碳、铍、镁或铁中的任意一种或至少两种的组合,典型但非限制性的组合包括碳和铍的组合,铍和镁的组合,镁和铁的组合,碳和镁的组合,碳和铁的组合,铍和铁的组合,碳、铍和镁的组合,铍、镁和铁的组合,或碳、铍、镁和铁的组合。

26.本发明利用在应力调节层中掺杂不同元素的杂质来补偿非故意掺杂n型材料层,以及利用杂志深层能级捕捉方式,使此层呈中性材料,最终达到高阻值特性,此高阻值层来可以减少漏电路径。

27.优选地,所述掺杂元素在应力调节层中的含量为1.0

×

e17~1.0

×

e19atoms/cm3,例如可以是1.0

×

e17atoms/cm3、5.0

×

e17atoms/cm3、1.0

×

e18atoms/cm3、5.0

×

e18atoms/cm3或1.0

×

e19atoms/cm3,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

28.当掺杂浓度大于1.0

×

e19atoms/cm3时,由于掺杂过量,使单晶晶体材料呈现晶体崩塌,产生更多位错;但当掺杂浓度小于1.0

×

e17atoms/cm3时,由于无法形成n型材料补偿与深层能级电子捕捉动作,产生此层出现重大漏电路径进而影响器件操作功能。

29.优选地,所述衬底包括al2o3、gan、aln、gao、si或sic中的任意一种或至少两种的组合,典型但非限制性的组合包括al2o3和gan的组合,gan和aln的组合,aln和si的组合,al2o3和gao的组合,aln和gao的组合,gao和si的组合,si和sic的组合,al2o3、gan和aln的组合,gan、aln和si的组合,aln、si和sic的组合,al2o3、gan、aln和si的组合,gan、aln、si和sic的组合,或al2o3、gan、aln、si和sic的组合。

30.优选地,所述缓冲层的材料包括aln和/或alinn。

31.优选地,所述飘移层包括aln、gan、algan或alingan中的任意一种或至少两种的组合,典型但非限制性的组合包括aln和gan的组合,gan和algan的组合,gan和alingan的组合,aln和algan的组合,algan和alingan的组合,aln和alingan的组合,aln、gan和algan的组合,gan、algan和alingan的组合,aln、gan和alingan的组合,或aln、algan和alingan的组合。

32.优选地,衬底的厚度为350μm以上,例如可以是350μm、400μm、450μm、500μm或600μm,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

33.优选地,所述缓冲层的厚度为1~500nm,例如可以是1nm、50nm、100nm、300nm或500nm,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

34.优选地,所述应力调节层的厚度为0.1~50μm,例如可以是0.1μm、1μm、5μm、10μm、15μm、20μm、30μm、40μm或50μm,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

35.优选地,所述飘移层的厚度为1~50μm,例如可以是1μm、5μm、10μm、15μm、20μm、30μm、40μm或50μm,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

36.第二方面,本发明提供了一种根据第一方面所述半导体外延结构的制备方法,所述制备方法包括如下步骤:

37.(1)在衬底的表面生长缓冲层;

38.(2)在所得缓冲层的表面生长应力调节层;

39.(3)在所得应力调节层表面生长飘移层。

40.本发明所述生长为气相外延生长的方法。

41.优选地,步骤(1)所述生长的温度为500~1100℃,例如可以是500℃、600℃、700℃、800℃、900℃、1000℃或1100℃,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

42.优选地,步骤(1)所述生长的反应腔体压力为20~500torr,例如可以是20torr、50torr、100torr、200torr或500torr,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

43.优选地,步骤(1)所述生长的tmal流量为200~300slm,例如可以是200slm、210slm、220slm、250slm、280slm或300slm,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

44.优选地,步骤(1)所述生长在通入氨气的条件下进行,流量为0.5~50slm,例如可以是0.5slm、1slm、5slm、10slm、25slm或50slm,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

45.优选地,步骤(2)所述生长的温度为500~1100℃,例如可以是500℃、600℃、700℃、800℃、900℃、1000℃或1100℃,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

46.优选地,步骤(2)所述生长的反应腔压力为20~500torr,例如可以是20torr、50torr、100torr、200torr或500torr,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

47.优选地,步骤(2)所述生长的tmal流量为10~250slm,例如可以是10slm、50slm、100slm、200slm、220slm或250slm,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

48.优选地,步骤(2)所述生长在通入氨气的条件下进行,流量为0.5~50slm,例如可以是0.5slm、1slm、5slm、10slm、25slm或50slm,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

49.优选地,步骤(3)所述生长的温度为500~1100℃,例如可以是500℃、600℃、700℃、800℃、900℃、1000℃或1100℃,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

50.优选地,步骤(3)所述生长的反应腔压力为20~500torr,例如可以是20torr、50torr、100torr、200torr或500torr,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

51.优选地,步骤(3)所述生长的tmal流量为10~300slm,例如可以是10slm、50slm、

100slm、200slm、220slm、250slm、280slm或300slm,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

52.优选地,步骤(3)所述生长在通入氨气的条件下进行,流量为0.5~100slm,例如可以是0.5slm、1slm、5slm、10slm、25slm、50slm、80slm或100slm,但不限于所列举的数值,数值范围内其它未列举的数值同样适用。

53.作为本发明第二方面所述制备方法的一种优选技术方案,所述制备方法包括如下步骤:

54.(1)在温度为500~1100℃,反应腔压力为20~500torr,tmal流量为200~300slm的条件下,通入流量为0.5~50slm的氨气,在衬底的表面生长缓冲层;

55.(2)在温度为500~1100℃,反应腔压力为20~500torr,tmal流量为10-250slm的条件下,通入流量为0.5~50slm的氨气,在所得缓冲层的表面生长应力调节层;

56.(3)在温度500~1100℃,反应腔压力为20~500torr,tmal流量为10~300slm的条件下,通入流量为0.5~100slm的氨气,在所得应力调节层表面生长飘移层。

57.第三方面,本发明提供了一种功率器件,所述功率器件含有如第一方面所述的半导体外延结构。

58.第四方面,本发明提供了一种射频器件,所述射频器件含有如第一方面所述的半导体外延结构。

59.由以上技术方案,本发明的有益效果如下:

60.本发明通过在缓冲层和飘移层之间生长一层应力调节层,所述应力调节层中含有半导体材料,并且添加掺杂材料,使得缓冲层与飘移层间因差异晶格常数与热膨胀系数不同而产生的螺旋型与刀刃型位错,经由应力调节层将其位错缓减与倾斜,使得在飘移层内的位错减缓,进而提升了晶体的品质,从而提高了半导体材料的耐电压能力。

附图说明

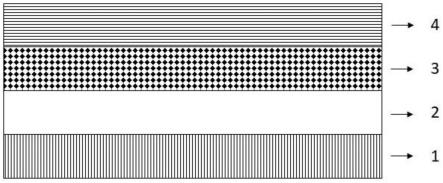

61.图1是实施例1-3所述半导体外延结构的结构示意图。

62.图2是实施例4所述半导体外延结构的结构示意图。

63.其中,1-衬底,2-缓冲层,3-单层结构的应力调节层,4-飘移层,5-复合层结构的应力调节层。

具体实施方式

64.下面结合附图并通过具体实施方式来进一步说明本发明的技术方案。但下述的实例仅仅是本发明的简易例子,并不代表或限制本发明的权利保护范围,本发明的保护范围以权利要求书为准。

65.实施例1

66.本实施例提供了一种半导体外延结构(图1),所述半导体外延结构包括层叠设置的衬底1、缓冲层2、应力调节层3和飘移层4。

67.所述衬底1的材料为al2o3,厚度为350μm。

68.所述缓冲层2的材料为aln,厚度为250nm。

69.所述应力调节层3为单层结构,所述单层结构由半导体材料aln和掺杂材料组成,

掺杂元素mg在所述应力调节层3中的掺杂浓度为1.0

×

e18atoms/cm3,所述应力调节层3的厚度为2μm。

70.所述飘移层4的材料包括algan,厚度为25μm。

71.所述半导体外延结构的制备方法包括如下步骤:

72.(1)在温度为800℃,反应腔压力为260torr,tmal流量为250slm的条件下,通入流量为25slm的氨气,在衬底1的表面生长缓冲层2;

73.(2)在温度为800℃,反应腔压力为260torr,tmal流量为130slm的条件下,通入流量为25slm的氨气,在所得缓冲层2的表面生长应力调节层3;

74.(3)在温度为800℃,反应腔压力为260torr,tmal流量为150slm的条件下,通入流量为50slm的氨气,在所得应力调节层3表面生长飘移层4。

75.实施例2

76.本实施例提供了一种半导体外延结构(图1),所述半导体外延结构包括层叠设置的衬底1、缓冲层2、应力调节层3和飘移层4。

77.所述衬底1的材料为gan,厚度为400μm。

78.所述缓冲层2的材料为aln,厚度为1nm。

79.所述应力调节层3为单层结构,所述单层结构由半导体材料al

0.6

ga

0.4

n和掺杂材料组成fe6n2,掺杂元素fe在所述应力调节层3中的掺杂浓度为1.0

×

e17atoms/cm3,所述应力调节层3的厚度为0.1μm。

80.所述飘移层4的材料包括alinn,厚度为1μm。

81.所述半导体外延结构的制备方法包括如下步骤:

82.(1)在温度为500℃,反应腔压力为500torr,tmal流量为300slm的条件下,通入流量为50slm的氨气,在衬底1的表面生长缓冲层2;

83.(2)在温度为500℃,反应腔压力为500torr,tmal流量为250slm的条件下,通入流量为50slm的氨气,在所得缓冲层2的表面生长应力调节层3;

84.(3)在温度为500℃,反应腔压力为20torr,tmal流量为10slm的条件下,通入流量为0.5slm的氨气,在所得应力调节层3表面生长飘移层4。

85.实施例3

86.本实施例提供了一种半导体外延结构(图1),所述半导体外延结构包括层叠设置的衬底1、缓冲层2、应力调节层3和飘移层4。

87.所述衬底1的材料为si,厚度为500μm。

88.所述缓冲层2的材料为aln,厚度为500nm。

89.所述应力调节层3为单层结构,所述单层结构由半导体材料in

0.3

al

0.3

ga

0.4

n和掺杂材料组成be3n2,掺杂元素be在所述应力调节层3中的掺杂浓度为1.0

×

e19atoms/cm3,所述应力调节层3的厚度为50μm。

90.所述飘移层4的材料包括alingan,厚度为50μm。

91.所述半导体外延结构的制备方法包括如下步骤:

92.(1)在温度为1100℃,反应腔压力为20torr,tmal流量为200slm的条件下,通入流量为0.5slm的氨气,在衬底1的表面生长缓冲层2;

93.(2)在温度为1100℃,反应腔压力为20torr,tmal流量为250slm的条件下,通入流

量为0.5slm的氨气,在所得缓冲层2的表面生长应力调节层3;

94.(3)在温度为1100℃,反应腔压力为500torr,tmal流量为300slm的条件下,通入流量为100slm的氨气,在所得应力调节层3表面生长飘移层4。

95.实施例4

96.本实施例提供了一种半导体外延结构(图2),所述半导体外延结构包括层叠设置的衬底1、缓冲层2、应力调节层5和飘移层4。

97.所述衬底1的材料为sic,厚度为350μm。

98.所述缓冲层2的材料为aln,厚度为300nm。

99.所述应力调节层5为复合层结构,所述复合层结构中每相邻两层呈周期性层叠,周期的个数为2,相邻两层中一层是由半导体材料aln和掺杂材料mg3n2组成,另一层是由半导体材料al

0.7

ga

0.3

n和掺杂材料mg3n2所组成,掺杂元素mg在所述应力调节层5中的掺杂浓度为1.0

×

e18atoms/cm3,所述应力调节层5的厚度为2μm。

100.所述飘移层4的材料包括algan,厚度为25μm。

101.所述半导体外延结构的制备方法包括如下步骤:

102.(1)在温度为800℃,反应腔压力为260torr,tmal流量为250slm的条件下,通入流量为25slm的氨气,在衬底1的表面生长缓冲层2;

103.(2)在温度为800℃,反应腔压力为260torr,tmal流量为130slm的条件下,通入流量为25slm的氨气,在所得缓冲层2的表面生长应力调节层5;

104.(3)在温度为800℃,反应腔压力为260torr,tmal流量为150slm的条件下,通入流量为50slm的氨气,在所得应力调节层5表面生长飘移层4。

105.实施例5

106.本实施例提供了一种半导体外延结构,所述半导体外延结构包括层叠设置的衬底、缓冲层、应力调节层和飘移层。

107.所述衬底的材料为aln,厚度为400μm。

108.所述缓冲层的材料为aln,厚度为1nm。

109.所述应力调节层为复合层结构,所述复合层结构中每相邻两层呈周期性层叠,周期的个数为1,相邻两层中的一层是由半导体材料gan和掺杂材料cbr4组成,另一层是由半导体材料al

0.7

ga

0.3

n和掺杂材料石墨所组成,掺杂元素c在所述应力调节层中的掺杂浓度为1.0

×

e17atoms/cm3,所述应力调节层的厚度为0.1μm。

110.所述飘移层的材料包括aln,厚度为1μm。

111.所述半导体外延结构的制备方法包括如下步骤:

112.(1)在温度为500℃,反应腔压力为500torr,tmal流量为300slm的条件下,通入流量为50slm的氨气,在衬底的表面生长缓冲层;

113.(2)在温度为500℃,反应腔压力为500torr,tmal流量为250slm的条件下,通入流量为50slm的氨气,在所得缓冲层的表面生长应力调节层;

114.(3)在温度为500℃,反应腔压力为20torr,tmal流量为10slm的条件下,通入流量为0.5slm的氨气,在所得应力调节层5表面生长飘移层4。

115.实施例6

116.本实施例提供了一种半导体外延结构,所述半导体外延结构包括层叠设置的衬

底、缓冲层、应力调节层和飘移层。

117.所述衬底的材料为si,厚度为350μm。

118.所述缓冲层的材料为aln,厚度为500nm。

119.所述应力调节层为复合层结构,所述复合层结构中每相邻两层呈周期性层叠,周期的个数为100,相邻两层中的一层是由半导体材料in

0.3

al

0.3

ga

0.4

n和掺杂材料be3n2组成,另一层是由半导体材料al

0.7

ga

0.3

n和掺杂材料be3n2所组成,掺杂元素be在所述应力调节层中的掺杂浓度为1.0

×

e19atoms/cm3,所述应力调节层的厚度为50μm。

120.所述飘移层的材料包括alingan,厚度为50μm。

121.所述半导体外延结构的制备方法包括如下步骤:

122.(1)在温度为1100℃,反应腔压力为20torr,tmal流量为200slm的条件下,通入流量为0.5slm的氨气,在衬底的表面生长缓冲层;

123.(2)在温度为1100℃,反应腔压力为20torr,tmal流量为250slm的条件下,通入流量为0.5slm的氨气,在所得缓冲层的表面生长应力调节层;

124.(3)在温度为1100℃,反应腔压力为500torr,tmal流量为300slm的条件下,通入流量为100slm的氨气,在所得应力调节层5表面生长飘移层4。

125.实施例7

126.本实施例提供了一种半导体外延结构,除掺杂元素mg在所述应力调节层中的掺杂浓度为8.0

×

e16atoms/cm3外,其余组成含量、工艺参数与实施例1相同。

127.实施例8

128.本实施例提供了一种半导体外延结构,除掺杂元素mg在所述应力调节层中的掺杂浓度为1.2

×

e19atoms/cm3外,其余组成含量、工艺参数与实施例1相同。

129.实施例9

130.本实施例提供了一种半导体外延结构,除所述应力调节层的厚度为80nm外,其余组成含量、工艺参数与实施例1相同。

131.实施例10

132.本实施例提供了一种半导体外延结构,除所述应力调节层的厚度为52μm外,其余组成含量、工艺参数与实施例1相同。

133.实施例11

134.本实施例提供了一种半导体外延结构,除掺杂材料mg3n2替换为等掺杂浓度的ca3n2外,其余组成含量、工艺参数与实施例1相同。

135.实施例12

136.本实施例提供了一种半导体外延结构,除掺杂材料mg3n2替换为等掺杂浓度的con外,其余组成含量、工艺参数与实施例2相同。

137.实施例13

138.本实施例提供了一种半导体外延结构,除掺杂材料石墨替换为等掺杂浓度的si外,其余组成含量、工艺参数与实施例5相同。

139.实施例14

140.本实施例提供了一种半导体外延结构,除所述周期的个数为120外,其余组成含量、工艺参数与实施例4相同。

141.对比例1

142.本对比例提供了一种半导体外延结构,除无应力调节层,制备方法中无步骤(2)外,其余组成含量、工艺步骤与实施例1相同。

143.对比例2

144.本对比例提供了一种半导体外延结构,除应力调节层中无掺杂材料外,其余组成含量、工艺步骤与实施例1相同。

145.从上述半导体外延结构可以得到如下结论:

146.(1)由实施例1-6可知,本发明通过在缓冲层和飘移层之间生长一层应力调节层,所述应力调节层中含有半导体材料并添加掺杂材料,使得缓冲层与飘移层间因差异晶格常数与热膨胀系数不同而产生的螺旋型与刀刃型位错,经由应力调节层将其位错缓减与倾斜,使得在飘移层内的位错减缓,进而提升了晶体的品质,从而提高了半导体材料的耐电压能力。

147.(2)由实施例7、8与实施例1的比较可知,当掺杂浓度不在1.0

×

e17~1.0

×

e19atoms/cm3时,所得半导体外延结构的耐受电压降低,电子迁移率降低,晶体品质差。

148.(3)由实施例9、10与实施例1的比较可知,当应力调节层的厚度不在0.1~50μm的范围内,所得半导体外延结构的耐受电压降低,电子迁移率降低,晶体品质差。

149.(4)由实施例11-13与实施例1的比较可知,当掺杂元素不为本发明提供的碳、铍、镁或铁时,所得半导体外延结构的耐受电压降低,电子迁移率降低,晶体品质差。

150.(5)由实施例14与实施例1的比较可知,当复合层结构的周期不在1-100时,所得半导体外延结构的耐受电压降低,电子迁移率降低,晶体品质差。

151.(6)由对比例1、2与实施例1的比较可知,当无应力调节层或者不进行掺杂时,所得半导体外延结构的耐受电压降低,电子迁移率降低,晶体品质差。

152.综上所述,本发明通过在缓冲层和飘移层之间生长一层应力调节层,所述应力调节层中含有半导体材料并添加掺杂材料,使得缓冲层与飘移层间因差异晶格常数与热膨胀系数不同而产生的螺旋型与刀刃型位错,经由应力调节层将其位错缓减与倾斜,使得在飘移层内的位错减缓,进而提升了晶体的品质,从而提高了半导体材料的耐电压能力。

153.本发明通过上述实施例来说明本发明的详细结构特征,但本发明并不局限于上述详细结构特征,即不意味着本发明必须依赖上述详细结构特征才能实施。所属技术领域的技术人员应该明了,对本发明的任何改进,对本发明所选用部件的等效替换以及辅助部件的增加、具体方式的选择等,均落在本发明的保护范围和公开范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1