具有状态机控制器的时钟恢复设备的制作方法

具有状态机控制器的时钟恢复设备

[0001]

相关申请的交叉引用

[0002]

本申请依照35usc 119(e)的规定要求2018年6月26日提交的美国临时申请62/689855号的权益,该临时申请的内容以引用方式并入本文。

技术领域

[0003]

本发明涉及分组网络中、例如实现由以下标准描述的精密时间协议(ptp)的网络中的精密时钟恢复的领域:ieee网络测量和控制系统精密时钟同步协议标准(ieee standard for a precision clock synchronization protocol for networked measurement and control systems),ieee标准1588tm-2008,2008年7月24日(下文称为1588),该标准的内容以引用方式并入本文。本发明特别涉及用于通过异步网络从传入分组流恢复频率和定时信息的时钟恢复设备。本发明适用于以太网,但也可应用于其他网络,诸如互联网协议(ip)网络。本发明特别适用于如标题为“具有可切换瞬态非线性相位调整器的时钟恢复设备(clock recovery device with switchable transient non-linear phase adjuster)”的美国专利公布2018/0091291号中所述的时钟恢复设备,该专利公布的内容以引用方式并入本文。

背景技术:

[0004]

在需要极高精度的情况下,诸如在先进控制或蜂窝通信系统中,使用ptp来使主时钟与从时钟同步。在存在多个潜在主时钟的情况下,最佳主时钟算法可基于预定要求来选择最佳时钟以用作主时钟。所选择的时钟被称为最高级主时钟。

[0005]

如上文引用的ieee 1588标准中所述,ptp利用带时间戳的同步分组通过网络将定时信息输送到接收器,在此使用驱动数字控制式振荡器的锁相回路来恢复物理时钟信号。示例性现有技术ptp时钟恢复系统在2010年3月30日公布的美国专利7689854号中有所描述,该专利的内容以引用方式并入本文。赫斯曼(hirschmann)白皮书中提供了更多细节,该白皮书标题为精密时钟同步(precision clock synchronization)

–

ieee 1588标准,1.2版,可得自德克萨斯州艾迪生的工业联网解决方案公司(industrial networking solutions,addison,texas)。

[0006]

通常在网络之间的边界处发生时钟恢复。itu建议g.8273.2描述了对边界时钟的要求。现有技术时钟恢复设备可能无法满足上述itu建议对于在用作边界时钟时减小残留相位误差的能力的极其严格的要求。具体地讲,由于时间传输层的性质和格式,不可能在网络同步应用中使用常规锁相回路(pll)架构。任何总体解决方案均应旨在满足以下方面的某些限制:

[0007]

·

初始频率和相位锁定间隔

[0008]

·

频率锁定声明之后的频率误差

[0009]

·

频率锁定声明之后的频率漂移

[0010]

·

相位锁定声明之后的相位误差

[0011]

·

与计算间隔相关的mtie(最大时间间隔误差)

[0012]

·

与计算间隔相关的tdev(时间偏差)

[0013]

·

保持性能和进入/退出标准

[0014]

除了满足这些限制之外,该解决方案还应旨在足够灵活以支持以下系统要求:

[0015]

·

具有给定频率偏移的服务器的热启动

[0016]

·

从频率/相位跳变的容错和恢复

[0017]

·

从网络停机时间场景的容错和恢复

[0018]

·

基准丢失的短暂缓解

[0019]

·

激活/监视服务器频率和相位锁定声明

[0020]

·

激活和监视服务器基准之间的基准切换(基准在这种情况下表示ptp基准)

[0021]

·

激活和监视服务器基准之间的模式切换(基准在这种情况下表示ptp基准,服务器可具有不同操作模式)

[0022]

·

ptp服务器和电频率/相位源之间的模式切换

技术实现要素:

[0023]

本发明的实施方案提供了实现状态机的控制器,该状态机提供不同系统条件之间的无缝转变,同时保持所需的时钟极限。在一个实施方案中,状态机架构控制正常pll锁定、步进时间操作、监测、保持及快速相位和频率锁定之间的转变。具体地讲,状态控制器在已知的1588服务器相位和频率状态之间转变,以便促进常规pll架构用于提供g.8273.1、g.8273.2和/或g.8273.3等级时钟以实现全面路径支持1588同步。本发明的实施方案以根据本发明的时钟恢复设备所服务的主节点与服务器节点之间的大时间偏移来执行超快锁定。

[0024]

根据本发明的实施方案的状态机控制器(其响应于ptp输入流的变化而将pll块置于特定状态)的使用允许常规ii型pll的使用。如本文所定义的ii型pll具有回路滤波器,其中向两个路径的输入施加pll相位差,对这两个路径的输出求和以便为数控振荡器(nco)或数字控制式振荡器(dco)提供控制输入。第一路径是向低通滤波器的输出施加比例因子的比例路径,并且第二路径包含对pll输入相位差进行操作的积分器。ii型pll的使用在降低的复杂性和与零输入相位相对应的最终固定频率偏移方面具有相当大的优势。

[0025]

根据本发明,提供了用于通过异步分组网络从传入分组流恢复频率和定时信息的时钟恢复设备,该时钟恢复设备包括具有多个预定义状态的锁相回路(pll)块,所述pll块包括ii型pll,所述状态中的一个状态包括ii型pll操作;用于响应于传入分组流的变化来控制所述预定义状态之间的转变的状态机控制器;以及对所述pll块作出响应以生成输出信号的受控振荡器。

[0026]

根据本发明的实施方案,全面路径支持边界时钟需要最小分组滤波,相位界面块可用于使用“同步和延迟请求”(sync and delayreq)时间戳按如下方式计算与主节点的偏移:

[0027]

<offsetfrommaster>=<synceventingresstimestamp>-<origintimestamp>-<meanpathdelay>,并且日历函数(包括步进时间(steptime)函数)可用于在pll开始锁定操作之前使时间/相位信息在可编程阈值内对准。

[0028]

本发明的实施方案允许使用针对极大初始相位偏移(由48位表示)的超快收敛及并行频率收敛的多级pll,并且允许去除反馈路径中的局部相位不连续性而不影响闭环频率传递函数。

[0029]

根据本发明的另一个方面,提供了通过异步分组网络从传入分组流恢复频率和定时信息的计算机实现的方法,该计算机实现的方法包括以下步骤:提供具有多个预定义状态的锁相回路(pll)块,所述pll块包括ii型pll,所述状态中的一个状态包括ii型pll操作;响应于传入分组流的变化来控制所述预定义状态之间的转变;以及响应于所述pll块而用受控振荡器生成输出信号。

附图说明

[0030]

现在将参照附图仅以举例的方式更详细描述本发明,在附图中:

[0031]

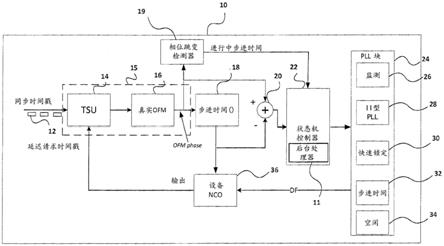

图1是根据本发明的一个实施方案的结合状态机控制器的时钟恢复设备的顶层系统图;

[0032]

图2是示出时钟恢复设备的顶层状态的示意图;

[0033]

图3是示出空闲状态转变控制的示意图;

[0034]

图4是示出步进时间状态控制的示意图;

[0035]

图5是示出强制快速锁定状态控制的示意图;

[0036]

图6是示出快速锁定状态控制的示意图;

[0037]

图7是示出正常状态控制的示意图;

[0038]

图8是示出监测状态控制的示意图;

[0039]

图9是如现有技术已知的示例性ii型pll的框图;

[0040]

图10是示出采用1.2ppm和2.343s初始频率和时间偏移的85mhz pll时的相位和频率锁定时间的tie(时间间隔误差)图;

[0041]

图11是示出采用9.2ppm和1.743s初始频率和时间偏移的85mhz pll时的相位和频率锁定时间的tie图;

[0042]

图12是示出对时间作图的主节点和从节点之间的期望相位收敛的曲线图;并且

[0043]

图13示出了快速锁定状态的频率响应。

具体实施方式

[0044]

作为非限制性示例,图1所示的时钟恢复设备10可实现ieee网络测量和控制系统精密时钟同步协议标准(ieee standard for a precision clock synchronization protocol for networked measurement and control systems),ieee标准1588tm-2008,2008年7月24日。该协议允许通过异步分组网络恢复定时和频率信息,如本领域所熟知。

[0045]

用作从时钟的时钟恢复设备10在相位界面块15中的时间戳单元(tsu)14的输入处从远程主时钟(未示出)接收被表示为sync timestamp的带时间戳的传入分组流12,该相位界面块包括时间戳单元(tsu)14和真实ofm(与主节点的偏移)块16。tsu 14还创建被表示为delreq timestamp的延迟请求分组,这些延迟请求分组基于数控振荡器(nco)36的输出来打上时间戳,该nco 36生成时钟恢复设备10的输出。

[0046]

真实ofm块16使用synceventingress timestamp和delreq timestamp时间戳按如

下方式计算与主节点的偏移(ofm相位):

[0047]

<offsetfrommaster>=<synceventingresstimestamp>-<origintimestamp>-<meanpathdelay>,

[0048]

其中synceventingresstimestamp是向到达的分组施加的时间戳,并且meanpathdelay是根据由主节点返回的delreq timestamps获得的。

[0049]

将真实ofm块16的输出相位ofm phase馈送到步进时间()块18。将时间/相位信息存储在nco 36中,该时间/相位信息确定nco 36的电流输出或使使用专用相位偏移寄存器的相关联的硬件的输出相位移位。是否移位的选择依赖于硬件。在pll块24开始锁定操作之前,步进时间()块18将所存储的时间/相位信息置于与ofm块16的输出相关的可编程阈值偏移值内。进一步将真实ofm块16的输出馈送到加法器20的加输入,该加法器的输出向状态机控制器22提供输入,该状态机控制器可以以适当编程的处理器形式实现。

[0050]

还将真实ofm块16的输出输入到相位跳变检测器19,当传入激活ptp流中的所检测的相位跳变超过可编程步进时间阈值时,该相位跳变检测器将“进行中步进时间”(steptimeinprogress)标志断言为真。“进行中步进时间”标志用作状态机输入,如图1和图5至图7所示。

[0051]

将步进时间()块18的输出馈送到nco 36的输入并馈送到加法器20的减输入。由状态机控制器22的输出(未示出)控制步进时间()块18。

[0052]

状态机控制器22确定pll块24的状态。状态机控制器22还包括后台处理器11,该后台处理器执行整个本说明书中提及的多个后台任务。

[0053]

pll块24包括ii型pll 28,但也根据其状态执行待描述的多个其他不同功能。pll块24的输出将频率差df作为控制输入提供给nco 36。

[0054]

为了理解本发明,知道pll块24可处于多个不同状态就足够了,每个所述状态可能都是本领域已知的。美高森美公司(microsemi corporation)于2016年12月公布的美高森美(microsemi)应用指南zlan-632“监测备用ptp连接(monitoring standby ptp connections)”中详细描述了监测状态26,该应用指南的内容以引用方式并入本文。在监测状态26中,如本领域所知,启用固定100mhz滤波器带宽预测开环df估计模式/滤波。

[0055]

在ii型pll状态28中,pll块24充当典型ii型pll,通常为数字pll(dpll)。示例性ii型pll在图9中示出并且包括相位比较器84和低通回路滤波器86,该低通回路滤波器包括比例块90和积分器92,该积分器包括存储器imem 94,该存储器保留ii型pll所计算的主节点和从节点之间的频率偏移的换算值。该换算值将视需要由图1的块24中的其他状态控制。将比例块90和积分器92的输出在加法器96中求和并且作为控制输入df施加到nco 36,从而生成输出信号。

[0056]

如上所指示,状态机控制器22确定图1所示的pll块24的状态。例如,状态机控制器22可将pll块24设定为以ii型pll状态28发挥功能,该ii型pll状态可用于ieee 1588应用。在该状态下,pll块24锁定到传入分组流12。可通过命令来设定状态机控制器22以使pll块24处于ii型pll状态28,这允许用户无缝地测试时钟恢复设备10,就像其是没有附加状态的简单ii型pll一样。

[0057]

状态机控制器22在以下情况之后触发附加状态:基准切换;初始化;网络断开;或主节点或本地振荡器上的频率或相位(时间)跳变,如分别在图3至图8中示出。在这些状态

中的一些状态中,可以以比ii型pll状态28下显著更快的方式校正相位(时间)和频率,同时在返回到ii型pll28操作之前准备适当值来插入到积分器存储器imem 94(图9)中。ii型pll状态28操作被视为正常操作并且下文可进一步如此称呼。

[0058]

在监测状态26下,在考虑到受另一个激活流(未示出)控制的ptp主节点和本地nco 36的情况下计算imem 94的值的统计性估计。在从监测状态26退出时,将监测状态26下估计的最终频率偏移(df)值插入到imem94中。

[0059]

在快速锁定状态30(也称为快速锁定)下,通过以下方式启用简单快速相位补偿:在短时间周期内调节nco 36的频率,直到输入相位向下桥接到时间戳分辨率。该方法是递归的,并且df更新的最大值受到初始相位偏移、快速锁定迭代数以及可编程频率控制极限的控制。在pll理论中,频率控制极限限定最大频率变化率。在快速锁定状态下,执行快速相位锁定,同时保持df的正确值的动态估计。同样,在从该状态退出时,将快速锁定状态下确定的最终df加载到imem 94中。

[0060]

下文将参照下图12和图13更详细描述快速锁定状态。

[0061]

在步进时间状态32下,基于与主节点的偏移和允许的硬件特定的时间步长来在大时间步长中更新nco 36和相关联的相位偏移硬件。可多次进行较大的步长以满足硬件限制。在该状态期间,通过对相位求导来执行当前频率的后台估计以使pll 24在返回正常pll操作(或快速锁定)之前能够适当地被初始化。当使nco中的日历寄存器中的时间步进时,后台功能记录频率偏移的任何变化。在从步进时间状态32退出时,将df的最终值加载到imem 94中。后台任务保存时间步进中用去的周期的时间计数和输入相位的值。在退出步进时间状态32时,该后台任务将提供以下值:

[0062]

phasedifferencens=(当前相位)

–

启动相位+时间步长量

[0063]

于是,df(以ppb计)=-(phasedifferencens*1000)/eclipsedtimems其中eclipsedtimems是以ms计的步进时间周期。

[0064]

pll块24还具有空闲状态34,在该空闲状态下,pll块24处于其他状态均未激活的空闲模式。

[0065]

图2的状态图中更具体地示出了这些状态。快速锁定状态30包括两个不同潜在状态:如上所述的快速锁定状态30和强制快速锁定(forcedfastlock)状态30a,在后一状态下,不论输入相位阈值如何,均进入快速锁定态。

[0066]

状态机控制器22响应于来自加法器20的输入相位和来自块38的软复位命令来确定当前状态。锁定状态机块40(其不构成本发明的一部分)充当总体系统的锁定状态的监督器通知块24。只要系统处于锁定条件,pll操作的正常模式就保持处于状态28,否则系统将如下所述的那样操作。

[0067]

图3示出了状态机控制器22的操作以将pll块24置于空闲状态34。状态机控制器22在以下情况下将pll块24置于空闲状态34:该pll块先前处于监测状态26并且流12变为激活的(这意味着传入分组从它们不输送有效频率和定时信息的状态移动到tsu 14确定它们输送有效频率和定时信息的状态)或响应于来自块38的初始化/软复位,如“与”门42和“或”门44所指示。

[0068]

图4示出了状态机控制器22的操作以将pll块24置于步进时间状态32。当先前状态为空闲34、正常28、快速锁定30或强制快速锁定30a(即除监测状态之外的任何状态)并且在

存在激活流的情况下断言相位跳变检测器19所输出的“进行中步进时间”标志(如“或”门46和“与”门48所指示)时,状态机控制器22将pll块24置于步进时间状态32。“进行中步进时间”标志的断言与状态机控制器22将pll块24置于步进时间状态32之间存在一个中断延迟的宽限期。

[0069]

如果在激活ptp流上检测到比存储在相位跳变检测器19中的可编程阈值(其在一个非限制性示例中可为3微秒)更大的相位跳变,则相位跳变检测器19断言stepinprogress标志。

[0070]“进行中步进时间”标志引起状态机控制器22激活步进时间()块18并且将pll块24置于步进时间状态32。在该状态下,执行频率估计,同时闲置ii型pll状态28,如上所述。

[0071]

步进时间()块18监测ofm phase,并且如果ofm phase超过更大的阈值(例如20微秒),则步进时间()块18增加步长大小以更迅速地降低ofm phase偏移。

[0072]

图5示出了状态机控制器22的操作以将pll块24置于任选的强制快速锁定状态30a。如果客户/用户仅在以下条件下通过设定强制快速锁定标志来启用快速强制锁定功能,则状态机控制器22将pll块24置于强制快速锁定状态30a:1)先前状态是空闲状态34,tsu 14检测到传入流12为激活的,并且相位误差在步进时间阈值内,因此“进行中步进时间”标志未激活;或2)先前状态是步进时间状态32,相位误差在步进时间阈值内,因此“进行中步进时间”标志未激活,并且如tsu 14所检测,传入流12为激活的。

[0073]

因此如果先前状态是空闲状态34或步进时间状态32(如“或”门54所指示),存在激活流,并且步进时间未在进行中,即相位跳变检测器19所输出的“进行中步进时间”标志未被断言(如“与”门50、52的存在所指示),则状态机控制器22在存在强制快速锁定标志的情况下将pll 24置于强制快速锁定状态30a。

[0074]

图6中示出了用于转变到快速锁定状态30的条件,如具有反相输入的“与”门56、58、60、“与”门62和“或”门64所指示。

[0075]

如果先前状态是空闲状态34、步进时间状态32或正常状态28,tsu14检测到激活流,并且步进时间未在进行中,即“进行中步进时间”标志未被断言,则在存在“快速锁定进入”(fastlockenter)标志的情况下进入快速锁定状态30。

[0076]

当“快速锁定启用”(fastlockenabled)被断言(这意味着用户已选择允许时钟恢复设备在适当的时候进入快速锁定状态),时钟恢复设备被频率锁定(如状态机控制器22所确定),并且输入相位大于预设阈值时,由“与”门62生成“快速锁定进入”标志。输入相位是图1中的加法器20的输出,其也与积分器imem 94的输入相同。还需要“快速锁定未激活”(fastlocknotactive)标志,该标志是在退出快速锁定状态30时状态机控制器22所生成的控制标志。该标志确保在先前状态标志中的一个状态未清除时不重新启动快速锁定状态30。

[0077]

状态机控制器22在快速锁定激活时设定“进行中快速锁定”(fastlockinprogress)标志。

[0078]

图6表示这样的一些条件,在这些条件下,发生从空闲状态34、步进时间状态32和正常状态28到快速锁定状态30的转变。

[0079]

图7中示出了用于转变到正常状态28(即,ii型pll状态28)的条件,如具有一个反相输入的“与”门66、具有两个反相输入的“与”门70、“与”门72、74及具有三个反相输入的

“

与”门76以及“或”门78所指示。

[0080]

当先前状态是空闲34、快速锁定30、强制快速锁定30a或步进时间32时,在存在激活输入流(如tsu 14所检测)的情况下进入正常状态28。

[0081]

在先前状态是空闲34的情况下,还需要“无效快速锁定”(invalidfastlock)标志和“无效强制快速锁定”(invalidforcedfastlock)标志。另外,“进行中步进时间”标志必须未被断言。状态机控制器22在“与”门70的输出为真(1)时设定“无效快速锁定”标志,并且在“与”门72的输出为真时设定“无效强制快速锁定”标志。

[0082]

ofm块16的输出处的ofm相位降到预定阈值以下(如相位跳变检测器19所确定)会引起有效“进行中步进时间”标志的去除。

[0083]

如果先前状态是快速锁定状态30,则为了进入正常状态28,需要tsu14所检测到的有效流,并且不需要有效“进行中快速锁定”标志以确保快速锁定状态已结束。另外,“进行中步进时间”标志必须未被断言,如“与”门70的反相输入所指示。

[0084]

如果先前状态是强制快速锁定30a或步进时间32,则需要tsu 14所检测到的激活流、无效“快速锁定进入”标志、无效“强制快速锁定”标志和无效“进行中步进时间”标志,如“与”门76所示。

[0085]

最后,图8中示出了用于转变到监测状态26的条件,如“或”门80和具有一个反相输入的“与”门82所指示。响应于不存在tsu 14所检测到的激活流而从空闲状态34、正常状态28、快速锁定状态30、强制快速锁定状态30a或步进时间状态32中的任何一个状态进入监测状态26。

[0086]

如上文参照图4所指出,在刚好在启动后或在主节点和从节点之间的相位(时间)跳变时进入步进时间状态32。主节点和从节点之间的频率偏移跳变也可引起相位跳变。

[0087]

一旦已进入步进时间状态32,就将当前频率差值df保存到ii型pll的imem 94中并且ii型pll可停止其计算操作。

[0088]

一旦已清除“进行中步进时间”标志,如上所指出,如果用户已设定“强制快速锁定”标志,状态机控制器22就迫使pll 24进入强制快速锁定状态30a。

[0089]

在强制快速锁定状态30a下,执行预先指定数量的相位快速锁定循环以清除残留输入相位使之低于可编程阈值。通常,以ns限定可编程阈值。

[0090]

一旦已实现强制快速锁定,即,残留输入相位低于可编程阈值,就清除“进行中快速锁定”标志并且状态机控制器22在存在激活流的情况下将pll块24切换成ii型pll状态28,即,切换成正常操作模式,如上文相对于图7所述。

[0091]

如上文相对于图8所述,在任何状态期间,如果该流变为非激活的,则状态机控制器22将pll块24切换成固定100mhz滤波器带宽预测开环df估计模式/滤波,这也称为监测状态26。

[0092]

图10是根据本发明的实施方案的时钟恢复设备的tie(时间间隔误差)图,该tie图在时间0秒时具有初始1.2ppm(百万分率)频率偏移和2.343s时间偏移(未在该图中示出)。y轴表示以微秒计的时间(相位)偏移。x轴示出了实耗时间(从60秒开始)。图10示出了85mhz pll带宽时80s的快速相位和频率锁定时间。偏移和扰动由时间戳分辨率(在这种情况下为+/-4ns)引起。

[0093]

图11是根据本发明的实施方案的时钟恢复设备的tie(时间间隔误差)图,该tie图

具有初始9.2ppm频率偏移和1.743s时间偏移。y轴是以纳秒计的时间(相位)偏移。x轴是实耗时间。图11示出了85mhz pl带宽时100s的快速相位和频率锁定时间。

[0094]

在该示例中,在大约950秒时发生2μs的相位跳变,从而例如因线条上的毛刺而引起相位锁定损失。这使用快速锁定状态在少于十秒内进行校正。当相位偏移降至数纳秒以内时,相位锁定通常被视为已实现、在不存在快速锁定状态的情况下,使用pll 28时,通常需要约600秒才能实现相位锁定。

[0095]

现在将参照图12和图13更详细描述快速锁定状态。ii型pll中的回路滤波器的比例部分粗略地确定pll的带宽(f

c

),该pll具有等于1/2f

c

的时间常数t。当pll的输入频率和输出频率之间几乎没有差异(但可存在一些残差)时即发生频率锁定。比例部分(p部分)与积分部分(i部分)之和表示pll的输入处的频率偏移。此时,pll的输入和输出之间仍将存在相位误差,该相位误差可较显著。作为一般经验法则,已发现在大约4.5

×

时间常数t时(对于1mhz带宽而言,算出在大约716秒时)发生频率锁定。

[0096]

实现相位锁定需要更长时间,将在pll的输入和输出之间几乎没有相位差时获得相位锁定。当实现相位锁定时,p部分的贡献平均为零(经受一些抖动)并且i部分补偿输入信号的频率偏移。实际上,在频率锁定与相位锁定之间的时间中,剩余相位误差(由p部分的输出表示)缓慢转移到i部分。

[0097]

快速锁定状态的理念是通过代替正常pll回路来直接调节nco 36的频率,以此缩短实现完全锁定所需的时间。

[0098]

图12中示出了该概念。在开始时,输入(ref)从与nco 36的输出相关的相位偏移开始,如线ref(输入)信号和线out(输出信号)在y轴上的相位分离所指示。在开始时,输入ref还将具有与nco 36的输出相关的频率偏移,这由线ref的斜率表示。在预定目标时间时,时钟恢复设备的输出相位out应等于输入相位ref。使线ref延续到目标时间使得能够在目标时间时估计输入ref的相位。

[0099]

在快速锁定状态下,在确定目标时间的输入ref的相位之后,nco 36的频率被设定为使得线ref和out相交于目标时间。图13中示出了快速锁定状态下的频率响应。

[0100]

通常,一旦快速锁定被占用,该过程就持续达基于(125ms

×

initial_phase/psl)的较小值计算的具体最小时间极限,其中initial_phase是初始相位偏移并且psl是预定相位斜率极限或12.5秒。无论哪种方式,在该非限制性示例中,如果输入相位小于或等于8ns(该值在一个实施方案中是可编程阈值的默认值),快速锁定过程都会停止。

[0101]

本领域的技术人员应当理解,本文的任何框图均表示体现本发明原理的示例性电路的视图。例如,可通过使用专用硬件以及联合使用能够执行软件的硬件和适当软件来提供处理器。当由处理器提供时,这些功能可由单个专用处理器提供,由单个共享处理器提供,或由多个单独处理器(其中一些可为共享的)提供。此外,术语“处理器”的显式使用不应被理解为排他性地指能够执行软件的硬件,并且可隐式地包括但不限于数字信号处理器(dsp)硬件、网络处理器、专用集成电路(asic)、现场可编程门阵列(fpga)、用于存储软件的只读存储器(rom)、随机存取存储器(ram)以及非易失性存储器。还可以包括常规的和/或定制的其他硬件。本文所示的功能块或模块实际上可在合适处理器上运行的硬件或软件中实现。由于“加法器”可具有负输入,因此其当然也可在如此指示时充当减法器。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1