一种电性能优良的高纯半绝缘碳化硅衬底及其制备方法与流程

本技术涉及一种电性能优良的高纯半绝缘碳化硅衬底及其制备方法,属于半绝缘碳化硅衬底。

背景技术:

1、碳化硅是第三代半导体材料,具有较好的物理电子学特性及化学稳定性,其热导率高、击穿场强大、饱和电子漂移速率大,因此在高温、高频、大功率及耐腐蚀辐射器件制备及应用上具有广阔前景,广泛用于国防、航空航天、通信等领域,使用半绝缘碳化硅衬底制备的晶体管在10ghz频率下能够产生超过gaas微波部件五倍功率密度的功率。

2、目前实现半绝缘的方式基本分为三种:一种是通过人为引入较多的深能级杂质(如v、ti等),来补偿碳化硅晶体中非故意掺杂引入的浅能级杂质(如硼、铝等),实现半绝缘的高阻性能,如美国专利us5611955a;另一种是晶体中点缺陷的深能级来补偿剩余的浅能级杂质,如美国专利us6218680a和us6396080a;第三种是通过引入少量深能级杂质(如v、ti等),通过深能级缺陷和晶体中点缺陷的深能级共同补偿浅能级杂质,进而达到半绝缘的高阻性能,如cn1985029a和cn102560671a。

3、上述第一种和第三种方法都需要人为引入深能级杂质,其中引入量有差异,因此制备的晶体为半绝缘碳化硅或掺杂半绝缘碳化硅。虽然高温下电阻率稳定性好,如cn102560671a,晶体经过1800℃退火后,电阻率大部分保持在1e5ω*cm以上,但是由于深能级杂质的引入,对衬底质量及外延器件质量均会造成不利影响:一方面,深能级杂质目前主要通过固相掺杂引入,存在掺杂不均匀问题,影响掺杂的均匀性及电阻率均匀性,掺杂的不均匀问题还会对晶体的应力、结晶质量、热导率等产生影响,不利于晶体各项参数的一致性,也给长晶工艺调控提出较高要求;另一方面,掺杂剂的引入会削弱其电子性能,在微波器件中形成电荷陷阱,引发背栅效应,出现电流崩塌、漏电流离散和输出功率降低等问题。

4、上述第二种方法不会人为引入深能级杂质,晶体杂质含量低,制备的晶体为高纯半绝缘碳化硅。其制备的高纯半绝缘碳化硅衬底深能级杂质浓度极低(低于sims测试检测限),不存在明显的由于v等元素掺杂引起的问题,但由于浅能级杂质含量高(高于1e16atoms/cm3)、净浅杂质浓度大等问题,导致其电阻率稳定性差,1800℃退火后,电阻率一般会降低至1e5ω*cm以下,高温下电阻率的不稳定性会影响后续外延器件的性能和良率。除了衬底电阻率的稳定性对外延期间性能有影响外,衬底电阻率的均匀性也会影响下游器件性能均匀。

5、鉴于现有技术中存在的上述问题,而碳化硅衬底的电性能及结晶质量又是影响后续外延及器件应用的重要参数,因此有必要提供一种纯度高、杂质浓度低,且电阻率稳定性、片内及片间电阻率均匀性优良的半绝缘碳化硅衬底。

技术实现思路

1、为了解决上述问题,提供了一种电性能优良的高纯半绝缘碳化硅衬底及其制备方法,本方案中针对高纯半绝缘碳化硅晶体,通过对物料纯度的控制、长晶过程控制以及长晶完成后的原位退火,得到纯度高、电阻率高阻并且电阻率稳定性好的碳化硅衬底。本方案提供的高纯半绝缘碳化硅衬底,由于未进行人为掺杂,因此衬底不存在因掺杂带来的掺杂不均问题,同时也可避免电荷陷阱、背栅效应等问题,使得制备的下游器件性能更稳定。

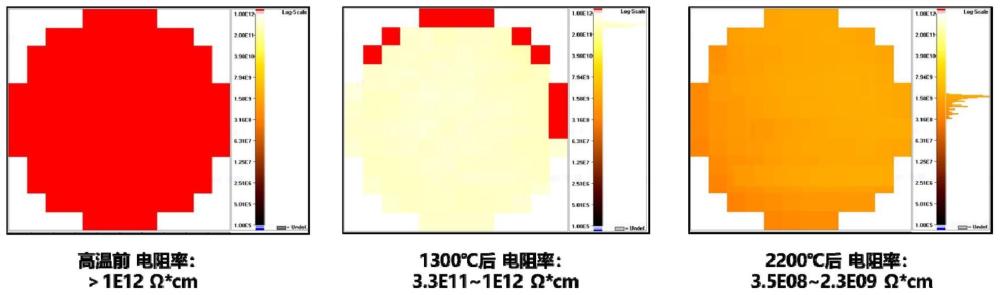

2、根据本技术的一个方面,提供了一种电性能优良的高纯半绝缘碳化硅衬底,所述高纯半绝缘碳化硅衬底的半绝缘面积比率为100%,且电阻率min不低于1e10ω*cm,且电阻率的高温稳定性优良,衬底放置在不高于2200℃的高温环境中,其电阻率保持不低于1e7ω*cm;

3、碳化硅晶体中的浅施主能级杂质浓度低于5e15 atoms/cm3,浅受主能级杂质浓度低于5e15 atoms/cm3,净浅能级杂质浓度低于3e15 atoms/cm3,深能级杂质浓度低于3e14atoms/cm3。

4、其中浅施主能级杂质包含但不限于ⅴa族元素,例如n、p元素,浅受主能级杂质包含但不限于ⅲa元素,例如b、al元素,深能级杂质包含但不仅限于元素周期表中的ⅰb、ⅱb、ⅲb、ⅳb、ⅴb、ⅵb、ⅶb、ⅷb族元素,例如矾(v)和钛(ti)元素,净浅能级杂质浓度指浅施主杂质与浅受主杂质浓度差值的绝对值。

5、可选的,所述高纯半绝缘碳化硅衬底,经温度t1高温存储t1时长后,电阻率min不低于1e10ω*cm,其中t1≤1300℃、t1<10h;经温度t2、高温存储t2时长后,电阻率min不低于1e7ω*cm,其中1300℃<t2≤2200℃、t2<10h。

6、可选的,所述高纯半绝缘碳化硅衬底片内电阻率极差值不大于1个数量级,径向电阻率相对标准偏差不大于10%。

7、可选的,所述高纯半绝缘碳化硅衬底中晶体轴向同种杂质的浓度差异不大于20%,晶体径向同种杂质的浓度差异不大于20%,所述同种杂质中的杂质包括深能级杂质和浅能级杂质。其中浅施主能级杂质包含但不限于ⅴa族元素,例如n、p元素,浅受主能级杂质包含但不限于ⅲa元素,例如b、al元素,深能级杂质包含但不仅限于元素周期表中的ⅰb、ⅱb、ⅲb、ⅳb、ⅴb、ⅵb、ⅶb、ⅷb族元素,例如矾(v)和钛(ti)元素。

8、可选的,所述高纯半绝缘碳化硅晶体热导率不低于3.3w/(cm*k),晶体轴向及径向热导率差异均不大于10%。

9、可选的,所述高纯半绝缘碳化硅衬底在hrxrd测试下,晶体半高宽fwhm不大于25arcsec,片内及同棒不同衬底间晶体半高宽fwhm差值均不大于10arcsec。

10、可选的,所述高纯半绝缘碳化硅衬底经koh腐蚀后,所得衬底贯穿位错的密度不大于2000cm-2,所述衬底贯穿位错包括tsd和ted。

11、可选的,所述高纯半绝缘碳化硅衬底在室温下epr测试晶体的自旋密度不大于5e15 cm-3。

12、可选的,所述高纯半绝缘碳化硅衬底包括但不限于4h、6h、8h、15r、3c晶型。

13、根据本技术的另一个方面,提供了一种高纯半绝缘碳化硅衬底的制备方法,所述制备方法包括以下步骤:

14、1)物料准备:准备石墨材料、保温材料和碳化硅粉料;

15、2)二次纯化:将碳化硅粉料置于长晶炉中进行二次纯化,温度2200℃~2400℃下保持时间不低于20h,设备真空度不大于0.1pa;

16、3)长晶过程:将纯化后的物料清理后,放入籽晶进行长晶;

17、4)原位退火:长晶过程结束后,压力升高至不低于900mbar,温度1800℃~2150℃下保持时间2~10h,之后缓慢降温至室温,降温速度不大于5℃/min,获得所述高纯半绝缘碳化硅晶体,经过后续加工后得到高纯半绝缘碳化硅衬底。

18、可选的,所述石墨材料的灰分小于5ppm,所述保温材料的灰分小于10ppm,所述碳化硅粉料的纯度不低于99.999%。

19、可选的,所述长晶过程包括以下步骤:

20、s1升温及形核:压力保持300~10mbar,升温速率5~10℃/min,温度升高至2100℃~2200℃,保持时间不小于10h;

21、s2降压及生长:压力降低至10~1mbar,降压速率0.2~5mbar/min,温度保持在2150℃~2200℃,降压总时间不大于10h,降压后稳定5~20h,稳定期间温度在2150℃~2200℃;生长过程温度不小于2250℃,生长时间不小于50h。

22、本技术的有益效果包括但不限于:

23、1.根据本技术的电性能优良的高纯半绝缘碳化硅衬底,在保证电性能优良的基础上,晶体纯度更高,不存在由于v等深能级杂质元素故意掺杂造成的掺杂不均匀的问题,从而影响电阻率均匀性以及晶体的应力、结晶质量、热导率等,解决了现有技术中由于掺杂剂的引入带来的削弱其电子性能的问题,降低在微波器件中形成电荷陷阱、引发背栅效应、出现电流崩塌、漏电流离散和输出功率降低等问题的发生。

24、2.根据本技术的电性能优良的高纯半绝缘碳化硅衬底,由于纯度高、杂质元素含量少,更易获得热导率高、位错密度低的高结晶质量的晶体,不仅利于晶体各项参数的一致性,还能降低长晶工艺调控的难度。

25、3.根据本技术的电性能优良的高纯半绝缘碳化硅衬底,电阻率稳定性、片内及片间电阻率均匀性要优于常规方式制备的高纯半绝缘碳化硅晶体。

26、4.根据本技术的电性能优良的高纯半绝缘碳化硅衬底,制备过程中,在长晶前进行二次纯化可以进一步去除物料中的杂质元素,可制备出纯度高,杂质浓度低的高纯半绝缘晶体,此外在制备过程增加原位退火步骤,能够降低晶体中的点缺陷密度,增加深能级复合点缺陷的形成,从而提高晶体的电阻率稳定性。

- 还没有人留言评论。精彩留言会获得点赞!