随机递增存储器、脉动随机递增存储器体系结构

本发明涉及神经网络加速器体系,尤其涉及一种随机递增存储器、脉动随机递增存储器体系结构。

背景技术:

1、目前,最新的一元计算神经网络加速器采用脉动阵列结构,如图1中所示,该结构主要包括一个一元处理单元阵列和边缘部件。其中,在一元处理单元阵列中,每个一元处理单元(pe)包括四种组件:权重寄存器(wreg)、输入寄存器(ireg)、一元乘法器(mul)和用于缓存一元比特流的累加器(acc)。除了累加器在所有数据流下都实现为高能耗的高位宽加法器,权重寄存器、输入寄存器和一元乘法器在各种数据流中略有不同。在权重静态(ws)数据流下,权重寄存器包括随机数寄存器、权重的绝对值寄存器和权重的符号寄存器,而输入寄存器由输入的符号寄存器和寄存输入的一元比特流中的一比特的d触发器组成。一元乘法器由一个比较器、一个用于一元乘法的与门和一个用于计算符号的异或门组成。权重寄存器和比较器的位宽可以是8位或16位,以支持不同的精度。在输入静态(is)数据流下,一元处理单元的结构类似于ws数据流,唯一的区别是权重和输入做了交换。对于输出静态(os)数据流,权重寄存器和输入寄存器都由符号寄存器和寄存一元数据流的一比特的d触发器构成。os数据流中的一元乘法器仅包括一个与门和一个异或门。其中,边缘部件(ph)包括一元比特流生成器、随机数生成器和先进先出缓存(fifo)。在ws和is数据流中,一元处理单元阵列左侧的边缘部件由一列fifo、一元比特流生成器和随机数生成器组成。每行一元处理单元共享一对一元比特流生成器和随机数生成器。另一方面,位于一元处理单元阵列顶部的边缘部件仅由fifo组成。在os数据流中,两个边缘部件都由一列/行的fifo和一元比特流生成器组成,每个一元比特流生成器由一行/列的一元处理单元共享。总体而言,边缘部件在确保整个一元处理单元阵列的有效数据重用和同步方面发挥着至关重要的作用。

2、该一元处理单元阵列的操作类似于传统的二进制处理单元阵列。首先,如有必要,将相关数据预加载到一元处理单元中,并保持不动,直到计算出输出特征图。例如,在ws数据流中,权重在计算之前流入每个一元处理单元的权重寄存器。边缘部件中的一元比特流生成器或随机数生成器然后生成一元比特流或随机数,这些比特流或随机数被输送到一元处理单元阵列中,并被多个一元处理单元复用。一元比特流或随机数的复用使得只需在边缘部件放置一元比特流生成器,从而一元比特流生成器的功耗和面积开销得以被一行一元处理单元平摊。当一元比特流或随机数在一元处理单元阵列中流动的同时,每个一元处理单元中的累加器需要将新计算得到的一元比特流重新转换为二进制数。

3、但该现有的一元计算神经网络加速器面临着缓存一元比特流的能耗开销大的问题,缓存一元比特流需要高能耗的高位宽二进制累加器。具体地,由于一元比特流包含数百到数千个比特,缓存完整的一元比特流需要大量的存储容量,从而造成大量的功耗和面积开销。相反,如果将一元比特流累加成二进制数,则可以指数级降低缓存一元比特流的功耗和面积开销。因此,现有技术一般使用二进制累加器将一元比特流转换成二进制数格式存储。该二进制累加器的高能耗来源于其进位传递问题。具体地,当将一元比特流中的“1”累加到二进制数上时,二进制数的每个比特都可能接收来自低位的进位,该进位可能使当前比特翻转并为下一个比特生成新的进位。结果,这些进位可以从最低有效比特传递到最高有效比特(即,进位传递),导致二进制数的全比特翻转。例如,当把“1”累加到“01111b”上时,进位将翻转所有五个比特。由于进位传递,每次累加都需要激活二进制数的所有比特,因此需要高位宽加法器来实现,导致累加器的高能耗问题。相比于其它的部件(权重寄存器、输入寄存器和一元乘法器),累加器成为能耗的瓶颈。

技术实现思路

1、本发明的目的是解决上述现有技术的累加能耗瓶颈问题,提出了一种随机递增存储器、脉动随机递增存储器体系结构。该随机递增存储器能够将一元比特流累加为偏斜数格式,并与脉动阵列结构集成,以降低累加能耗,提升能效。

2、为了实现上述目的,本发明一方面提供了一种随机递增存储器,包含:

3、多个偏斜单元,配置为将一元比特流存储为偏斜数格式,每一偏斜数至多包含一数字“2”,每一该偏斜单元存储数字“0”、“1”或“2”中的其中之一;

4、至少一计算单元,配置为对该多个偏斜单元存储的偏斜数进行递增操作。

5、在一些实施例中,多个偏斜单元排列形成多路偏斜阵列;

6、若一偏斜数不包含数字“2”,激活存储该偏斜数的最低有效位的一偏斜单元并读取到该计算单元进行递增;

7、若一偏斜数包含数字“2”,根据该偏斜数中数字“2”的存储位置选择激活相邻其中一个该偏斜单元并读取到该计算单元进行递增。

8、在一些实施例中,若该被激活的偏斜单元相邻位置处,存在存储数字“2”的一偏斜单元,将该偏斜单元存储的数字清除为“0”。

9、在一些实施例中,每一路偏斜阵列配置至少一计算单元,

10、各个被激活的偏斜单元由其所属一路的偏斜阵列的该计算单元进行递增。

11、在一些实施例中,当一元比特流完成累加时,将所有偏斜数读出;且在一个时钟周期中,最多允许一偏斜数被读出。

12、在一些实施例中,每一该偏斜单元包含:

13、一数据比特模块,

14、一偏斜比特模块,用于存储一比特数据,以及激活相邻的偏斜单元;且该偏斜比特模块与该数据比特模块相连,且该偏斜比特模块同时连接与该计算单元;该偏斜比特模块包含:

15、第一传输门、第二传输门、第三传输门,每一传输门包含第一端、第二端、第三端、第四端;

16、第一开关,其栅极连接至该第一传输门的第一端,源极或漏极其中之一接地,另一连接至该第一传输门的第四端、以及该第二传输门的第二端;

17、第二开关,其源极或漏极其中之一接电源电压,另一连接至该第二传输门的第四端、以及该第三传输门的第四端;

18、一存储模块,一端连接至该数据比特模块;

19、该第二传输门的第四端、第三传输门的第四端均连接至该存储模块,该第一传输门的第四端直接连接至该数据比特模块;

20、该第一传输门的第一端与第三端、该第二传输门的第一端与第三端、该第三传输门的第一端与第三端、以及该第二开关的栅极为控制端,与该计算单元连接,用于输入递增控制信号;

21、该第一传输门的第二端为激活信号端,该第三传输门的第二端为清零端。

22、在一些实施例中,通过该第一传输门的第一端、第二端,选择接地信号或者激活信号,接地信号在充/放电时被选择,激活信号在计算时被选择;

23、通过该第二传输门的第一端与第三端、该第三传输门的第一端与第三端、以及该第二开关的栅极,当生成两个数字“2”时,该第三传输门的第一端与第三端选择该传输门第二端的清零信号;当生成1个数字“2”时,该第二开关的栅极的输入信号选择电源电压信号。

24、在一些实施例中,每一该偏斜比特模块还包含:

25、一第一或非门,其一输入端与该存储模块的一输出端连接。

26、在一些实施例中,该计算单元负责递增控制信号的生成,包含:

27、第一感应放大与写入驱动器、第二感应放大与写入驱动器、一锁存器、第一与门、第二与门、第三与门,

28、该第一感应放大与写入驱动器与该第二感应放大与写入驱动器均至少包含:

29、第一引脚,配置为充放电引脚,用于连接一位线bl;

30、第二引脚,配置为充放电引脚,用于连接另一位线blb;

31、第三引脚,用于接收一控制信号b;

32、第四引脚,用于接收另一控制信号bb;

33、第五引脚,配置为写数据引脚wdata;

34、第六引脚,配置为写使能引脚wen;

35、第七引脚,配置为一串行输出引脚dout;以及

36、第八引脚,配置为一控制读使能引脚ren;

37、该第一感应放大与写入驱动器的第三引脚连接至该第二感应放大与写入驱动器的第四引脚,该第一感应放大与写入驱动器的第四引脚连接至该第二感应放大与写入驱动器的第三引脚,该第一感应放大与写入驱动器的第六引脚连接至该第二感应放大与写入驱动器的第六引脚,该第一感应放大与写入驱动器的第五引脚连接至该第二感应放大与写入驱动器的第七引脚,该第一感应放大与写入驱动器的第八引脚连接至该第二感应放大与写入驱动器的第八引脚;

38、以及

39、该第一感应放大与写入驱动器的第四引脚连接至该第一与门的一输入端;

40、该第二感应放大与写入驱动器的第五引脚连接至该第二与门的一输入端、以及该第三与门的一输入端;

41、该第一与门的输出端连接至该第三与门另一输入端,且该输出端通过一非门连接至该第二与门的另一输入端;

42、该第二与门输出端连接至该锁存器的清零端,该第三与门的输出端通过一非门连接至该锁存器的置位端。

43、在一些实施例中,当该第三引脚接收到低电平信号时,该第一引脚、第二引脚不能充/放电;

44、当该第三引脚接收到高电平信号时,根据该锁存器的值,该第一引脚、第二引脚由该第二感应放大与写入驱动器充/放电;

45、该第一引脚、第二引脚被放电一段时间后,将该第八引脚信号置一,二感应放大与写入驱动器感知该位线bl和位线blb之间的电平差异,并将读取的差异值存储到该锁存器中。

46、在一些实施例中,该随机递增存储器执行一次递增,包含:

47、预充电步骤,准备从该随机递增存储器中执行偏斜读;

48、偏斜读步骤,根据偏斜数中数字“2”的存储位置选择激活相邻其中一个该偏斜单元并读取到该计算单元

49、该第一引脚、第二引脚被放电一段时间后,将该第八引脚信号置一,二感应放大与写入驱动器感知该位线bl和位线blb之间的电平差异,并将读取的差异值存储到该锁存器中;

50、偏斜写步骤,通过将该第六引脚置一来启动偏斜写步骤,以递增激活的偏斜单元并将新的数字写回该随机递增存储器;

51、倾斜更新步骤,若在偏斜写步骤中向随机递增存储器写入新的数字“2”,则将新的数字“2”激活且旧的数字“2”清除为零;若没有生成新的数字“2”,将所有的位清零。

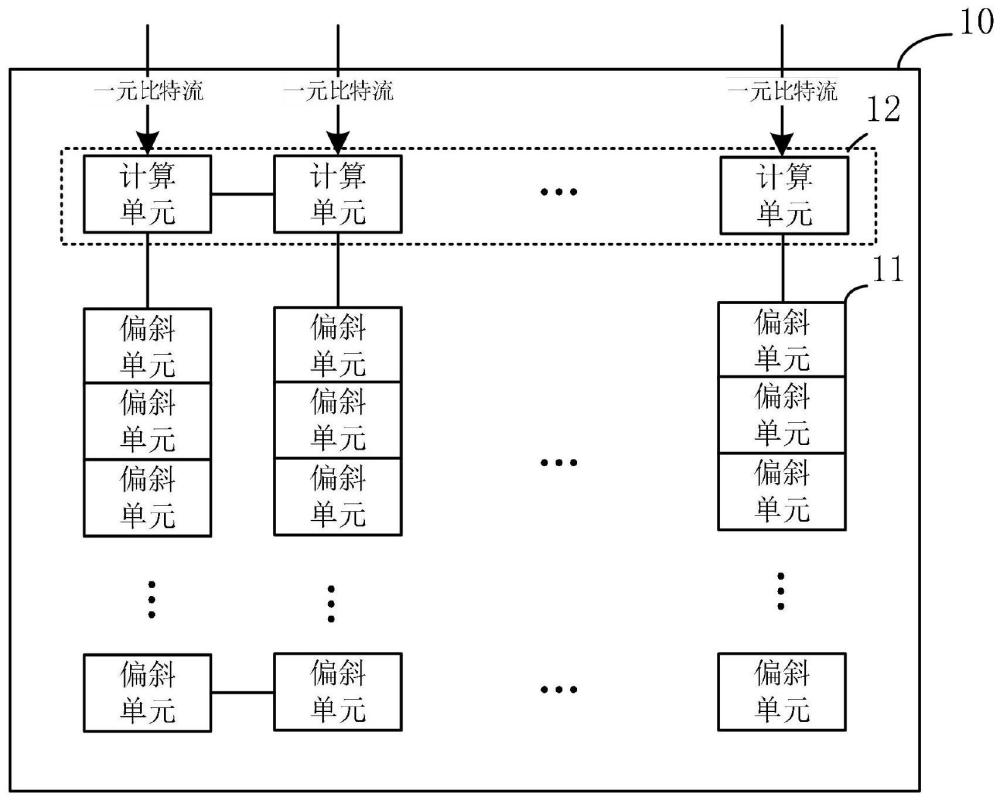

52、本发明另一方面还提供了一种脉动随机递增存储器体系结构,其包含多路存储器;

53、每一路存储器包含:

54、多个一元处理单元,呈多行排列分布;

55、多个随机递增存储器,

56、同一行的一元处理单元配置一随机递增存储器,每一该随机递增存储器采取上述的随机递增存储器;

57、多路存储器之间由边缘部件隔开。

58、在一些实施例中,每个一元处理单元将累加的值偏移一位,以将数字“-1,0,1”被替换为数字“0,1,2”;

59、每个一元处理单元保持一比特状态位模块,以确保每个周期只有一位被传输到该随机递增存储器。

60、在一些实施例中,该一元处理单元包含:

61、该一元处理单元包含:

62、一元乘法器,用于生成一绝对值位和一符号位;

63、两比特状态位模块,用于根据该符号位和绝对值位的值生成数字“0,1,2”中的其中之一,该两比特状态位模块包含:

64、一第三非门,输入为绝对值位,用于生成数字“0,1,2”的低位;

65、一第二或非门,输入为符号位以及第三非门的输出,用于生成数字“0,1,2”的高位;

66、该第三非门与第二或非门的输出组合为二元比特流;

67、一比特状态位模块,用于根据该两比特状态位模块生成的二元比特流,生成一元比特流,该一比特状态位模块包含:

68、一半加器,一输入端与该第三非门的输出端连接,

69、一d触发器,输入端与该半加器的数据输出端连接,由半加器的输出更新,且该d触发器的输出端反馈连接至该半加器的另一输入端;

70、一第一或门,一输入端为该半加器的进位端,另一输入端为该第二或非门的输出端,第一或门输出端连接至该随机递增存储器,由该半加器产生的进位与数字“0,+1,+2”的高位进行“或”运算,生成一元比特流。

71、在一些实施例中,每个随机递增存储器配有一转换器,用于将偏斜数转换回二进制数。

72、在一些实施例中,该转换器包含:

73、一加法器,将偏斜数的偶数位和奇数位相加,并将和左移一位,得到一加法结果;

74、一并行计数器,计算偏斜数中的数字“1”的个数,其中数字“2”表示两个数字“1”;

75、第一减法器,其二输入端分别与该加法器以及该并行计数器的输出端连接,用于从该加法结果中减去数字“1”的个数,并生成与读出的偏斜数相对应的二进制数;

76、第二减法器,其一输入端与该第一减法器输出端连接,另一输入端与输入寄存器连接,用于将生成的二进制数减去一元比特串的长度,以消除从累加到递增的转换的影响。

77、在一些实施例中,该边缘部件包含感应放大器、写入驱动器、寄存器、加法器至少其中之一。

78、由以上方案可知,本发明的优点在于:

79、本发明提供的面向一元计算的脉动随机递增存储器体系结构,该体系结构中的随机递增存储器能够将一元比特流累加为偏斜数格式,并与脉动阵列结构集成,随机递增存储器累加功耗显著降低,整个脉动随机递增存储器体系结构的得到能效显著提升。

- 还没有人留言评论。精彩留言会获得点赞!