半导体结构及其形成方法与流程

1.本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

2.随着集成电路的集成度不断提高,集成电路向亚微米、深亚微米方向快速发展,其图案线宽也将越来越细,这对半导体工艺提出了更高的要求。因此,对如何实现细线宽图案进行深入研究以适应半导体工艺的新要求已成为一个刻不容缓的课题。

3.光刻技术(lithograph)是实现集成电路图案的关键工艺技术。在光刻技术中,将感光材料(光刻胶)涂覆于基底的薄膜上,采用与光刻胶感光特性相应的波段的光,透过具有特定图案的掩膜板照射至光刻胶表面,经显影后形成与掩膜板上的图案相对应的光刻胶图形。在集成电路的后续工艺中,以此光刻胶图形作为阻挡层对其下的薄膜进行选择性刻蚀,便可以将掩膜板上的图案完整地转移到基底的薄膜上。集成电路的图案线宽越细,要求光刻胶的成像分辨率越高,而光刻胶的成像分辨率与曝光光源的波长成反比,因此,缩小曝光光源的波长成为实现细线宽图案的主要途径。

4.目前,随着集成电路的发展,光刻技术经历了g线光刻(436nm)、i线光刻(365nm)、krf深紫外光刻(248nm)以及arf深紫外光刻(193nm)等发展历程。曝光光源的种类包括近紫外光(nearultra-violet,nuv)、中紫外光(midultra-violet,muv)、深紫外光(deepultra-violet,duv)、极紫外光(extreme ultraviolet lithography,euv)等多种。

技术实现要素:

5.本发明实施例解决的问题是提供半导体结构及其形成方法,提升半导体结构的性能。

6.为解决上述问题,本发明实施例提供一种半导体结构的形成方法,包括:提供基底;在所述基底上形成有机层,所述有机层中具有露出所述基底的开口;在所述开口中形成阻断结构材料层,所述阻断结构材料层包括第一阻断层,所述第一阻断层保形覆盖所述开口侧壁以及所述开口底部,所述开口侧壁上的所述第一阻断层围成缝隙,所述阻断结构材料层还包括位于所述缝隙中的第二阻断层,所述第二阻断层的耐刻蚀度大于所述第一阻断层的耐刻蚀度;去除所述第二阻断层以及覆盖所述第二阻断层侧壁的所述第一阻断层,剩余的所述第一阻断层作为阻断结构,所述阻断结构适于作为图形化所述基底的掩膜;形成所述阻断结构后,去除所述有机层,露出所述基底。

7.相应的,本发明实施例还提供一种半导体结构,包括:基底;有机层,位于所述基底上,所述有机层中具有贯穿有机层的开口;第一阻断层,保形覆盖在所述开口侧壁以及所述开口的底部,所述开口侧壁上的所述第一阻断层围成缝隙;第二阻断层,位于所述缝隙中,所述第二阻断层的耐刻蚀度大于所述第一阻断层的耐刻蚀度。

8.与现有技术相比,本发明实施例的技术方案具有以下优点:

9.本发明实施例中,所述开口中形成有阻断结构材料层,所述阻断结构材料层包括

第一阻断层和第二阻断层,所述开口侧壁上的所述第一阻断层围成缝隙,所述第二阻断层位于所述缝隙中,所述第二阻断层的耐刻蚀度大于所述第一阻断层的耐刻蚀度。本发明实施例中,所述第二阻断层提高了所述阻断结构材料层的中间区域的耐刻蚀度,在刻蚀所述阻断结构材料层形成阻断结构的过程中,所述阻断结构材料层的中间区域不易被过快地去除,从而提高了阻断结构的顶面平坦度,这使得所述阻断结构在后续过程中能起到更好的掩膜作用,进而提升半导体结构的性能。

附图说明

10.图1至图4是一种半导体结构的形成方法中各步骤对应的结构示意图;

11.图5至图16是本发明半导体结构的形成方法一实施例中各步骤对应的结构示意图。

具体实施方式

12.目前所形成的半导体结构仍有性能不佳的问题。现结合一种半导体结构的形成方法分析半导体结构性能不佳的原因。

13.图1至图4,是一种半导体结构的形成方法中各步骤对应的结构示意图。

14.如图1所示,提供基底1,所述基底1上形成有有机层2,所述有机层2中具有露出所述基底1的开口3。

15.如图2所示,在所述开口3以及所述开口3露出的所述基底1上保形覆盖阻挡材料层4。

16.如图3所示,去除位于所述有机层2(如图2所示)顶端的所述阻挡材料层4(如图2所示);去除所述有机层2顶端的所述阻挡材料层4后,刻蚀所述有机层2和剩余的所述阻挡材料层4,刻蚀后剩余的所述阻断材料层4作为所述阻挡层5。

17.如图4所示,以所述阻挡层5为掩膜刻蚀所述基底1,形成衬底6和位于所述衬底6上的目标图形7。

18.所述阻挡材料层4的材料通常为氧化硅,通常采用原子层沉积工艺(atomic layer deposition,ald)等台阶覆盖性好的工艺在所述有机层2以及所述有机层2露出的基底1上形成所述阻挡材料层4,所述在沉积过程中,一般先向所述开口3中通入硅烷,所述硅烷吸附在所述有机层2的表面,之后再向所述开口3中通入含氧气体,硅烷与含氧气体反应形成氧化硅。在形成所述阻挡材料层4的过程中,随着沉积厚度的逐渐增加,所述开口3侧壁上的所述阻挡材料层4之间的缝隙越来越接小,硅烷和含氧气体不易进入缝隙中,导致所述开口3中间区域的氧化硅形成质量较差,相应的中间区域的所述阻挡材料层4的硬度较低,在后续以所述阻挡层5为掩膜刻蚀所述基底1的过程中,所述阻挡层5的中间区域易过快的被去除,因此所述阻挡层5不能很好的起到掩膜作用,导致目标图形7的形成质量较差。

19.为了解决所述技术问题,本发明实施例提供一种半导体结构的形成方法,包括:提供基底;在所述基底上形成有机层,所述有机层中具有露出所述基底的开口;在所述开口中形成阻断结构材料层,所述阻断结构材料层包括第一阻断层,所述第一阻断层保形覆盖所述开口侧壁以及所述开口底部,所述开口侧壁上的所述第一阻断层围成缝隙,所述阻断结构材料层还包括位于所述缝隙中的第二阻断层,所述第二阻断层的耐刻蚀度大于所述第一

reflective coating,底部抗反射涂层)材料、odl(organic dielectric layer,有机介电层)材料、光刻胶、darc(dielectric anti-reflective coating,介电抗反射涂层)材料、duo(deep uv light absorbing oxide,深紫外光吸收氧化层)材料或apf(advanced patterning film,先进图膜)材料。

36.其他实施例中,所述有机层还可以为其他易于去除的材料,使得在后续去除有机层时减少对基底以及后续形成的阻断结构的损伤。

37.具体的,形成有机层103的步骤包括:形成覆盖所述基底的有机材料膜(图中未示出);图形化所述有机材料膜,在所述有机材料膜中形成所述开口104,剩余的所述有机材料膜作为有机层103。

38.本实施例中,采用旋涂工艺形成所述有机材料膜,所述有机材料膜的表面平坦度较高。

39.需要说明的是,本实施例中,所述开口104的延伸方向与所述核心层101的延伸方向相垂直。其他实施例中,所述开口的延伸方向还可以与核心层的延伸方向相平行。

40.需要说明的是,所述开口104位于所述核心层101之间的区域上,为后续在所述核心层101之间的区域形成第一阻断材料层做准备,从而使所述第一阻断材料层填充所述核心层101之间的区域。

41.结合参考图7至图10,在所述开口104(如图7所示)中形成阻断结构材料层107(如图10所示),所述阻断结构材料层107包括第一阻断层105(如图10所示),所述第一阻断层105保形覆盖所述开口104侧壁以及所述开口的底部,所述开口104侧壁上的所述第一阻断层105围成缝隙108(如图7c所示),所述阻断结构材料层107还包括位于所述缝隙108中的第二阻断层106(如图10所示),所述第二阻断层106的耐刻蚀度大于所述第一阻断层105的耐刻蚀度。

42.所述开口104中形成有阻断结构材料层107,所述阻断结构材料层107包括第一阻断层105和第二阻断层106,所述开口104侧壁上的所述第一阻断层105围成缝隙108,所述第二阻断层106位于所述缝隙108中,所述第二阻断层106的耐刻蚀度大于所述第一阻断层105的耐刻蚀度。本发明实施例中,所述第二阻断层106提高了所述阻断结构材料层107的中间区域的耐刻蚀度,在刻蚀所述阻断结构材料层107形成阻断结构的过程中,所述阻断结构材料层107的中间区域不易被过快地去除,从而提高了阻断结构的顶面平坦度,这使得所述阻断结构在后续过程中能起到更好的掩膜作用,进而提升半导体结构的性能。

43.需要说明的是,本实施例中,所述中间区域指代的是在所述阻断结构材料层107的延伸方向上,所述阻断结构材料层107中与所述缝隙108相对应的区域;所述边缘区域指代的是所述阻断结构材料层107中围绕所述中间区域的剩余区域。

44.本实施例中,所述第一阻断层105的材料为介电材料。

45.具体的,第一阻断层105的材料包括氧化硅、氮化硅、碳氮化硅、碳氮氧化硅、氮氧化硅、氮化硼和碳氮化硼中的一种或多种。本实施例中,所述第一阻断层105的材料为氧化硅。氧化硅具有较高的工艺兼容性,有利于降低形成第一阻断层105的工艺难度和工艺成本。

46.所述第二阻断层106的耐刻蚀度大于所述第一阻断层105的耐刻蚀度。

47.本实施例中,所述第二阻断层106的材料为金属氧化物。所述金属氧化物具有较高

的耐刻蚀性,且与介电材料具有高刻蚀选择比,在高纵横比的通孔、开口或沟槽中具有良好的填充能力。

48.具体的,所述金属氧化物包括:氧化钛、氧化钽、氧化钨、氧化钴、氧化铬、氧化矾、氧化镉、氧化铪、氧化铟、氧化铁、氧化铝、氧化锆、氧化锌和氧化镍中一种或多种。

49.具体的,形成所述阻断结构材料层107的步骤包括:

50.如图7所示,图7包括图7a、图7b和图7c,其中,图7a是俯视图,图7b是图7a在aa方向的剖面图,图7c是图7a在cc方向的剖面图,形成第一阻断材料层109,所述第一阻断材料层109保形覆盖所述有机层103以及所述开口104底部和侧壁,所述开口104侧壁上的所述第一阻断材料层109围成所述缝隙108,所述缝隙108的延伸方向与所述开口104的延伸方向相同。

51.所述第一阻断材料层109为后续形成第一阻断层做准备。

52.本实施例中,采用原子层沉积工艺(atomic layer deposition,ald)形成所述第一阻断材料层109。原子层沉积工艺包括进行多次的原子层沉积循环,原子层沉积工艺的间隙填充性能和阶梯覆盖性好,相应提高了所述第一阻断材料层109的保形覆盖能力。在其他实施例中,还可以采用等离子体增强化学的气相沉积法(plasma enhanced chemical vapor deposition,pecvd)形成所述第一阻断材料层。

53.需要说明的是,所述缝隙108为后续形成第二阻断材料层提供空间位置。

54.还需要说明的是,所述缝隙108的侧壁与所述基底法线的夹角不宜过大也不宜过小。后续所述半导体结构的形成方法还包括:去除所述第二阻断层106以及覆盖所述第二阻断层106侧壁的所述第一阻断层105,剩余的所述第一阻断层105作为阻断结构。以垂直于所述开口104的延伸方向为横向,若所述夹角过大,相应的形成在所述缝隙108中的第二阻断层106顶部的横向尺寸过大,因为所述第二阻断层106的耐刻蚀度高于所述第一阻断层105的耐刻蚀度,因此,后续去除所述第二阻断层106的难度较大,易导致形成的阻断结构的中间区域过高于所述阻断结构的边缘区域。若所述夹角过小,形成所述第二阻断层106的反应气体不易进入所述缝隙108中,从而在所述缝隙108中形成第二阻断层106的难度较大,导致所述第二阻断层106的形成质量不佳,进而在刻蚀第一阻断层105和第二阻断层106的过程中,所述第二阻断层106易过快的被去除,易导致形成的阻断结构的中间区域过低于所述阻断结构的边缘区域,因此所述阻断结构在后续过程中难以起到较好的掩膜作用。本实施例中,所述缝隙108的侧壁与所述基底法线的夹角为5

°

至10

°

。

55.继续参考图7a,本实施例中,形成所述缝隙108的过程中,沿所述缝隙108的延伸方向,所述缝隙108的任一端还均具有两个分叉113。

56.需要说明的是,所述缝隙108的底端高于或齐平于位于所述核心层101顶部的侧墙材料层102的顶面。

57.所述缝隙108的底端高于或齐平于位于所述核心层101顶部的侧墙材料层102的顶面,从而使得后续形成在所述缝隙108中的第二阻断材料层的底端高于或齐平于位于所述核心层101顶部的侧墙材料层102的顶面。

58.还需要说明的是,在图7a和图7b中,所述第一阻断材料层109中的黑线用于表示所述开口104不同侧壁上的所述阻断材料层105接触面。

59.如图8所示,图8包括图8a和图8b,图8b为图8a在cc方向的剖面图,形成保形覆盖所

述第一阻断材料层109的第二阻断材料层110,所述第二阻断材料层110填满所述缝隙108(如图7所示)。

60.所述第二阻断材料层110为后续形成第二阻断层做准备。

61.本实施例中,采用原子层沉积工艺形成所述第二阻断材料层110。原子层沉积工艺的间隙填充性能和阶梯覆盖性好,相应提高了所述第二阻断材料层110的保形覆盖能力,使得形成的所述第二阻断材料层110中不易产生空洞等缺陷。

62.如图9所示,图9包括图9a和图9b,图9b为图9a在cc方向的剖视图,去除高于所述第一阻断材料层109顶部的所述第二阻断材料层110。

63.去除高于所述第一阻断材料层109顶部的所述第二阻断材料层110,露出第一阻断材料层109的顶面,从而为后续去除高于所述有机层103(如图6所示)的第一阻断材料层109做准备。

64.本实施例中,采用干法刻蚀工艺去除高于所述第一阻断材料层109顶部的所述第二阻断材料层110。干法刻蚀工艺具有各向异性的刻蚀特性,在采用干法刻蚀工艺去除高于所述第一阻断材料层109顶部的所述第二阻断材料层110的过程中,能够以所述第一阻断材料层109的顶部作为刻蚀停止层,易于控制刻蚀停止位置,降低对其他膜层结构的损伤。

65.本实施例中,所述第二阻断材料层110的材料为金属氧化物,相应的,采用干法刻蚀工艺去除所述第一阻断材料层109顶部的所述第二阻断材料层110的过程中,采用的刻蚀气体包括cl2和ch4。

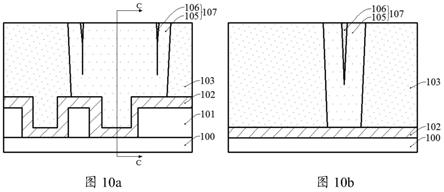

66.如图10所示,图10包括图10a和图10b,图10b为图10a在cc方向的剖面图,去除高于所述第一阻断材料层109顶部的所述第二阻断材料层110后,去除高于所述有机层103的第一阻断材料层109和第二阻断材料层110,剩余的所述第一阻断材料层109作为第一阻断层105,剩余的所述第二阻断材料层110作为第二阻断层106,所述第一阻断层105和第二阻断层106作为所述阻断结构材料层107。

67.所述阻断结构材料层107的中间区域为第二阻断层106,所述第二阻断层106的耐刻蚀度大于所述第一阻断层105的耐刻蚀度。因此在后续去除所述第二阻断层106以及覆盖所述第二阻断层106侧壁的所述第一阻断层105的过程中,所述阻断结构材料层107的中间区域不易被过快去除,形成的阻断结构的中间区域不易低于所述阻断结构的边缘区域,有利于提高阻断结构的顶面平坦度。

68.本实施例中,采用干法刻蚀工艺去除高于所述有机层103的第一阻断材料层109和第二阻断材料层110。干法刻蚀工艺具有较快的刻蚀速率,采用干法刻蚀工艺去除高于所述有机层103的第一阻断材料层109和第二阻断材料层110的过程中,能够以所述有机层103的顶部作为刻蚀停止层,能够控制刻蚀停止位置,降低对其他膜层结构的损伤。

69.本实施例中,在一步干法刻蚀工艺中去除高于所述有机层103的第一阻断材料层109和第二阻断材料层110,有利于简化工艺步骤,提高半导体结构的形成效率。

70.本实施例中,去除高于所述有机层103的第一阻断材料层109和第二阻断材料层110的过程中,采用的刻蚀气体包括第一类刻蚀气体和第二类刻蚀气体,第一类刻蚀气体包括:cl2和ch4,第二类刻蚀气体包括:碳氟气体和碳氢氟气体。

71.本实施例中,形成阻断结构材料层107的步骤中,所述第二阻断层106位于所述缝隙108中,相应的所述第二阻断层106的底端高于或齐平于位于所述核心层101顶部的侧墙

材料层102的顶面。

72.所述第二阻断层106的底端高于或齐平于位于所述核心层101顶部的侧墙材料层102的顶面,这易于使得后续形成的阻断结构的顶部能够高于位于所述核心层101顶部的侧墙材料层102的顶面,从而有利于提高所述阻断结构顶端的平坦度。

73.还需要说明的是,所述第一阻断材料层109(如图7所示)填充在所述核心层101之间,相应的,所述第一阻断层105也形成在所述核心层101之间。

74.参考图11至图14,去除所述第二阻断层106以及覆盖所述第二阻断层106侧壁的所述第一阻断层105,剩余的所述第一阻断层105作为阻断结构111(如图14所示),所述阻断结构111适于作为图形化所述基底的掩膜。

75.所述阻断结构111为后续图形化所述基底做准备。

76.本实施例中,采用多次阻断刻蚀工艺去除所述第二阻断层106以及覆盖所述第二阻断层106侧壁的所述第一阻断层105。

77.采用多次阻断刻蚀工艺去除所述第二阻断层106以及覆盖所述第二阻断层106侧壁的所述第一阻断层105,有利于提升形成的所述阻断结构111顶面的平坦度;因为所述第二阻断层106的耐刻蚀度大于所述第一阻断层105的耐刻蚀度,本发明实施例通过采用多次阻断刻蚀工艺的方式,在去除所述第一阻断层105后,能够避免所述第二阻断层106出现倒塌的情况。

78.具体的,所述阻断刻蚀工艺的步骤包括:

79.如图11所示,图11包括图11a和图11b,图11b为图11a在cc方向的剖面图,去除部分厚度的所述有机层103。

80.去除部分厚度的所述有机层103,露出第一阻断层105的部分侧壁,使得后续去除高于剩余的所述有机层103的所述第一阻断层105的过程中,产生的聚合物杂质能够较快的去除,从而聚合物杂质不易对刻蚀过程产生不良影响,高于所述有机层103的第一阻断层105易去除干净,进而提高刻蚀质量,且刻蚀过程中能够以所述有机层103的顶面为刻蚀停止层,使得被所述有机层103覆盖的膜层结构不易受到损伤。

81.本实施例中,采用干法刻蚀工艺去除部分厚度的所述有机层103。干法刻蚀工艺有利于精确控制所述有机层103的去除厚度。其他实施例中,还可以采用灰化工艺去除部分厚度的所述有机层。

82.需要说明的是,刻蚀所述有机层103的厚度不易过大,也不宜过小。若刻蚀所述有机层103的厚度过大,相应的高于剩余的所述有机层103的第一阻断层105过多,后续去除高于剩余的所述有机层103的所述第一阻断层105的过程中产生的聚合物杂质(polymer)过多,所述聚合物杂质清除不及时,易对刻蚀所述第一阻断层105产生影响,易导致剩余的所述第一阻断层105的顶面平坦度较差,且不利于后续去除高于剩余的所述有机层103的所述第二阻断层106。若刻蚀所述有机层103的厚度过小,会需要较多次数的阻断刻蚀工艺,易增加去除所述第二阻断层106以及覆盖所述第二阻断层106侧壁的所述第一阻断层105的工艺时间。本实施例中,每一次所述阻断刻蚀工艺中,刻蚀所述有机层103的厚度为10纳米至30纳米。

83.如图12所示,图12包括图12a和图12b,图12b为图12a在cc方向的剖面图,去除高于剩余的所述有机层103的所述第一阻断层105。

84.因为所述第二阻断层106的横向尺寸较小,直接刻蚀所述第二阻断层106的工艺难度较大,本发明实施例在去除高于剩余的所述有机层103的所述第一阻断层105后,高于剩余的所述有机层103的所述第二阻断层106被暴露,这更有利于后续去除高于剩余的所述有机层103的所述第二阻断层106。

85.本实施例中,采用干法刻蚀工艺去除高于剩余的所述有机层103的所述第一阻断层105。干法刻蚀工艺具有较快的刻蚀速率,且能够精确控制所述第一阻断层105的去除厚度,刻蚀过程中,以剩余的有机层103为刻蚀停止层,能够降低对其他膜层结构的损伤。

86.本实施例中,所述第一阻断层105的材料为氧化硅,相应的,去除高于剩余的所述有机层103的所述第一阻断层105的过程中采用的刻蚀气体包括:碳氟气体和碳氢氟气体中的一种或两种。

87.如图13所示,图13包括图13a和图13b,图13b为图13a在cc方向的剖面图,去除高于剩余的所述有机层103的所述第一阻断层105后,去除高于剩余的所述有机层103的所述第二阻断层106。

88.去除高于剩余的所述有机层103的所述第二阻断层106后,为进行下一次的阻断刻蚀工艺做准备。

89.本实施例中,采用干法刻蚀工艺去除高于剩余的所述有机层103的所述第二阻断层106。干法刻蚀工艺具有较快的刻蚀速率,能够精确控制所述第二阻断层106的去除厚度,采用干法刻蚀工艺去除高于剩余的所述有机层103的所述第二阻断层106的过程中,以剩余的有机层103为刻蚀停止层,能够降低对其他膜层结构的损伤。

90.本实施例中,所述第二阻断层106的材料为氧化钛,去除所述第二阻断层106的过程中采用的刻蚀气体包括:cl2和ch4。

91.需要说明的是,本实施例仅示意了一次阻断刻蚀工艺,本实施例中阻断刻蚀工艺的次数为多次。

92.如图14所示,图14包括图14a和图14b,图14b为图14a在cc方向的剖面图,本发明实施例通过多次阻断刻蚀工艺,形成阻断结构111。

93.形成所述阻断结构111的步骤中,所述阻断结构111的顶面高于或齐平于位于所述核心层101顶部的所述侧墙材料层102的顶面。

94.所述阻断结构111的顶面高于或齐平于位于所述核心层101顶部的所述侧墙材料层102的顶面的情况下,刻蚀形成阻断结构111过程中的负载效应不易导致阻断结构111边缘区域过高的高于阻断结构111的中心区域。

95.需要说明的是,所述阻断结构111的顶面至位于所述核心层101顶部的所述侧墙材料层102的顶面的距离不宜过大。若所述距离过大,位于所述核心层101顶端的侧墙材料层102上的所述阻断结构111在后续刻蚀过程中易起到掩膜作用,从而所述阻断结构111下方的所述核心层101不易被去除,进而所述核心层101下方的所述介质层100不易被去除,导致后续刻蚀所述介质层100形成的目标图形的质量较差。本实施例中,形成所述阻断结构111的步骤中,所述阻断结构111的顶面至位于所述核心层101顶部的所述侧墙材料层102的顶面的距离小于10纳米。

96.需要说明的是,所述第一阻断层105(如图10所示)形成在所述核心层101之间,相应的,形成的所述阻断结构111形成在所述核心层101之间。

97.参考图15,图15包括图15a和图15b,图15b为图15a在cc方向的剖面图,形成所述阻断结构111后,去除剩余的所述有机层103,露出所述基底。

98.去除剩余的所述有机层103,为后续以所述阻断结构111为掩膜刻蚀所述介质层100形成目标图形做准备。

99.本实施例中,采用灰化工艺去除所述有机层103。

100.参考图16,图16包括图16a和图16b,图16b为图16a在cc方向的剖面图,所述半导体结构的形成方法还包括:去除剩余的所述有机层103(如图14a所示)后,回刻蚀所述侧墙材料层102,去除所述介质层100表面的侧墙材料层102和位于所述核心层101(如图15所示)顶部的所述侧墙材料层102,剩余的所述侧墙材料层102作为侧墙层112;形成所述侧墙层112后,去除所述核心层101。

101.本实施例中,采用无掩膜干法刻蚀工艺去除所述介质层100表面的侧墙材料层102和位于所述核心层101顶部的所述侧墙材料层102。干法刻蚀工艺具有各向异性刻蚀的特性,有利于保证将所述核心层101顶部以及所述介质层100表面的侧墙材料层102完全去除的同时,对其他膜层结构的损伤较小,而且有利于避免对侧墙材料层102横向刻蚀,使得形成的侧墙层112的厚度不易减薄,从而保证所述侧墙层112能够在形成目标图形的步骤中起到刻蚀掩膜的作用。另外,无掩膜干法刻蚀工艺能够省去一张光罩(mask),降低形成所述侧墙层112的工艺成本。

102.需要说明的是,在形成所述侧墙层112的过程中,形成在所述核心层101之间的所述阻挡结构111也被刻蚀,相应的所述阻挡结构111的厚度降低,在后续过程中,所述阻挡结构111和所述侧墙层112一同作为刻蚀所述介质层100的刻蚀掩膜。

103.相应的,本发明实施例还提供一种半导体结构。参考图10,示出了本发明半导体结构一实施例的结构示意图,图10包括图10a和图10b,图10b为图10a在cc方向的剖面图。

104.所述半导体结构包括:基底;有机层103,位于所述基底上,所述有机层103中具有贯穿有机层103的开口104(如图6所示);第一阻断层105,保形覆盖在所述开口104侧壁以及所述开口104的底部,所述开口104侧壁上的所述第一阻断层105围成缝隙108(如图7c所示);第二阻断层106,位于所述缝隙108中,所述第二阻断层106的耐刻蚀度大于所述第一阻断层105的耐刻蚀度。

105.本发明实施例中,所述第一阻断层105和第二阻断层106构成阻断结构材料层107,所述开口104侧壁上的所述第一阻断层105围成缝隙108,所述第二阻断层106位于所述缝隙108中,所述第二阻断层106的耐刻蚀度大于所述第一阻断层105的耐刻蚀度。本发明实施例中,所述第二阻断层106提高了所述阻断结构材料层107的中间区域的耐刻蚀度,在刻蚀所述阻断结构材料层107形成阻断结构的过程中,所述阻断结构材料层107的中间区域不易被过快地去除,从而提高了阻断结构的顶面平坦度,这使得所述阻断结构在后续过程中能起到更好的掩膜作用,进而提升半导体结构的性能。

106.需要说明的是,本实施例中,所述中间区域指代的是在所述阻断结构材料层107的延伸方向上,所述阻断结构材料层107中与所述缝隙108相对应的区域;所述边缘区域指代的是所述阻断结构材料层107中围绕所述中间区域的剩余区域。

107.所述基底为后续形成半导体结构提供工艺基础。

108.本实施例中,所述基底包括衬底(图中未示出)、位于所述衬底上的介质层100、分

立于所述介质层100上的核心层101,以及保形覆盖所述核心层101和介质层100的侧墙材料层102。其他实施例中,所述基底还可以仅包含介质层。

109.本实施例中,所述衬底的材料为硅、锗、碳化硅、砷化镓或镓化铟,所述衬底还能够为绝缘体上的硅衬底或者绝缘体上的锗衬底。所述衬底内还能够形成有元器件,例如,pmos晶体管、cmos晶体管、nmos晶体管、电阻器、电容器或电感器等。

110.所述介质层100为后续形成导电材料提供工艺平台。

111.本实施例中,所述介质层100的材料为氧化硅。其他实施例中,所述介质层的材料还可以为氮化硅或者氮氧化硅。

112.所述核心层101和侧墙材料层102为后续形成侧墙层做准备。

113.所述侧墙材料层102的材料与所述核心层101具有刻蚀选择比。后续无掩膜刻蚀所述侧墙材料层102,在所述核心层101的侧壁上形成侧墙层后,还会去除核心层101,在去除所述核心层101的过程中,所述侧墙层不易受到损伤。

114.本实施例中,所述核心层101的材料包括氮化硅、氧化硅、硅、非晶硅、氮氧化硅和碳化硅中的一种或多种。本实施例中,核心层101的材料为氧化硅。

115.本实施例中,所述侧墙材料层102的材料包括氮化硅、氧化硅、硅、非晶硅、氮氧化硅和碳化硅中的一种或多种。本实施例中,所述侧墙材料层102的材料为氮化硅。氮化硅的硬度和致密度较高,与氧化硅具有较大的刻蚀选择比。

116.所述有机层103中具有所述开口104,所述开口104为第一阻断层105和第二阻断层106的形成提供空间位置。

117.本实施例中,所述有机层103的材料为有机材料,例如:barc材料、odl材料、光刻胶、darc材料、duo材料或apf材料。

118.其他实施例中,所述有机层还可以为其他易于去除的材料,使得在后续去除有机层时减少对基底以及后续形成的阻断结构的损伤。

119.需要说明的是,本实施例中,所述开口104的延伸方向与所述核心层101的延伸方向相垂直。其他实施例中,所述开口的延伸方向还可以与核心层的延伸方向相平行。

120.需要说明的是,所述开口104位于所述核心层101之间的区域上,相应的所述第一阻断层105填充所述核心层101之间的区域。

121.所述阻断结构材料层107中间区域为第二阻断层106,所述第二阻断层106的耐刻蚀度大于所述第一阻断层105的耐刻蚀度。因此在后续去除所述第二阻断层106以及覆盖所述第二阻断层106侧壁的所述第一阻断层105的过程中,所述阻断结构材料层中间区域不易被过快去除,形成的阻断结构的中间区域不易低于所述阻断结构的边缘区域,有利于提高阻断结构的顶面平坦度。

122.本实施例中,所述第一阻断层105的材料为介电材料。

123.具体的,第一阻断层105的材料包括氧化硅、氮化硅、碳氮化硅、碳氮氧化硅、氮氧化硅、氮化硼和碳氮化硼中的一种或多种。本实施例中,所述第一阻断层105的材料为氧化硅。氧化硅具有较高的工艺兼容性,有利于降低形成第一阻断层105的工艺难度和工艺成本。

124.所述开口104(如图6所示)侧壁上的所述第一阻断层105围成缝隙108,所述缝隙108的延伸方向与所述开口104的延伸方向相同。

125.需要说明的是,所述缝隙108的侧壁与所述基底法线的夹角不宜过大也不宜过小。后续所述半导体结构的形成方法还包括:去除所述第二阻断层106以及覆盖所述第二阻断层106侧壁的所述第一阻断层105,剩余的所述第一阻断层105作为阻断结构。以垂直于所述开口104的延伸方向为横向,若所述夹角过大,相应的形成在所述缝隙108中的第二阻断层106顶部的横向尺寸过大,因为所述第二阻断层106的耐刻蚀度高于所述第一阻断层105的耐刻蚀度,因此,后续去除所述第二阻断层106的难度较大,易导致形成的阻断结构的中间区域过高于所述阻断结构的边缘区域。若所述夹角过小,形成所述第二阻断层106的反应气体不易进入所述缝隙108中,从而在所述缝隙108中形成第二阻断层106的难度较大,导致所述第二阻断层106的形成质量不佳,进而在刻蚀第一阻断层105和第二阻断层106的过程中,所述第二阻断层106易过快的被去除,易导致形成的阻断结构的中间区域过低于所述阻断结构的边缘区域,因此所述阻断结构在后续过程中难以起到较好的掩膜作用。本实施例中,所述缝隙108的侧壁与所述基底法线的夹角为5

°

至10

°

。

126.需要说明的是,所述缝隙108延伸的两端还均具有两个分叉113(如图7a所示),所述分叉113不具有延伸方向。

127.所述第二阻断层106的耐刻蚀度大于所述第一阻断层105的耐刻蚀度。

128.本实施例中,所述第二阻断层106的材料为金属氧化物。所述金属氧化物具有较高的耐刻蚀性,且与介电材料具有高刻蚀选择比,在高纵横比的通孔、开口或沟槽中具有良好的填充能力。

129.具体的,所述金属氧化物包括:氧化钛、氧化钽、氧化钨、氧化钴、氧化铬、氧化矾、氧化镉、氧化铪、氧化铟、氧化铁、氧化铝、氧化锆、氧化锌和氧化镍中一种或多种。

130.本实施例中,第二阻断层106的底部高于或齐平于位于所述核心层101顶部的所述侧墙材料层102的顶面。

131.所述第二阻断层106的底端高于或齐平于位于所述核心101顶部的所述侧墙材料层102的顶面,后续刻蚀所述阻断结构材料层107形成阻断结构后,易于使得所述阻断结构的顶端高于或齐平于位于所述核心层101顶部的所述侧墙材料层102的顶面,从而有利于提高所述阻断结构顶端的平坦度。

132.本实施例所述半导体结构可以采用前述实施例所述的形成方法所形成,也可以采用其他形成方法所形成。对本实施例所述半导体结构的具体描述,可参考前述实施例中的相应描述,本实施例在此不再赘述。

133.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1