高压晶体管元件及其制作方法与流程

1.本发明涉及一种半导体元件的结构及其制作方法,特别是涉及一种高压晶体管元件及其制作方法。

背景技术:

2.负偏压温度不稳定性(negative-bias temperature instability,nbti)是影响金属氧化物半导体场效晶体管(例如,高压晶体管元件)可靠性的一个重要因素。当高压晶体管元件在高温或是高电流密度下操作中,高温或高电流密度会造成栅极和栅介电层界面的si-h键结断裂键,导致界面的陷阱电荷(dangling bond)和氧化层固定正电荷(fixed charge in oxide layer)的产生,让高压晶体管元件的临界电压产生偏移而失效,影响元件的使用寿命。一般而言,对p型金属氧化物半导体(metal-oxide-semiconductor,mos)高压晶体管元件所带来的不利影响又远高过于nmos高压晶体管元件。

3.目前已知增加栅介电层的厚度可以降低负偏压温度不稳定性的影响。然而,栅介电层的厚度与高压晶体管元件的驱动电流(drive current,ion)呈反比关系,增加栅介电层的厚度可能影响高压晶体管元件驱动电流的效能。如何降低高压晶体管元件负偏压温度不稳定性,同时兼顾元件的驱动电流效能已成为该技术领域的重要课题之一。

4.因此,有需要提供一种先进的高压晶体管元件及其制作方法,来解决现有技术所面临的问题。

技术实现要素:

5.本发明的一实施例揭露一种高压晶体管元件,包括:半导体基材、隔离结构、栅介电层、栅极、源极区以及漏极区。半导体基材具有多条凹沟,由基材表面向下延伸,而形成一个锯齿状剖面轮廓。隔离结构位于多条凹沟的外侧,并由表面向下延伸进入半导体基材之中,用于定义出一个高压区。栅介电层位于高压区上方,且部分地填充于多条凹沟之中。栅极位于栅介电层上方。源极区和漏极区分别位于半导体基材之中,且彼此隔离。

6.本发明的另一实施例揭露一种高压晶体管元件的制作方法,此方法包括下述步骤:首先,提供一个半导体基材;并以第一图案化掩模蚀刻半导体基材,形成多条凹沟,由基材表面向下延伸,而使其具有锯齿状剖面轮廓。接着,在多条凹沟的外侧形成一个隔离结构,由基材表面向下延伸进入半导体基材之中,用于定义出一个高压区。然后,以第二图案化掩模蚀刻高压区。再于高压区上方形成栅介电层,且部分地填充于多条凹沟之中;在栅介电层上方形成栅极。在半导体基材中形成源极区,,且彼此隔离。

7.根据上述实施例,本发明是在提供一种高压晶体管元件及其制作方法。在尚未以隔离结构来定义高压晶体管的通道掺杂阱区之前,利用制作其他元件(逻辑元件)的光掩模蚀刻制作工艺,以第一图案化光致抗蚀剂来蚀刻用来作为高压晶体管通道的一部分半导体基材,使其具有实质上平行通道长度方向(垂直通道宽度方向)的多条凹沟。在形成高压晶体管的通道掺杂阱区之后,再以第二图案化光致抗蚀剂,进行另一次蚀刻制作工艺,移除一

部分通道掺杂阱区,使通道掺杂阱区与栅介电层的界面具有实质上平行通道宽度方向的锯齿状结构。

8.由此,可以在不缩减栅介电层厚度的前提下,拉长高压晶体管的通道宽度,达到降低(或不诱发)元件负偏压温度不稳定性,并提高压晶体管驱动电流效能的目的。

附图说明

9.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附的附图详细说明如下:

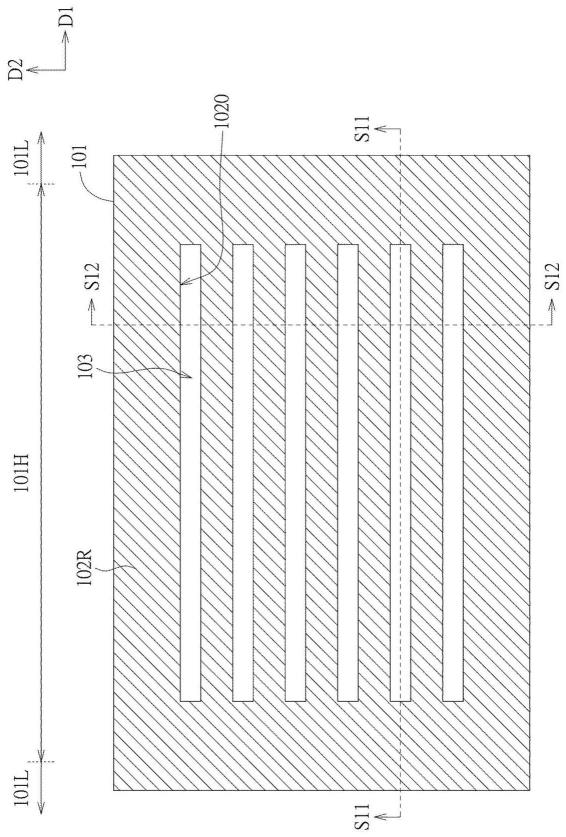

10.图1a为本发明的一实施例所绘示在半导体基材中形成多条凹沟后的半导体基材部分结构俯视示意图;

11.图1b为沿着图1a的切线s11所绘示的半导体基材部分结构剖面示意图;

12.图1c为沿着图1a的切线s12所绘示的部分结构剖面示意图;

13.图2a为在半导体基材高压区中形成隔离结构之后的部分结构俯视示意图;

14.图2b为沿着图2a的切线s21所绘示的部分结构剖面示意图;

15.图2c为沿着图2a的切线s22所绘示的部分结构剖面示意图;

16.图3a为以第二次光刻蚀刻制作工艺蚀刻高压区之后的部分结构俯视示意图;

17.图3b为沿着图3a的切线s31所绘示的部分结构剖面示意图;

18.图3c为沿着图3a的切线s32所绘示的部分结构剖面示意图;

19.图4a为本发明的一实施例所绘示的高压晶体管元件的部分结构俯视示意图;

20.图4b为沿着图4a的切线s41所绘示的部分结构剖面示意图;以及

21.图4c为沿着图4a的切线s42所绘示的部分结构剖面示意图。

22.符号说明

23.100:高压晶体管元件

24.101:半导体基材

25.101a:基材表面

26.101l:逻辑区

27.101h:高压区

28.102:第一光刻蚀刻制作工艺

29.102r:第一图案化掩模

30.102o:开口

31.103:凹沟

32.103’:凹沟

33.104:隔离结构

34.105:掺杂阱区

35.106a:高压场掺杂区

36.106b:高压场掺杂区

37.107:第二光刻蚀刻制作工艺

38.107r:第二图案化掩模

39.108:凹室

40.109:栅介电层

41.110:栅极

42.111:间隙壁

43.c:通道区

44.d1:通道长度方向

45.d2:通道宽度方向

46.h:距离

47.p:锯齿状剖面轮廓

48.pt:锯齿状剖面轮廓的顶部

49.p’:锯齿状剖面轮廓

50.pt’:锯齿状剖面轮廓的顶部

51.s11:切线

52.s12:切线

53.s21:切线

54.s22:切线

55.s31:切线

56.s32:切线

57.s41:切线

58.s42:切线

具体实施方式

59.本发明是提供一种高压晶体管元件及其制作方法,可降低高压晶体管元件负偏压温度不稳定性,同时提高元件的驱动电流效能。为了对本发明的上述实施例及其他目的、特征和优点能更明显易懂,下文特举多个实施例,并配合所附附图作详细说明。

60.但必须注意的是,这些特定的实施案例与方法,并非用以限定本发明。本发明仍可采用其他特征、元件、方法及参数来加以实施。较佳实施例的提出,仅用以例示本发明的技术特征,并非用以限定本发明的申请专利范围。该技术领域中具有通常知识者,将可根据以下说明书的描述,在不脱离本发明的精神范围内,作均等的修饰与变化。在不同实施例与附图之中,相同的元件,将以相同的元件符号加以表示。

61.高压晶体管元件100的制作方法,此方法包括下述步骤:首先,提供一个半导体基材101;并进行第一光刻蚀刻制作工艺102,以第一图案化掩模102r蚀刻半导体基材101,形成多条凹沟103,由基材表面101a向下延伸,而使其具有锯齿状剖面轮廓p。

62.请参照图1a至图1c,图1a是根据本发明的一实施例所绘示在半导体基材101中形成多条凹沟103后的半导体基材101部分结构俯视示意图。图1b是沿着图1a的切线s11所绘示的半导体基材101部分结构剖面示意图。图1c是沿着图1a的切线s12所绘示的部分结构剖面示意图。

63.在本实施例中,半导体基材101可以包括一个逻辑区101l和一个高压区101h。第一图案化掩模102r可以是一种图案化光致抗蚀剂层,同时覆盖在半导体基材101的逻辑区101l和高压区101h之中,且具有多个光致抗蚀剂图案(例如,开口102o)分别位于半导体基

材101的不同区域,至少将位于逻辑区101l和高压区101h的一部分半导体基材101暴露于外。故而,第一光刻蚀刻制作工艺102除了在高压区101h中形成多条凹沟103外,还可以在半导体基材101的其他区域(例如,逻辑区101l)中形成其他的蚀刻图案(未绘示)。

64.之后,进行一系列的中间制作工艺,在半导体基材101的其他区域中形成其他的元件结构,例如(但不以此为限)在逻辑区101l中形成多个逻辑元件(未绘示)。再于高压区101h多条凹沟103的外侧形成一个隔离结构104,使其由基材表面101a向下延伸进入半导体基材101之中,用于将高压区101h的范围定义出来。

65.请参照图2a至图2c,图2a是绘示在半导体基材101高压区101h中形成隔离结构104之后的部分结构俯视示意图。图2b是沿着图2a的切线s21所绘示的部分结构剖面示意图。图2c是沿着图2a的切线s22所绘示的部分结构剖面示意图。在本实施例中,隔离结构104可以是一种浅沟隔离结构(shallow trench isolation,sti)。且隔离结构104围绕于多条凹沟103的周边。

66.在本发明的一些实施例中,形成隔离结构104之前可以对高压区101h进行一离子注入制作工艺,用于在高压区101h中形成一个具有第一电性掺质(例如,n型掺质)的掺杂阱区105(以dnw表示),由高压区101h基材表面101a向下延伸进入半导体基材101之中。在形成隔离结构104之后,可以再对高压区101h进行另一次离子注入制作工艺,在多条凹沟103的两端分别形成具有第二电性掺质(例如,p型掺质)的二个彼此隔离的高压场(hv field)掺杂区106a和106b。在本发明的一些实施例中,高压场掺杂区106a和106b可以与多条凹沟103的两端部分重叠。

67.然后,采用第二图案化掩模107r对高压区101h进行第二次光刻蚀刻制作工艺107,移除一部分掺杂阱区105,并在高压区101中形成一凹室108时。请参照图3a至图3c,图3a是绘示以第二次光刻蚀刻制作工艺107蚀刻高压区101h之后的部分结构俯视示意图。图3b是沿着图3a的切线s31所绘示的部分结构剖面示意图。图3c是沿着图3a的切线s32所绘示的部分结构剖面示意图。

68.在本实施例中,第二图案化掩模107r以是一种图案化光致抗蚀剂层,覆盖在半导体基材101的逻辑区101l上,并将位于高压区101中由数条凹沟103所形成的锯齿状剖面轮廓p暴露于外。在尚未进行第二次光刻蚀刻制作工艺107前,锯齿状剖面轮廓p的顶部pt实质上与基材表面101a共平面(请参照图2c)。在第二次光刻蚀刻制作工艺107中,随着位于高压区101中的一部分掺杂阱区105被移除,锯齿状剖面轮廓p也会沿着蚀刻方向向下位移,而形成另一个由数条凹沟103’所构成的锯齿状剖面轮廓p’(请参照图3c)。

69.其中,锯齿状剖面轮廓p’的顶部pt’实质上会低于基材表面101a。锯齿状截面轮廓p’的顶部pt’与基材表面101a之间具有一段距离h。形成锯齿状剖面轮廓p’的每一条凹沟103’可以具有一个上宽下窄的结构;且凹沟103’的深宽比实质为1:10。

70.后续,在高压区101h上方形成栅介电层109,且部分地填充于多条凹沟103’和凹室108之中。并且分别邻接位于多条凹沟103’两侧的高压场掺杂区106a和106b。之后,再在栅介电层109上方形成栅极110。后续,在栅介电层109侧壁上形成间隙壁111,并进行一连串后段制作工艺,例如形成金属内连线结构(未绘示),完成如图4a至图4c所绘示的高压晶体管元件100的制备。

71.请参照,图4a是根据本发明的一实施例所绘示的高压晶体管元件100的部分结构

俯视示意图。图4b是沿着图4a的切线s41所绘示的部分结构剖面示意图。图4c是沿着图4a的切线s42所绘示的部分结构剖面示意图。

72.在本实施例中,高压场掺杂区106a和106b可以分别作为高压晶体管元件100的源极/漏极,具有锯齿状剖面轮廓p’的一部分掺杂阱区105与栅介电层109之间的界面,可以定义出高压晶体管元件100的通道区c。高压场掺杂区106a和106b(源极和漏极)沿着通道长度方向d1排列;锯齿状剖面轮廓p’沿着通道宽度方向d2延伸;且通道长度方向d1与通道宽度方向d2垂直。

73.由于,高压晶体管元件100的通道区c具有锯齿状剖面轮廓p’,相较于具有相同尺寸的现有高压晶体管元件(未绘示),栅介电层109在填充于多条凹沟103’中的部分具有较大的厚度,有助于改善高压晶体管元件100的负偏压温度不稳定性,延长高压晶体管元件100的使用寿命。再者,具有锯齿状剖面轮廓p’的通道区c,能实质上增加高压晶体管元件100的通道宽度,可以在不增加高压晶体管元件100的关键尺寸的前提下,提高高压晶体管元件100的驱动电流。

74.根据上述实施例,本发明是在提供一种高压晶体管元件100及其制作方法。在尚未以隔离结构104来定义高压晶体管100的通道掺杂阱区105之前,利用制作其他元件(逻辑元件)的光掩模蚀刻制作工艺,以第一图案化光致抗蚀剂102r来蚀刻用来作为高压晶体管通道的一部分半导体基材101,使其具有实质上平行通道长度d1方向(垂直通道宽度方向d2)的多条凹沟103。并在形成通道掺杂阱区105之后,以第二图案化光致抗蚀剂107r进行另一次蚀刻制作工艺107,移除一部分通道掺杂阱区105,使通道掺杂阱区105与栅介电层109的界面具有实质上平行通道宽度方向d2的锯齿状结构p’。

75.由此,可以在不缩减栅介电层109厚度的前提下,拉长高压晶体管元件100的通道宽度,达到降低(或不诱发)高压晶体管元件负偏压温度不稳定性,并提高压晶体管驱动电流效能的目的。

76.虽然结合以上优选实施例揭露了本发明,然而其并非用以限定本发明,任何该技术领域中具有通常知识者,在不脱离本发明的精神和范围内,可作些许的更动与润饰,因此本发明的保护范围应当以附上的权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1