半导体结构的制作方法

1.本公开涉及半导体结构,尤其涉及一种包含碳基层(carbon-based layer)的半导体结构。

背景技术:

2.一些电子装置,例如处理器、记忆装置或其他类型的电子装置,包括将位于前段工艺(front end of line,feol)区中的晶体管电性连接到后段工艺(back end of line,beol)区的中段工艺(middle end of line,meol)区。meol区可以包括形成于介电层中的介电层与接触插塞(也被称为接触导孔)。接触插塞可以电性连接feol区的源极/漏极区与金属栅极。接触插塞可以包括一或多个金属,例如钨、钴、钌、或铜。

技术实现要素:

3.一种半导体结构,包括:第一金属结构,在第一氧化层内邻近第一虚置金属结构;第二氧化层,沉积于第一氧化层上方;第二金属结构,沉积于第一金属结构上以及第二氧化层内;以及碳基层,沉积于第一虚置金属结构的顶表面上。

4.一种半导体结构的形成方法,包括:在第一金属结构的顶表面上沉积碳基层;在第一金属结构上方的凹槽的多个侧壁上直接沉积阻挡层;以及在第一金属结构上、凹槽内以及侧壁之间沉积第二金属结构。

5.一种半导体结构,包括:第一金属结构;第二金属结构,沉积于第一金属结构上且在金属界面与第一金属结构交界;以及碳基层,位于金属界面。

附图说明

6.以下将配合所附附图详述本发明实施例。应注意的是,依据在业界的标准做法,各种特征并未按照比例绘制且仅用以说明例示。事实上,可任意地放大或缩小元件的尺寸,以清楚地表现出本发明实施例的特征。

7.图1是范例环境的图,其中可以实施在此描述的系统及/或方法。

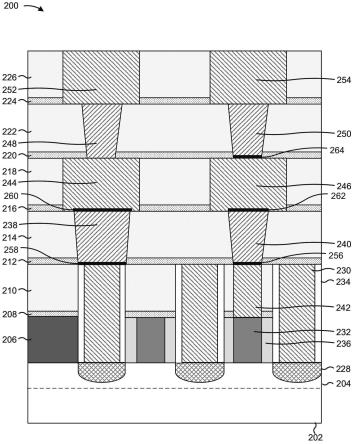

8.图2是在此描述的范例半导体结构的图。

9.图3是在此描述的范例半导体结构的三维图。

10.图4a~图4g是在此描述的范例实施方式的图。

11.图5a~图5h是在此描述的范例实施方式的图。

12.图6a~图6f是在此描述的范例实施方式的图。

13.图7a~图7g是在此描述的范例实施方式的图。

14.图8是在此描述的图1的一或多个装置的范例组件的图。

15.图9是与形成在此描述的半导体结构相关的范例工艺的流程图。

16.附图标记如下:

17.100:范例环境(环境)

18.102:沉积工具

19.104:曝光工具

20.106:显影工具

21.108:蚀刻工具

22.110:平坦化工具

23.112:镀覆工具

24.114:光刻胶移除工具

25.116:芯片/裸片运输工具

26.200,300:范例装置(装置)

27.202:基板

28.204:鳍片结构

29.206,210,214,218,222,226:介电层

30.208,212,216,220,224:蚀刻停止层

31.228:外延区

32.230:金属源极或漏极接触件(源极或漏极接触件,金属源极/漏极)

33.232:栅极

34.234,236:间隔物

35.238,240:内连线

36.240a:接触插塞

37.240b:虚置接触插塞

38.242:栅极接触件

39.244,246:导电结构

40.246a:金属化层

41.246b:虚置接触插塞(虚置金属化层)

42.248,250:导孔

43.252,254:导电结构

44.256,258,260,262,264,312,262a,262b:碳基层

45.302,304,306,308,310:虚置栅极接触件

46.400,500,600,700:范例实施方式

47.402,406,606:阻挡层

48.404,604:凹槽

49.800:装置

50.810:总线

51.820:处理器

52.830:存储器

53.840:输入组件

54.850:输出组件

55.860:通信组件

56.900:范例工艺(工艺)

57.910,920,930:步骤

具体实施方式

58.以下公开提供了许多的实施例或范例,用于实施所提供的不同元件。各元件和其配置的具体范例描述如下,以简化本发明实施例的说明。当然,这些仅仅是范例,并非用以限定本发明实施例。举例而言,叙述中若提及第一元件形成在第二元件之上,可能包含第一和第二元件直接接触的实施例,也可能包含额外的元件形成在第一和第二元件之间,使得它们不直接接触的实施例。此外,本发明实施例可能在各种范例中重复参考数值以及/或字母。如此重复是为了简明和清楚的目的,而非用以表示所讨论的不同实施例及/或配置之间的关系。

59.再者,其中可能用到与空间相对用词,例如“在

……

之下”、“下方”、“较低的”、“上方”、“较高的”等类似用词,是为了便于描述附图中一个(些)部件或特征与另一个(些)部件或特征之间的关系。空间相对用词用以包括使用中或操作中的装置的不同方位,以及附图中所描述的方位。当装置被转向不同方位时(旋转90度或其他方位),其中所使用的空间相对形容词也将依转向后的方位来解释。

60.在一些情况下,meol区可以将电子装置的feol区中的半导体结构电性连接到电子装置的beol区。meol区可以包括介电层与形成于介电层中的接触插塞(也被称为接触导孔)。接触插塞可以电性连接到feol区的源极或漏极区与金属栅极。因此,接触插塞可以包括金属(例如,铜(cu)、钴(co)、钌(ru)、或其他金属),使得接触插塞在金属界面连接到源极或漏极接触件(或连接到栅极接触件)。beol区可以将meol区的接触插塞电性连接到内连线或其他导电结构(例如:金属化层,也被称为导线;或导孔)。金属化层(例如,铜、钴、钌、或其他金属)可以在金属界面彼此接触(或接触接触插塞)。

61.由于相对于其他导电材料(例如铝(al))具有较低的接触电阻及片电阻,铜经常用于beol金属化层及导孔(或用于meol接触插塞)。较低的电阻率提供较低的电阻/电容(resistance/capacitance,rc)时间常数以及较快的横跨电子装置的信号传输。然而,铜也具有较高的扩散(或电迁移)速率,其能够造成铜离子扩散到周围的介电材料。这个扩散造成beol金属化层及导孔(或meol接触插塞)的电阻率增加,可能会导致电子装置的电气性能降低。此外,扩散可能会导致铜离子迁移到其他meol层及/或feol层,可能会造成半导体装置的失效(failures)并降低制造产率。

62.当金属界面是使用不同的金属(例如,用于一区域的例如铜的第一金属以及用于另一区域的例如钴的第二金属)所形成时,在第一金属上沉积第二金属时的从第二金属到第一金属的热传递可能会造成第二金属的不对称沉积。这个不对称导致气穴(air pockets)或其他不规则(irregularities)产生于金属界面,增加位于金属界面的接触电阻。增加的接触电阻可能会降低电子装置的电气性能。

63.因此,可以沉积阻挡层(例如氮化钛(tin)、氮化钽(tan)及/或其他类型的阻挡层)以防止扩散。当在第一金属上沉积第二金属时,这些阻挡层也能够帮助防止从第二金属到第一金属的热传递。然而,当阻挡层沉积于金属界面时会增加接触电阻,又再降低了电子装置的电气性能。

64.在此描述的一些实施方式在金属界面(例如,meol内连线与栅极接触件或源极或

漏极区接触件之间、meol接触插塞与beol金属化层之间及/或beol导电结构之间的金属界面)提供一层石墨或石墨烯以替代阻挡层。因为石墨及石墨烯具有明显低于阻挡层的电阻,接触电阻降低,提高了电子装置的电气性能。

65.此外,在一些实施方式中,当第二金属沉积于第一金属时,石墨或石墨烯可以帮助防止从第二金属到第一金属的热传递。这导致了第二金属的更对称的沉积,进一步降低了位于金属界面的接触电阻。作为替代,在一些实施方式中,在第二金属的沉积之前,蚀刻石墨或石墨烯的膜层以进一步降低位于金属界面的接触电阻。

66.图1是范例环境100的图,其中可以实施在此描述的系统及/或方法。范例环境100包括半导体处理工具,其能够用于形成半导体结构及装置,例如在此描述的包括石墨或石墨烯衬层的半导体结构或装置。

67.如图1所示,环境100可以包括多个半导体处理工具102~114以及芯片/裸片(die)运输工具116。多个半导体处理工具102~114可以包括沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆(plating)工具112、光刻胶移除工具114及/或其他半导体处理工具。范例环境100所包括的工具可以被包括在半导体无尘室、半导体工厂(foundry)、半导体处理及/或制造设施、或其他地点中。

68.沉积工具102是一个半导体处理工具,包括半导体处理室(processing chamber)以及能够将各种类型的材料沉积到基板上的一或多个装置。在一些实施方式中,沉积工具102包括能够在例如芯片的基板上沉积光刻胶层的旋转涂布工具。在一些实施方式中,沉积工具102包括化学气相沉积(chemical vapor deposition,cvd)工具,例如等离子体辅助cvd(plasma-enhanced cvd,pecvd)工具、高密度等离子体cvd(high-density plasma cvd,hdp-cvd)工具、次常压cvd(sub-atmospheric cvd,sacvd)工具、原子层沉积(atomic layer deposition,ald)工具、等离子体辅助原子层沉积(plasma-enhanced atomic layer deposition,peald)工具、或其他类型的cvd工具。在一些实施中,沉积工具102包括物理气相沉积(physical vapor deposition,pvd)工具,例如溅镀工具或其他类型的pvd工具。在一些实施方式中,范例环境100包括多个类型的沉积工具102。

69.曝光工具104是一个半导体处理工具,能够将光刻胶层曝光于辐射源(radiation source),例如紫外光(ultraviolet light,uv)源(例如,深紫外光(deep uv)源、极紫外光(extreme uv,euv)源及/或类似紫外光源)、x射线源、电子束(electron beam,e-beam)源及/或其他类型的曝光工具。曝光工具104可以将光刻胶层曝光于辐射源以将图案从光掩膜转移到光刻胶层。图案可以包括用于形成一或多个半导体装置的一或多个半导体装置膜层图案、可以包括用于形成一或多个半导体装置的结构的图案、可以包括用于蚀刻半导体装置的各种部分的图案及/或类似图案。在一些实施方式中,曝光工具104包括扫描器(scanner)、步进机(stepper)、或类似类型的曝光工具。

70.显影工具106是一个半导体处理工具,能够显影已曝光于辐射源的光刻胶层以显影从曝光工具104转移到光刻胶层的图案。在一些实施方式中,显影工具106通过移除光刻胶层的未曝光的部分以显影图案。在一些实施方式中,显影工具106通过移除光刻胶层的已曝光的部分以显影图案。在一些实施方式中,显影工具106通过使用化学显影剂,通过溶解光刻胶层的已曝光或未曝光的部分以显影图案。

71.蚀刻工具108是一个半导体处理工具,能够蚀刻基板、芯片、或半导体装置的各种

random access memory,dram)、逻辑装置、处理器、输入/输出装置、或其他类型的半导体装置的范例,其包括一或多个晶体管。

78.装置200包括在基板202上图案化的鳍片结构204。装置200还包括一或多个堆叠的膜层,其中一个范例为包括介电层206、蚀刻停止层(etch stop layer,esl)208、介电层210、蚀刻停止层212、介电层214、蚀刻停止层216、介电层218、蚀刻停止层220、介电层222、蚀刻停止层224及介电层226。包括介电层206、210、214、218、222及226以电性隔离装置200的各种结构。介电层206、210、214、218、222及226包括氮化硅(sinx)、氧化物(例如,氧化硅(siox)及/或其他氧化物材料)及/或其他类型的介电材料。因此,介电层206、210、214、218、222及226也可以被称为氧化层。蚀刻停止层208、212、216、220及224包括一层材料,其被配置为允许装置200的各个部分(或其中包括的膜层)被选择性蚀刻或被保护免于蚀刻以形成一或多个包括在装置200中的结构。

79.进一步如图2所示,装置200包括多个外延(epitaxial,epi)区,其在部分的鳍片结构204上及/或周围成长及/或以其他方式形成。外延区228是由外延成长所形成。在一些实施方式中,外延区228形成于鳍片结构204中的凹陷的部分。凹陷的部分可以通过鳍片结构204的应变源极漏极(strained source drain,ssd)蚀刻及/或其他类型的蚀刻操作来形成。外延区228用作包括在装置200中的晶体管的源极/漏极区。

80.外延区228电性连接到包括在装置200中的晶体管的金属源极或漏极接触件230。金属源极或漏极接触件(mds或cas)230包括钴(co)、钌(ru)及/或其他导电或金属材料。晶体管还包括栅极232(mgs),其由多晶硅材料、金属(例如,钨(w)或其他金属)及/或其他类型的导电材料所形成。金属源极或漏极接触件230与栅极232被一或多个侧壁间隔物电性隔离,包括在金属源极或漏极接触件230的每一侧的间隔物234以及在栅极232的每一侧的间隔物236。间隔物234与236可以包括氧化硅(siox)、氮化硅(sixny)、碳氧化硅(silicon oxy carbide,sioc)、氮氧化碳硅(silicon oxycarbonitride,siocn)及/或其他适合的材料。在一些实施方式中,在源极或漏极接触件230的侧壁省略间隔物234。

81.进一步如图2所示,金属源极/漏极接触件230与栅极232电性连接到一或多个类型的内连线。内连线电性连接装置200的晶体管及/或将晶体管电性连接到装置200的其他区域及/或组件。在一些实施方式中,内连线将晶体管电性连接到装置200的后段工艺(beol)区。

82.一或多个金属源极或漏极接触件230电性连接到源极/漏极内连线238(例如,源极/漏极导孔或vds)。一或多个栅极232电性连接到栅极内连线240(例如,栅极导孔或vgs)。内连线238与240包括导电材料,例如钨、钴、钌、铜及/或其他类型的导电材料。在一些实施方式中,栅极232通过栅极接触件242(cb或mp)电性连接到栅极内连线240以降低栅极232与栅极内连线240之间的接触电阻。栅极接触件242包括钨(w)、钴(co)、钌(ru)、钛(ti)、铝(al)、铜(cu)或金(au)以及导电材料的其他范例。

83.进一步如图2所示,内连线238及240电性连接到多个beol层,分别包括一或多个金属化层及/或导孔。作为一个范例,内连线238及240可以电性连接到包括导电结构244及246的m0金属化层。m0金属化层电性连接到包括导孔248及250的v0导孔层。v0导孔层电性连接到包括导电结构252及254的m1金属化层。在一些实施方式中,装置200的beol层可以包括将装置200连接到封装体(package)的额外的金属化层及/或导孔。

84.进一步如图2所示,装置200包括一或多个碳基层以降低在装置200的金属界面的接触电阻。在一些实施方式中,碳基层为石墨烯(例如,二维碳结构)或石墨(例如,三维碳结构)。碳基层可以具有从约1纳米(nm)到约5nm的深度。通过选择至少1nm的深度,在对应的蚀刻停止层的外延成长时,碳基层被对应的蚀刻停止层(例如,蚀刻停止层212、蚀刻停止层216、蚀刻停止层220、或其他蚀刻停止层)保护而不会过度成长。防止对应的蚀刻停止层的外延过度成长降低了在碳基层的接触电阻。选择至少1nm的深度也防止了热传递,导致金属在碳基层的上方更对称地沉积,并进一步降低接触电阻。通过选择不超过5nm的深度,碳基层将不显著地增加接触电阻。如果碳基层被蚀刻(例如,如图5g及图7f所更详细地描述),选择不超过5nm的深度也减少了时间、功率及化学品的消耗量。

85.装置200可以在栅极接触件242与内连线240(也被称为接触插塞240)之间的金属界面包括碳基层256。在一些实施方式中,可以如图4a~图4g所述地沉积碳基层256。图4a~图4g所述的实施方式通过使用碳基层256以在沉积内连线240时防止热传递,降低了在金属界面的表面粗糙度。作为替代,可以如图5a~图5h所述地沉积碳基层256。如图5a~图5h所述的实施方式通过在沉积内连线240之前蚀刻碳基层256,进一步降低了在金属界面的接触电阻。

86.此外,或替代地,装置200可以在金属源极或漏极接触件230与内连线238(也被称为接触插塞238)之间的金属界面包括碳基层258。在一些实施方式中,可以与图4a~图4g所述类似地沉积碳基层258。图4a~图4g所述的实施方式通过使用碳基层258以在沉积内连线时防止热传递,降低了在金属界面的表面粗糙度。作为替代,可以与图5a~图5h所述类似地沉积碳基层258。图5a~图5h所述的实施方式通过在沉积内连线240之前蚀刻碳基层,进一步降低了在金属界面的接触电阻。

87.此外,或替代地,装置200可以在内连线238(与金属源极或漏极接触件230相关联)与导电结构244(也被称为金属化层244)之间的金属界面包括碳基层260。在一些实施方式中,可以与图6a~图6f所述类似地沉积碳基层260。图6a~图6f所述的实施方式通过使用碳基层260以在沉积导电结构244时防止热传递,降低了在金属界面的表面粗糙度。作为替代,可以如图7a~图7g所述类似地沉积碳基层260。图7a~图7g所述的实施方式通过在沉积导电结构244之前蚀刻碳基层260,进一步降低了在金属界面的接触电阻。

88.此外,或替代地,装置200可以在内连线240(与栅极接触件242相关联)与导电结构246(也被称为金属化层246)之间的金属界面包括碳基层262。在一些实施方式中,可以与图6a~图6f所述类似地沉积碳基层262。图6a~图6f所述的实施方式通过使用碳基层262以在沉积导电结构246时防止热传递,降低了在金属界面的表面粗糙度。作为替代,可以如图7a~图7g所述地沉积碳基层260。图7a~图7g所述的实施方式通过在沉积导电结构246之前蚀刻碳基层262,进一步降低了在金属界面的接触电阻。

89.此外,或替代地,装置200可以在导电结构246与导孔250之间的金属界面包括碳基层264。在一些实施方式中,可以与图6a~图6f所述类似地沉积碳基层264。图6a~图6f所述的实施方式通过使用碳基层264以在沉积导孔250时防止热传递,降低了在金属界面的表面粗糙度。作为替代,可以如图7a~图7g所述类似地沉积碳基层264。图7a~图7g所述的实施方式通过在沉积导孔250之前蚀刻碳基层264,进一步降低了在金属界面的接触电阻。

90.此外,或替代地,装置200可以在导电结构244与导孔248之间、导孔248与导电结构

252(也被称为金属化层252)之间及/或导孔250与导电及够254(也被称为金属化层254)之间的金属界面包括碳基层。

91.如上所述,提供图2以作为范例。其他范例可以与图2所述的范例不同。

92.图3是在此描述的范例装置300的一部分的三维图。举例而言,装置300可以包括图2的装置200的至少一部分。

93.如图3所示,栅极接触件242可以在栅极接触件242的顶表面与接触插塞240的底表面之间的金属界面包括碳基层256。与图2类似,栅极接触件242形成于氧化层210中,且接触插塞240形成于氧化层214中。在氧化层210及214之间有一或多个蚀刻停止层,例如蚀刻停止层212。

94.进一步如图3所示,装置300包括多个虚置栅极接触件302、304、306、308及310。如图3所示,虚置栅极接触件302、304、306、308及310并未电性连接到接触插塞240。因此,在虚置栅极接触件302、304、306、308及310上方的部分的接触插塞240可以用作虚置接触插塞。然而,虚置栅极接触件302、304、306、308及310可以包括对应的碳基层,例如在虚置栅极接触件302、304、306、308及310的顶表面的碳基层312。举例而言,可以如图6a~图6f或如图7a~图7g所述地沉积碳基层。

95.尽管如栅极接触件242及接触插塞240所述,上述描述可类似地应用于其他金属界面。举例而言,装置300可以在金属源极或漏极接触件230与接触插塞238之间包括界面,且包括在顶表面上具有碳基层的多个虚置金属源极或漏极接触件。此外,或替代地,装置300可以在接触插塞240(或接触插塞238)与金属化层246(或金属化层244)之间包括界面,且包括在顶表面上具有碳基层的多个虚置接触插塞。此外,或替代地,装置300可以在金属化层246(或金属化层244)与导孔250(或导孔248)之间包括界面,且包括在顶表面上具有碳基层的多个虚置金属化层。此外,或替代地,装置300可以在导孔250(或导孔248)与金属化层254(或金属化层252)之间包括界面,且包括在顶表面上具有碳基层的多个虚置导孔。

96.尽管如单一的接触插塞240所述,且接触插塞240包括用作虚置接触插塞的部分,上述描述可类似地应用于虚置栅极接触件上方的虚置接触插塞。举例而言,多个虚置接触插塞可以包括如图6a~图6f或图7a~图7g所述地沉积的虚置接触插塞246b。

97.如上所述,提供图3以作为范例。其他范例可以与图3所述的范例不同。

98.图4a~图4g是在此描述的范例实施方式400的图。范例实施方式400可以是用于形成碳基层256的范例工艺。碳基层256降低了接触电阻,提高了电子装置的电气性能。此外,碳基层256在将内连线240沉积在栅极接触件242上时帮助防止热传递。这导致了内连线240的更对称的沉积,进一步降低了接触电阻。可以类似地使用范例实施方式400以在金属源极/或漏极接触件230与内连线238之间形成碳基层258。

99.如图4a所示,用于形成内连线240的范例工艺可以与feol一起进行。在一些实施方式中,feol包括在氧化层210内形成于栅极232上的栅极接触件242。此外,feol可以包括形成于氧化层210中的一或多个金属源极或漏极接触件230。如图4a所示,金属源极或漏极接触件230可以包括间隔物234。在一些实施方式中,栅极232可以额外地包括间隔物236。

100.在一些实施方式中,栅极接触件242可以(例如,在侧壁及/或底表面上)被阻挡层402围绕。举例而言,阻挡层402可以包括氮化物,例如氮化钛(tin)或氮化钽(tan)。在一些实施方式中,阻挡层402可以具有从约1nm到约3nm的厚度。通过选择至少1nm的厚度,能够防

止来自栅极接触件242的金属(例如,铜)的扩散,降低栅极接触件242的电阻率并防止包括栅极接触件242的电气装置的失效。选择不超过3nm的厚度可降低由阻挡层402造成的接触电阻。

101.如图4b所示,可以在栅极接触件242与金属源极或漏极接触件230上形成蚀刻停止层212。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术来沉积蚀刻停止层212。平坦化工具110可以在沉积蚀刻停止层212之后平坦化蚀刻停止层212。

102.在一些实施方式中,蚀刻停止层212可以具有从约1nm到约3nm的厚度。通过选择至少1nm的厚度,蚀刻停止层212能够具有防止蚀刻停止层212上方的膜层的过度蚀刻的功能。选择不超过3nm的厚度能够防止蚀刻停止层212阻碍蚀刻停止层212上方的膜层的图案化(例如,如图4d所述的图案化)。

103.如图4c所示,可以在金属源极/漏极230上形成氧化层214(也被称为介电层214)。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术来沉积氧化层214。平坦化工具110可以在沉积氧化层214之后平坦化氧化层214。

104.如图4d所示,可以蚀刻氧化层214以形成开口(形成凹槽404),使得栅极接触件242至少部分露出。举例而言,沉积工具102可以在氧化层214上形成光刻胶层(或在氧化层214上形成蚀刻停止层,例如蚀刻停止层216),曝光工具104可以将光刻胶层曝光于辐射源以图案化光刻胶层,显影工具106可以显影并移除部分的光刻胶层以露出图案,且蚀刻工具108可以蚀刻部分的氧化层214以形成凹槽404。在一些实施方式中,光刻胶移除工具114在蚀刻工具108(例如,使用化学剥除剂、等离子体灰化机(plasma asher)及/或其他技术)移除凹槽404之后移除光刻胶层的剩余部分。

105.尽管在此描述关于在栅极接触件242上方的氧化层214中形成凹槽404,上述描述可类似地应用于在一或多个金属源极或漏极接触件230上方的氧化层214中形成凹槽404。

106.如图4e所示,可以在栅极接触件242上形成碳基层256。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术来沉积碳基层256。在一些实施方式中,将碳基层256选择性地沉积在栅极接触件242上,但不沉积在凹槽404的侧壁上。举例而言,可以使用与金属反应(因此与栅极接触件242反应)但不与介电材料反应(因此不与氧化层214反应)的有机前驱材料以沉积碳基层256。

107.在一些实施方式中,碳基层256可以具有从约1nm到约5nm的厚度。通过选择至少1nm的厚度,碳基层256防止阻挡层406(如图4f所述)形成于栅极接触件242上。防止阻挡层406沉积在栅极接触件242上降低了在栅极接触件242的接触电阻。选择至少1nm的厚度也在沉积内连线240时防止了热传递(如图4g所述),导致内连线240的更对称的沉积,进一步降低了接触电阻。通过选择不超过5nm的厚度,碳基层256不显著增加栅极接触件242的接触电阻。

108.尽管在此描述关于在栅极接触件242上形成碳基层256,上述描述可类似地应用于在一或多个金属源极或漏极接触件230上形成碳基层258。

109.如图4f所示,阻挡层406可以形成于凹槽404的侧壁上(且在一些实施方式中,至少形成于一部分的氧化层214上)。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术来沉积阻挡层406。在一些实施方式中,将阻挡层406选择性地沉积在凹槽404的侧壁上,但不沉积在碳基层256上。举例而言,可以使用与电介质反应(因此与氧化层

214反应)但不与有机材料反应(因此不与碳基层256反应)的前驱材料以沉积阻挡层406。通过防止阻挡层406形成于栅极接触件242上,碳基层256降低了在栅极接触件242的接触电阻。平坦化工具110可以在沉积阻挡层406之后平坦化至少一部分的阻挡层406。

110.如图4g所示,可以在凹槽404中以及碳基层256上形成内连线240。沉积工具102可以使用cvd技术、pvd技术、ald技术、或其他类型的沉积技术沉积内连线240的材料,镀覆工具112可以使用电镀操作、或前述的组合沉积内连线240的材料。平坦化工具110可以在沉积内连线240之后平坦化内连线240。碳基层256在沉积内连线240时帮助防止热扩散,造成内连线240的更对称的沉积并在栅极接触件242与内连线240之间的金属界面降低表面粗糙度。降低表面粗糙度降低了在金属界面的接触电阻。

111.尽管在此描述关于在栅极接触件242上的碳基层256上形成内连线240,上述描述可应用于在一或多个金属源极或漏极接触件230上的碳基层258上形成内连线238。

112.通过使用结合图4a~图4g所述的技术,阻挡层406防止了来自内连线240的金属(例如,铜)的扩散,降低了内连线240的电阻率并防止包括内连线240的电气装置的失效。此外,碳基层256防止了在栅极接触件242与内连线240之间的金属界面的接触电阻。

113.如上所述,提供图4a~图4g以作为一或多个范例。其他范例可以与图4a~图4g所述的范例不同。举例而言,在一些实施方式中,与图6a~图6f及图7a~图7g所述类似地,在氧化层210内的虚置栅极接触件及/或虚置金属源极或漏极接触件上形成额外的碳基层。举例而言,可以在沉积蚀刻停止层212与氧化层214之前形成碳基层256,使得碳(例如,以石墨烯或石墨的形式)也沉积在不接触形成于氧化层214中的内连线的虚置结构上。

114.图5a~图5h是在此描述的范例实施方式500的图。范例实施方式500可以是用于形成碳基层256的范例工艺。碳基层256降低了接触电阻,增加了电子装置的电气性能。此外,在将内连线240沉积在栅极接触件242之前蚀刻碳基层256,进一步降低接触电阻。范例实施方式500可以类似地用于在金属源极或漏极接触件230与内连线238之间形成碳基层258。

115.如图5a所示,用于形成内连线240的饭粒工艺可以与feol一起进行。在一些实施方式中,feol包括在氧化层210内的栅极232上形成的栅极接触件242。此外,feol可以包括形成于氧化层210中的一或多个金属源极或漏极接触件230。如图5a所示,金属源极或漏极接触件230可以包括间隔物234。在一些实施方式中,栅极232可以额外地包括间隔物236。

116.在一些实施方式中,栅极接触件242可以(例如,在侧壁即/或底表面上)被阻挡层402围绕。举例而言,阻挡层402可以包括氮化物,例如氮化钛(tin)或氮化钽(tan)。在一些实施方式中,阻挡层402可以具有从约1nm到约3nm的厚度。通过选择至少1nm的厚度,能够防止来自栅极接触件242的金属(例如,铜)的扩散,降低栅极接触件242的电阻率并防止包括栅极接触件242的电气装置的失效。选择不超过3nm的厚度可降低由阻挡层402造成的接触电阻。

117.如图5b所示,可以在栅极接触件242与金属源极或漏极接触件230上形成蚀刻停止层212。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术来沉积蚀刻停止层212。平坦化工具110可以在沉积蚀刻停止层212之后平坦化蚀刻停止层212。

118.在一些实施方式中,蚀刻停止层212可以具有从约1nm到约3nm的厚度。通过选择至少1nm的厚度,蚀刻停止层212能够具有防止蚀刻停止层212上方的膜层的过度蚀刻的功能。选择不超过3nm的厚度能够防止蚀刻停止层212阻碍蚀刻停止层212上方的膜层的图案化

(例如,如图5d所述的图案化)。

119.如图5c所示,可以在金属源极/漏极230上形成氧化层214(也被称为介电层214)。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术来沉积氧化层214。平坦化工具110可以在沉积氧化层214之后平坦化氧化层214。

120.如图5d所示,可以蚀刻氧化层214以形成开口(形成凹槽404),使得栅极接触件242至少部分露出。举例而言,沉积工具102可以在氧化层214上形成光刻胶层(或在氧化层214上形成蚀刻停止层,例如蚀刻停止层216),曝光工具104可以将光刻胶层曝光于辐射源以图案化光刻胶层,显影工具106可以显影并移除部分的光刻胶层以露出图案,且蚀刻工具108可以蚀刻部分的氧化层214以形成凹槽404。在一些实施方式中,光刻胶移除工具114在蚀刻工具108(例如,使用化学剥除剂、等离子体灰化机及/或其他技术)移除凹槽404之后移除光刻胶层的剩余部分。

121.尽管在此描述关于在栅极接触件242上方的氧化层214中形成凹槽404,上述描述可类似地应用于在一或多个金属源极或漏极接触件230上方的氧化层214中形成凹槽404。

122.如图5e所示,可以在栅极接触件242上形成碳基层256。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术来沉积碳基层256。在一些实施方式中,将碳基层256选择性地沉积在栅极接触件242上,但不沉积在凹槽404的侧壁上。举例而言,可以使用与金属反应(因此与栅极接触件242反应)但不与介电材料反应(因此不与氧化层214反应)的有机前驱材料以沉积碳基层256。

123.在一些实施方式中,碳基层256可以具有从约1nm到约5nm的厚度。通过选择至少1nm的厚度,碳基层256防止阻挡层406(如图5f所述)形成于栅极接触件242上。防止阻挡层406沉积在栅极接触件242上降低了在栅极接触件242的接触电阻。通过选择不超过5nm的厚度,减少了用于蚀刻碳基层256(如图5g所述)的时间、功率及化学品的消耗量。

124.尽管在此描述关于在栅极接触件242上形成碳基层256,上述描述可类似地应用于在一或多个金属源极或漏极接触件230上形成碳基层258。

125.如图5f所示,阻挡层406可以形成于凹槽404的侧壁上(且在一些实施方式中,至少形成于一部分的氧化层214上)。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术来沉积阻挡层406。在一些实施方式中,将阻挡层406选择性地沉积在凹槽404的侧壁上,但不沉积在碳基层256上。举例而言,可以使用与电介质反应(因此与氧化层214反应)但不与有机材料反应(因此不与碳基层256反应)的前驱材料以沉积阻挡层406。通过防止阻挡层406形成于栅极接触件242上,碳基层256降低了在栅极接触件242的接触电阻。平坦化工具110可以在沉积阻挡层406之后平坦化至少一部分的阻挡层406。

126.如图5g所示,可以蚀刻碳基层256。举例而言,蚀刻工具108可以使用与有机材料反应(因此与碳基层256反应)但不与无机材料反应(因此不与阻挡层406与栅极接触件242反应)的一或多个蚀刻剂。进一步如图5g所示,一部分的碳基层256可以留在阻挡层406与栅极接触件242之间。

127.如图5h所示,可以在凹槽404中以及栅极接触件242上形成内连线240。沉积工具102可以使用cvd技术、pvd技术、ald技术、或其他类型的沉积技术沉积内连线240的材料,镀覆工具112可以使用电镀操作、或前述的组合沉积内连线240的材料。平坦化工具110可以在沉积内连线240之后平坦化内连线240。因为碳基层256被蚀刻,进一步降低了在内连线240

与栅极接触件242之间的金属界面的接触电阻。

128.尽管在此描述关于在栅极接触件242上形成内连线240,上述描述可类似地应用于在一或多个金属源极或漏极接触件230上形成内连线238。

129.通过使用结合图5a~图5h所述的技术,阻挡层406防止了来自内连线240的金属(例如,铜)的扩散,降低了内连线240的电阻率并防止包括内连线240的电气装置的失效。此外,碳基层256防止了碳基层406在内连线240与栅极接触件242之间的金属界面的沉积,降低了在金属界面的接触电阻。碳基层256也在沉积内连线240之前被蚀刻以进一步降低在金属界面的接触电阻。

130.如上所述,提供图5a~图5h以作为一或多个范例。其他范例可以与图5a~图5h所述的范例不同。举例而言,在一些实施方式中,与图6a~图6f及图7a~图7g所述类似地,在氧化层210内的虚置栅极接触件及/或虚置金属源极或漏极接触件上形成额外的碳基层。举例而言,可以在沉积蚀刻停止层212与氧化层214之前形成碳基层256,使得碳(例如,以石墨烯或石墨的形式)也沉积在不接触形成于氧化层214中的内连线的虚置结构上。

131.图6a~图6f是在此描述的范例实施方式600的图。范例实施方式600可以是用于形成碳基层262的范例工艺。碳基层262降低了接触电阻,增加了电子装置的电气性能。此外,碳基层262在将金属化层246沉积于接触插塞240上时帮助防止热传递。这导致了金属化层246的更对称的沉积,进一步降低接触电阻。范例实施方式600可以类似地用于在金属化层244与接触插塞238之间形成碳基层260、在导孔248与金属化层244之间形成碳基层及/或在导孔250与金属化层246之间形成碳基层264。

132.如图6a所示,用于形成金属化层246的范例工艺可以与feol一起进行。在一些实施方式中,feol包括在氧化层210内的栅极232上形成的栅极接触件242。此外,feol可以包括形成于氧化层210中的一或多个金属源极或漏极接触件230。如图6a所示,金属源极或漏极接触件230可以包括间隔物234,且栅极232可以包括间隔物236。在一些实施方式中,进一步如图6a所示,在氧化层210与间隔物236之间沉积蚀刻停止层208。在一些实施方式中,如结合图4a~图4g及图5a~图5h所述,栅极接触件242被阻挡层围绕。

133.进一步如图6a所示,用于形成金属化层246的范例工艺可以与meol一起进行。在一些实施方式中,meol包括形成于氧化层214内的栅极接触件242上的接触插塞240a。在一些实施方式中,如结合图4a~图4g及图5a~图5h所述,接触插塞240a被阻挡层围绕及/或在碳基层256与栅极接触件242交界。

134.在一些实施方式中,进一步如图6a所示,在氧化层214与氧化层210之间沉积蚀刻停止层212。此外,meol可以包括一或多个虚置结构,例如虚置接触插塞240b。如图6a所示,虚置接触插塞240b不电性连接到栅极接触件或金属源极或漏极接触件。

135.如图6b所示,碳基层262a可以形成于接触插塞240a上,且碳基层262b可以形成于虚置接触插塞240b上。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术以沉积碳基层262a及262b。在一些实施方式中,将碳基层262a及262b选择性沉积在接触插塞240a及虚置接触插塞240b上,但不沉积在氧化层214上。举例而言,可以使用与金属反应(因此与接触插塞240a及虚置接触插塞240b反应)但不与介电材料反应(因此不与氧化层214反应)的有机前驱材料沉积碳基层262a及262b。

136.在一些实施方式中,碳基层262a(且类似地碳基层262b)可以具有从约1nm到约5nm

的厚度。通过选择至少1nm的厚度,碳基层262a防止阻挡层606(如图6e所述)形成于接触插塞240a上。防止阻挡层606沉积在接触插塞240a上降低了在接触插塞240a的接触电阻。选择至少1nm的厚度也在沉积金属化层246a时(如图6f所示)防止热传递,导致金属化层246a的更对称的沉积,进一步降低接触电阻。通过选择不超过5nm的厚度,碳基层262a不显著增加在接触插塞240a的接触电阻。

137.尽管在此描述关于在接触插塞240a上形成碳基层262a(且在虚置接触插塞240b上形成碳基层262b),上述描述可类似地应用于在接触插塞238上形成碳基层260。

138.进一步如图6b所示,可以在氧化层214上形成蚀刻停止层216。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术以沉积蚀刻停止层216。平坦化工具110可以在沉积蚀刻停止层216之后平坦化蚀刻停止层216。

139.在一些实施方式中,蚀刻停止层216可以具有从约1nm到约3nm的厚度。通过选择至少1nm的厚度,蚀刻停止层216能够具有防止蚀刻停止层216上方的膜层的过度蚀刻的功能。选择不超过3nm的厚度能够防止碳基层262a上的蚀刻停止层216的外延成长,防止蚀刻停止层216增加在接触插塞240a的接触电阻。

140.尽管将蚀刻停止层216描述为具有从约1nm到约3nm的厚度的单一蚀刻停止层膜层,蚀刻停止层216可以包括一或多个额外的膜层。举例而言,蚀刻停止层216可以包括具有从约1nm到约5nm的厚度的额外的硅基层及/或具有从约1nm到约3nm的厚度的额外的铝基层。

141.如图6c所示,氧化层218(也被称为介电层218)可以形成于蚀刻停止层216上。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术沉积氧化层218。平坦化工具110可以在沉积氧化层218之后平坦化氧化层218。

142.如图6d所示,可以蚀刻氧化层218以形成开口(形成凹槽604)。可以蚀刻凹槽604,使得碳基层262a至少部分露出,但碳基层262b不露出。举例而言,沉积工具102可以在氧化层218上(或在形成于氧化层218上的蚀刻停止层上,例如蚀刻停止层220)形成光刻胶层,曝光工具104可以将光刻胶层曝光于辐射源以图案化光刻胶层,显影工具106可以显影并移除部分的光刻胶层以露出图案,且蚀刻工具108可以蚀刻部分的氧化层218以形成凹槽604。在一些实施方式中,光刻胶移除工具114在蚀刻工具108蚀刻凹槽604之后移除光刻胶层的剩余部分(例如,使用化学剥除剂、等离子体灰化机及/或其他技术)。

143.尽管在此描述关于在接触插塞240a(与虚置接触插塞240b)上方的氧化层218中形成凹槽604,上述叙述可类似地应用于在接触插塞238上方的氧化层218中形成凹槽604。

144.如图6e所示,可以在凹槽604的侧壁上(且在一些实施方式中,在氧化层218的至少一部分上)形成阻挡层606。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术以沉积阻挡层606。在一些实施方式中,将阻挡层606选择性沉积在凹槽604的侧壁上,但不沉积在碳基层262a上。举例而言,可以使用与电介质反应(因此与氧化层218反应)但不与有机材料反应(因此不与碳基层262a反应)的前驱材料沉积阻挡层606。通过防止阻挡层606沉积在接触插塞240a上,碳基层262a降低了在接触插塞240a的接触电阻。平坦化工具110可以在沉积阻挡层606之后平坦化至少一部分的阻挡层606。

145.如图6f所示,可以在凹槽604中形成金属化层246a与虚置金属化层246b。金属化层246a可以形成于碳基层262a上且因此与接触插塞240a电性连接,且虚置金属化层246b不接

触碳基层262b且与虚置接触插塞240b电性隔离。沉积工具102可以使用cvd技术、pvd技术、ald技术、或其他类型的沉积技术沉积金属化层246a与虚置金属化层246b的材料,镀覆工具112可以使用电镀操作或前述的组合沉积金属化层246a与虚置金属化层246b的材料。平坦化工具110可以在沉积之后平坦化金属化层246a与虚置金属化层246b。碳基层262a在沉积金属化层246a时帮助防止热扩散,造成金属化层246a的更对称的沉积并降低在接触插塞240a与金属化层246a之间的金属界面的表面粗糙度。降低表面粗糙度可降低在金属界面的接触电阻。

146.尽管在此描述关于在接触插塞240a上的碳基层262a上形成金属化层246a(以及在碳基层262b上但不与其接触地形成虚置金属化层246b),上述描述可类似地应用于在接触插塞238上的碳基层260上形成金属化层244。

147.通过使用结合图6a~图6f描述的技术,阻挡层606防止了来自接触插塞240a的金属(例如,铜)的扩散,降低接触插塞240a的电阻率并防止包括接触插塞240a的电气装置的失效。此外,碳基层262a降低了在接触插塞240a与金属化层246a之间的金属界面的接触电阻。

148.如上所述,提供图6a~图6f以作为一或多个范例。其他范例可以与图6a~图6f所述的范例不同。举例而言,在一些实施方式中,与图4a~图4g及图5a~图5h所述类似,可以在沉积蚀刻停止层216与氧化层218之后形成碳基层262a,使得碳(例如,以石墨烯或石墨的形式)不沉积在虚置接触插塞240b上。

149.图7a~图7g是在此描述的范例实施方式700的图。范例实施方式700可以是用于形成碳基层262的范例工艺。碳基层262降低了接触电阻,增加了电子装置的电气性能。此外,在将金属化层246沉积在接触插塞240上之前蚀刻碳基层262,进一步降低接触电阻。范例实施方式700可以类似地用于在金属化层244与接触插塞238之间形成碳基层260、在导孔248与金属化层244之间形成碳基层及/或在导孔250与金属化层246之间形成碳基层264。

150.如图7a所示,用于形成金属化层246的范例工艺可以与feol一起进行。在一些实施方式中,feol包括在氧化层210内的栅极232上形成的栅极接触件242。此外,feol可以包括形成于氧化层210中的一或多个金属源极或漏极接触件230。如图7a所示,金属源极或漏极接触件230可以包括间隔物234,且栅极232可以包括间隔物236。在一些实施方式中,进一步如图7a所示,在氧化层210与间隔物236之间沉积蚀刻停止层208。在一些实施方式中,如结合图4a~图4g及图5a~图5h所述,栅极接触件242被阻挡层围绕。

151.进一步如图7a所示,用于形成金属化层246的范例工艺可以与meol一起进行。在一些实施方式中,meol包括形成于氧化层214内的栅极接触件242上的接触插塞240a。在一些实施方式中,如结合图4a~图4g及图5a~图5h所述,接触插塞240a被阻挡层围绕及/或在碳基层256与栅极接触件242交界。

152.在一些实施方式中,进一步如图7a所示,在氧化层214与氧化层210之间沉积蚀刻停止层212。此外,meol可以包括一或多个虚置结构,例如虚置接触插塞240b。如图7a所示,虚置接触插塞240b不电性连接到栅极接触件或金属源极或漏极接触件。

153.如图7b所示,碳基层262a可以形成于接触插塞240a上,且碳基层262b可以形成于虚置接触插塞240b上。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术沉积碳基层262a及262b。在一些实施方式中,将碳基层262a及262b选择性沉积在接

触插塞240a及虚置接触插塞240b上,但不沉积在氧化层214上。举例而言,可以使用与金属反应(因此与接触插塞240a及虚置接触插塞240b反应)但不与介电材料反应(因此不与氧化层214反应)的有机前驱材料沉积碳基层262a及262b。

154.在一些实施方式中,碳基层262a(且类似地碳基层262b)可以具有从约1nm到约5nm的厚度。通过选择至少1nm的厚度,碳基层262a防止阻挡层606(如图7e所述)形成于接触插塞240a上。防止阻挡层606沉积在接触插塞240a上降低了在接触插塞240a的接触电阻。通过选择不超过5nm的厚度,降低了用于蚀刻碳基层262a(如图7f所示)的时间、功率及化学品的量。

155.尽管在此描述关于在接触插塞240a上形成碳基层262a(且在虚置接触插塞240b上形成碳基层262b),上述描述可类似地应用于在接触插塞238上形成碳基层260。

156.进一步如图7b所示,可以在氧化层214上形成蚀刻停止层216。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术以沉积蚀刻停止层216。平坦化工具110可以在沉积蚀刻停止层216之后平坦化蚀刻停止层216。

157.在一些实施方式中,蚀刻停止层216可以具有从约1nm到约3nm的厚度。通过选择至少1nm的厚度,蚀刻停止层216能够具有防止蚀刻停止层216上方的膜层的过度蚀刻的功能。选择不超过3nm的厚度能够防止碳基层262a上的蚀刻停止层216的外延成长,防止蚀刻停止层216增加在接触插塞240a的接触电阻。

158.尽管将蚀刻停止层216描述为具有从约1nm到约3nm的厚度的单一蚀刻停止层膜层,蚀刻停止层216可以包括一或多个额外的膜层。举例而言,蚀刻停止层216可以包括具有从约1nm到约5nm的厚度的额外的硅基层及/或具有从约1nm到约3nm的厚度的额外的铝基层。

159.如图7c所示,氧化层218(也被称为介电层218)可以形成于蚀刻停止层216上。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术沉积氧化层218。平坦化工具110可以在沉积氧化层218之后平坦化氧化层218。

160.如图7d所示,可以蚀刻氧化层218以形成开口(形成凹槽604)。可以蚀刻凹槽604,使得碳基层262a至少部分露出,但碳基层262b不露出。举例而言,沉积工具102可以在氧化层218上(或在形成于氧化层218上的蚀刻停止层上,例如蚀刻停止层220)形成光刻胶层,曝光工具104可以将光刻胶层曝光于辐射源以图案化光刻胶层,显影工具106可以显影并移除部分的光刻胶层以露出图案,且蚀刻工具108可以蚀刻部分的氧化层218以形成凹槽604。在一些实施方式中,光刻胶移除工具114在蚀刻工具108蚀刻凹槽604之后移除光刻胶层的剩余部分(例如,使用化学剥除剂、等离子体灰化机及/或其他技术)。

161.尽管在此描述关于在接触插塞240a(与虚置接触插塞240b)上方的氧化层218中形成凹槽604,上述叙述可类似地应用于在接触插塞238上方的氧化层218中形成凹槽604。

162.如图7e所示,可以在凹槽604的侧壁上(且在一些实施方式中,在氧化层218的至少一部分上)形成阻挡层606。沉积工具102可以通过cvd技术、pvd技术、ald技术、或其他类型的沉积技术沉积阻挡层606。在一些实施方式中,将阻挡层606选择性沉积在凹槽604的侧壁上,但不沉积在碳基层262a上。举例而言,可以使用与电介质反应(因此与氧化层218反应)但不与有机材料反应(因此不与碳基层262a反应)的前驱材料沉积阻挡层606。通过防止阻挡层606沉积在接触插塞240a上,碳基层262a降低了在接触插塞240a的接触电阻。平坦化工

具110可以在沉积阻挡层606之后平坦化至少一部分的阻挡层606。

163.如图7f所示,可以蚀刻碳基层262a。举例而言,蚀刻工具108可以使用与有机材料反应(因此与碳基层262a反应)且不与无机材料反应(因此不与阻挡层606与接触插塞240a反应)的一或多个蚀刻剂。进一步如图7g所示,部分的碳基层262a可以留在阻挡层606与接触插塞240a之间。

164.如图7g所示,可以在凹槽604中形成金属化层246a与虚置金属化层246b。金属化层246a可以形成于碳基层262a上且与接触插塞240a电性连接,且虚置金属化层246b形成于接触插塞240b上但与虚置接触插塞240b电性隔离。沉积工具102可以使用cvd技术、pvd技术、ald技术、或其他类型的沉积技术沉积金属化层246a与虚置金属化层246b的材料,镀覆工具112可以使用电镀操作或前述的组合沉积金属化层246a与虚置金属化层246b。平坦化工具110可以在沉积之后平坦化金属化层246a与虚置金属化层246b。因为碳基层262a被蚀刻,进一步降低了在金属化层246a与接触插塞240a之间的金属界面的接触电阻。

165.尽管在此描述关于在接触插塞240a上形成金属化层246a(且将虚置金属化层246b形成于虚置接触插塞240b上但不接触虚置接触插塞240b),上述描述可类似地应用于在接触插塞238上形成金属化层244。

166.通过使用结合图7a~图7g所述的技术,阻挡层606防止了来自金属化层246a的金属(例如,铜)的扩散,降低金属化层246a的电阻率并防止包括金属化层246a的电气装置的失效。此外,碳基层262a防止阻挡层606沉积在金属化层246a与接触插塞240a之间的金属界面,降低在金属界面的接触电阻。在沉积金属化层246a之前也蚀刻碳基层262a以进一步降低在金属界面的接触电阻。

167.如上所述,提供图7a~图7g以作为一或多个范例。其他范例可以与图7a~图7g所述的范例不同。举例而言,在一些实施方式中,与图4a~图4g及图5a~图5h所述类似,可以在沉积蚀刻停止层216与氧化层218之后形成碳基层262a,使得碳(例如,以石墨烯或石墨的形式)不沉积在虚置接触插塞上。

168.图8是装置800的范例组件的图。在一些实施方式中,一或多个半导体处理工具102~114及/或芯片/裸片运输工具116可以包括一或多个装置800及/或装置800的一或多个组件。如图8所示,装置800包括总线(bus)810、处理器820、存储器830、输入组件840、输出组件850及通信组件860。

169.总线810包括在装置800的组件之间实现有线及/或无线通信的一或多个组件。总线810可以例如通过操作耦合(operative coupling)、通信耦合(communicative coupling)、电子耦合(electronic coupling)及/或电耦合(electric coupling)以将两个或多个图8的组件耦合在一起。处理器820包括中央处理单元、图像处理单元、微处理器、控制器、微控制器、数字信号处理器、现场可程序栅极阵列(field-programmable gate array)、特定应用集成电路(application-specific integrated circuit)及/或其他类型的处理组件。处理器820是以硬体、韧体、或硬体及软体的组合来实现。在一些实施方式中,处理器820包括能够被程序化以进行本公开别处描述之一或多个操作或工艺的一或多个处理。

170.存储器830包括挥发性及/或非易失性存储器。举例而言,存储器830可以包括随机存取存储器(random access memory,ram)、只读存储器(read only memory,rom)、硬式磁

碟机及/或其他类型的存储器(例如,快闪存储器、磁存储器及/或光存储器)。存储器830可以包括内存储器(例如,ram、rom、或硬式磁碟机)及/或可移除存储器(例如,通过通用序列总线连接(universal serial bus connection)可移除)。存储器830可以是非暂态电脑可读取媒体(non-transitory computer-readable medium)。存储器830储存与装置800的操作相关的信息、指令及/或软体(例如,一或多个软体应用)。在一些实施方式中,存储器830包括一或多个存储器,其通过例如总线810与一或多个处理器(例如,处理器820)耦合。

171.输入组件840使装置800能够接收输入,例如使用者输入及/或感应输入(sensed input)。举例而言,输入组件840可以包括触控屏幕、键盘、小键盘、鼠标、按钮、麦克风、摇杆、感测器、全球定位系统感测器、加速计(accelerometer)、陀螺仪及/或致动器。输出组件850使装置800能够提供输出,例如通过显示器、喇叭及/或发光二极管。通信组件860使装置800能够通过有线连接及/或无线连接与其他装置通信。举例而言,通信组件860可以包括接收器、发射器、收发器、数据机、网络界面卡及/或天线。

172.装置800可以进行在此描述的一或多个操作或工艺。举例而言,非暂态电脑可读取媒体(例如,存储器830)可以储存用于通过处理器820执行的一组指令(例如,一或多个指令或编码)。处理器820可以执行一组指令以进行在此描述的一或多个操作或工艺。在一些实施方式中,通过一或多个处理器820,执行一组指令造成一或多个处理器820及/或装置800进行在此描述的一或多个操作或工艺。在一些实施方式中,可以使用固线式电路(hardwired circuitry)以代替指令或与指令结合以进行在此描述的一或多个操作或工艺。此外,或替代地,可以配置处理器820以进行在此描述的一或多个操作或处理。因此,在此描述的实施方式并不限于任何特定组合的硬体电路及软体。

173.图8所示的组件的数目及排列作为范例来提供。装置800可以包括额外的组件、较少的组件、不同的组件、或与图8所示的组件不同地排列的组件。此外,或替代地,装置800的一组组件(例如,一或多个组件)可以进行被描述为由装置800的另一组组件进行的一或多个功能。

174.图9是与形成石墨烯或石磨衬层以降低接触电阻相关的范例工艺900的流程图。在一些实施方式中,图9的一或多个工艺步骤可以通过一或多个半导体处理工具(例如,半导体处理工具102~114中的一或多个)来进行。此外,或替代地,图9的一或多个工艺步骤可以通过装置800的一或多个组件来进行,例如处理器820、存储器830、输入组件840、输出组件850及/或通信组件860。

175.如图9所示,工艺900可以包括在第一金属结构的顶表面上沉积碳基层(步骤910)。举例而言,如在此所描述,一或多个半导体处理工具102~114可以在第一金属结构242/240a的顶表面沉积碳基层256/262a。

176.进一步如图9所示,工艺900可以包括在第一金属结构上方的凹槽的侧壁上直接沉积阻挡层(步骤920)。举例而言,如在此所描述,一或多个半导体处理工具102~114可以在第一金属结构242/240a上方的凹槽404/604的侧壁上直接沉积阻挡层406/606。

177.进一步如图9所示,工艺900可以包括在第一金属结构上、凹槽内以及侧壁之间沉积第二金属结构(步骤930)。举例而言,如在此所描述,一或多个半导体处理工具102~114可以在第一金属结构242/240a上、凹槽404/604内以及侧壁之间沉积第二金属结构240/246a。

178.工艺900可以包括额外的实施方式,例如以下所述的任何单一实施方式或任何实施方式的组合及/或与本公开别处描述的一或多个其他工艺结合。

179.在第一实施方式中,工艺900包括在第一虚置金属结构240b的顶表面上沉积额外的碳基层262b,且在第一虚置金属结构上方沉积第二虚置金属结构246b,使得第二虚置金属结构246b不接触第一虚置金属结构240b。

180.在第二实施方式中,单独或结合第一实施方式,工艺900包括在沉积碳基层256/262a之后沉积至少一个蚀刻停止层216与氧化层218,且蚀刻氧化层218以在第一金属结构242/240a上方形成凹槽404/604。

181.在第三实施方式中,单独或结合第一实施方式,工艺900包括在沉积碳基层256/262a之前沉积至少一个蚀刻停止层216与氧化层218,且蚀刻氧化层218以在第一金属结构242/240a上方形成凹槽404/604。

182.在第四实施方式中,单独或结合第一到第三实施方式中的一或多个,沉积第二金属结构240/246a包括沉积第二金属结构240/246a以与第一金属结构242/240a在金属界面交界,其中碳基层256/262a位于金属界面。

183.在第五实施方式中,单独或结合第一到第三实施方式中的一或多个,工艺900包括在沉积第二金属结构240/246a之前蚀刻一部分的碳基层256/262a,其中碳基层256/262a的剩余部分位于阻挡层406/606与第一金属结构242/240a之间的界面。

184.尽管图9显示工艺900的范例步骤,在一些实施方式中,工艺900可以包括额外的步骤、较少的步骤、不同的步骤、或与图9所描绘的步骤不同地排列的步骤。此外,或替代地,工艺900的两个或多个步骤可以同时进行。

185.如此一来,在金属界面(例如,在meol内连线与栅极接触件或源极或漏极区接触件之间、meol接触插塞与beol金属化层之间及/或beol导电结构之间)的碳(例如,石墨或石墨烯)的膜层降低了在金属界面的接触电阻,增加电子装置的电气性能。此外,在一些实施方式中,碳的膜层在将第二金属沉积在第一金属上时帮助防止从第二金属到第一金属的热传递。这导致了第二金属的更对称的沉积,降低了在金属界面的表面粗糙度及接触电阻。作为替代,在一些实施方式中,在沉积第二金属之前蚀刻碳的膜层以降低在金属界面的接触电阻。

186.如以上更详细的描述,在此描述的一些实施方式提供一种半导体结构。半导体结构包括在第一氧化层内邻近第一虚置金属结构的第一金属结构。半导体结构包括还包括沉积在第一氧化层上方的第二氧化层。半导体结构包括在第二氧化层内沉积在第一金属结构上的第二金属结构。半导体结构还包括沉积在第一虚置金属结构的顶表面上的碳基层。

187.在一些实施例中,半导体结构还包括:至少一个蚀刻停止层,沉积于第一氧化层与第二氧化层之间,其中碳基层位于第一虚置金属结构与至少一个蚀刻停止层之间的界面。

188.在一些实施例中,半导体结构还包括:第二虚置金属结构,设置于第一虚置金属结构上方以及第二氧化层内,其中第二虚置金属结构不接触第一虚置金属结构。

189.在一些实施例中,半导体结构还包括:额外的碳基层,沉积于第一金属结构的顶表面上,其中额外的碳基层位于第一金属结构与第二金属结构之间的金属界面。

190.在一些实施例中,半导体结构还包括:阻挡层,沉积于第二金属结构与第二氧化层之间。

191.在一些实施例中,半导体结构还包括:额外的碳基层,沉积于第一金属结构的一部分的顶表面上,其中额外的碳基层位于第一金属结构与阻挡层之间的界面,且实质上不在第一金属结构与第二金属结构之间的金属界面。

192.在一些实施例中,第一金属结构包括栅极接触件、金属源极接触件、或金属漏极接触件,且第二金属结构包括内连线。

193.在一些实施例中,第一金属结构包括接触插塞,且第二金属结构包括金属化层。

194.如以上更详细的描述,在此描述的一些实施方式提供一种半导体结构的形成方法。上述方法包括在第一金属结构的顶表面上沉积碳基层。上述方法还包括在第一金属结构上方的凹槽的侧壁上直接沉积阻挡层。上述方法包括在第一金属结构上、凹槽内以及侧壁之间沉积第二金属结构。

195.在一些实施例中,上述方法还包括:在第一虚置金属结构的顶表面上沉积额外的碳基层;以及在第一虚置金属结构上方沉积第二虚置金属结构,其中第二虚置金属结构不接触第一虚置金属结构。

196.在一些实施例中,上述方法还包括:在沉积碳基层之后沉积至少一个蚀刻停止层与氧化层;以及蚀刻氧化层以在第一金属结构上方形成凹槽。

197.在一些实施例中,上述方法还包括:在沉积碳基层之前沉积至少一个蚀刻停止层与氧化层;以及蚀刻氧化层以在第一金属结构上方形成凹槽。

198.在一些实施例中,上述方法还包括:沉积第二金属结构以在金属界面与第一金属结构交界,其中碳基层位于金属界面。

199.在一些实施例中,上述方法还包括:在沉积第二金属结构之前蚀刻一部分的碳基层,其中剩余部分的碳基层位于阻挡层与第一金属结构之间的界面。

200.如以上更详细的描述,在此描述的一些实施方式提供一种半导体结构。半导体结构包括第一金属结构。半导体结构还包括沉积在第一金属结构上且在金属界面与第一金属结构交界的第二金属结构。半导体结构包括位于金属界面的碳基层。

201.在一些实施例中,碳基层位于第一金属结构与第二金属结构之间以实质上防止第一金属结构与第二金属结构之间的接触。

202.在一些实施例中,半导体结构还包括:第一阻挡层,沉积于第一金属结构与第一氧化层之间;以及第二阻挡层,沉积于第二金属结构与第二氧化层之间。

203.在一些实施例中,碳基层位于第一金属结构与第二阻挡层之间以实质上防止第一金属结构与第二阻挡层之间的接触。

204.在一些实施例中,半导体结构还包括:蚀刻停止层,邻近碳基层,其中蚀刻停止层具有从约1纳米(nm)到约3nm的深度。

205.在一些实施例中,碳基层具有从约1纳米(nm)到约5nm的深度。

206.以上概述数个实施例的特征,以使本发明所属技术领域中技术人员可更易理解本发明实施例的观点。本发明所属技术领域中技术人员应理解,可轻易地以本发明实施例为基础,设计或修改其他工艺和结构,以达到与在此介绍的实施例相同的目的及/或优势。在本发明所属技术领域中技术人员也应理解到,此类等效的工艺和结构并无悖离本发明的精神与范围,且可在不违背随附的权利要求的精神和范围之下,做各式各样的改变、取代和替换。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1