一种变掺杂SiC外延结构的制作方法

一种变掺杂sic外延结构

技术领域

1.本发明属于半导体器件技术领域,特别涉及一种sic外延结构。

背景技术:

2.空间辐射环境是一个充斥着各类宇宙射线的复杂环境,其主要包括由质子和α粒子构成的银河宇宙射线(gcr),由太阳大气加速的高能量、高通量带电粒子流组成的太阳宇宙射线(scr),自太阳飞向地球的热电离气体形成的太阳风,以及由地磁场俘获的质子、电子和少量低能重离子构成的地球辐射带(范艾伦带),来自地面或高空核武器爆炸产生的核辐射、高能电磁脉冲和核爆冲击波组成的空间核爆环境及上述高能粒子与航天飞船的构成材料相互作用产生的次级粒子,均对航天器有着不用程度的影响。

3.单粒子烧毁(seb,single-event burnout)是指由于个别高能粒子的入射导致器件产生正反馈使电流迅速增大并最终烧毁器件的现象。seb往往由于高能离子入射引发的寄生三极管开启或强电场下的局部电场过高,从而引发局部剧烈温升导致永久性器件失效。

4.sic材料被认为具有抗辐照的潜力,同时实验证明sic mosfet在抗总剂量方面的表现十分优越。但是sic的单粒子辐照效应抗性较差。通常,sic功率器件在高let辐照下往往在不到额定电压50%的偏压下发生seb。研究表明,深p-body/低浓度p-body层有助于提升seb抗性,但si基mosfet使用的长时间高温退火推结的方式在sic器件中无法实现,通过注入方式制造的p阱结深往往不超过1μm,这不利于sic器件的抗辐照加固设计。同时,虽然有报道轻掺杂、厚外延的sic高压材料制成的器件能够获得更高的seb抗性,但会使导通电阻急剧增大,无法满足高性能器件要求。

技术实现要素:

5.为解决上述sic器件单粒子辐照抗性差的问题,本发明提出一种变掺杂sic外延结构,其技术方案如下:

6.一种变掺杂sic外延结构,包括,

7.第一导电类型衬底;

8.形成于所述第一导电类型衬底上的第一导电类型缓冲层;

9.形成于所述第一导电类型缓冲层上的第一导电类型漂移层;

10.所述第一导电类型漂移层进一步包括,

11.形成于所述第一导电类型缓冲层上的第一导电类型耐压层;

12.形成于所述第一导电类型耐压层上的第一导电类型过渡层;

13.形成于所述第一导电类型过渡层上的第一导电类型补偿层。

14.进一步地,所述第一导电类型缓冲层的厚度为0.5μm~30μm,所述第一导电类型缓冲层为均匀掺杂或非均匀掺杂,所述第一导电类型缓冲层的平均掺杂浓度为2e15cm-3

~1e19cm-3

。

15.进一步地,所述第一导电类型耐压层为均匀掺杂或非均匀掺杂,所述第一导电类型耐压层的平均掺杂浓度为1e15cm-3

~1e17cm-3

,所述第一导电类型耐压层的厚度为5μm~20μm,所述第一导电类型耐压层靠近所述第一导电类型过渡层位置的掺杂浓度不高于所述第一导电类型耐压层靠近所述第一导电类型缓冲层位置的掺杂浓度,所述第一导电类型耐压层的最高掺杂浓度与最低掺杂浓度的比值不超过10。

16.进一步地,根据权利要求1所述变掺杂sic外延结构,其特征在于,所述第一导电类型过渡层为均匀掺杂或非均匀掺杂,所述第一导电类型过渡层的平均掺杂浓度为5e14cm-3

~1e16cm-3

,所述第一导电类型过渡层的厚度为0.5μm~5μm,所述第一导电类型过渡层的最高掺杂浓度与最低掺杂浓度的比值不超过2,所述第一导电类型过渡层包含所述外延结构中最低掺杂浓度的区域。

17.进一步地,所述第一导电类型补偿层为非均匀掺杂,所述第一导电类型补偿层的平均掺杂浓度为1e15cm-3

~2e16cm-3

,所述第一导电类型补偿层的厚度为0.5μm~5μm,所述第一导电类型补偿层靠近外延层表面位置的掺杂浓度与所述第一导电类型补偿层靠近所述第一导电类型过渡层位置的掺杂浓度的比值不低于1.2。

18.本发明的有益效果:

19.本发明通过设置过渡层和补偿层,可以提高后续第二导电类型注入后形成的有效阱区结深,降低第二导电类型阱区在靠近pn结附近的纵向浓度梯度变化,同时抑制由于轻掺杂漂移层导致的导通电阻过大问题。此外,本发明可以结合外延缓冲层和缓变/多层漂移区耐压层,在保障芯片击穿耐压的同时最大限度的抑制单粒子辐照过程中的材料温升,能有效提升sic功率器件的抗辐照加固能力。

附图说明

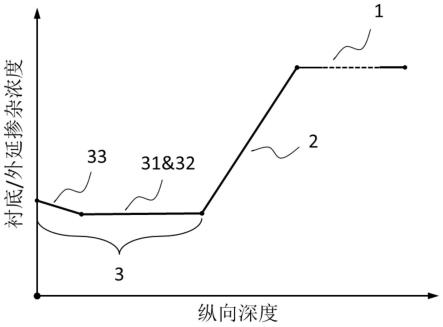

20.图1为实施例1的sic外延结构掺杂浓度示意图;

21.图2为实施例2的sic外延结构掺杂浓度示意图;

22.图3为实施例3的sic外延结构掺杂浓度示意图;

23.图4为实施例4的sic外延结构掺杂浓度示意图;

24.图5为实施例5的sic外延结构掺杂浓度示意图;

25.图6为5种仿真验证用器件的外延掺杂浓度示意图;

26.图7为5种仿真验证用器件沟道区域的纵向p型掺杂浓度示意图;

27.图8为5种器件单粒子辐照结温变化仿真结果图;

28.图9为5种器件的正向转移特性曲线仿真结果图。

29.附图标记说明:1、第一导电类型衬底;2、第一导电类型外延缓冲层;3、第一导电类型漂移层;31、第一导电类型耐压层;32、第一导电类型过渡层;33、第一导电类型补偿层。

具体实施方式

30.以下结合实施例对本发明作进一步的描述,实施例仅用于对本发明进行说明,并不构成对权利要求范围的限制,本领域技术人员可以想到的其他替代手段,均在本发明权利要求范围内。

31.此外,在本发明的描述中,需要说明的是,术语“中央”、“中心”、“上”、“下”、左”、

cm-3

的外延缓冲层。将a中1μm/1e18 cm-3

的外延缓冲层替换为10μm、掺杂浓度由1e18 cm-3

(近衬底区域)渐变至1e16 cm-3

(近外延层漂移区)的结构,即得到b。将b中10μm/1e16 cm-3

的均匀掺杂外延层浓度替换为5e15 cm-3

,即得到c和d。而e器件的外延结构则是在b的10μm、掺杂浓度渐变外延缓冲层基础上,进一步增加本发明中所述的耐压层、过度层和补偿层,形成一种本发明的抗辐照外延结构示例。

48.在外延结构的基础上,进行mosfet器件的定义与仿真,5种器件除外延结构和pwell纵向掺杂不同外,其他仿真结构完全相同,均采用0.55μm的沟道长度和50nm厚的栅氧层。如图7所示,a、b和c器件的pwell为一种常见的pwell掺杂分布,结深约0.75μm,d、e则采用深pwell掺杂结构,结深约2.5μm。

49.5种器件的单粒子仿真结果如图8所示。采用同样的漏极电压偏置,入射位置为pwell正中央。仿真结果显示,接近常规器件结构的a具有最高的单粒子辐照温升。通过优化外延缓冲层可以实现单粒子结温的抑制(b),但降低外延层漂移区掺杂浓度无法进一步提升器件的单粒子抗性(c)。深pwell则是抗单粒子辐照加固的另一个重要方向,通过采用深pwell结构可以进一步抵制单粒子辐照过程中的结温增大(d)。通过结合深pwell结构,本发明的提出的外延结构(e)可实现最优的抗单粒子烧毁效果。

50.图9展示了5种器件的转移特性曲线仿真结果,仿真时所用的漏源电压v

ds

固定为2v。可以看出,近衬底的外延缓冲层未对正向特性造成明显影响,但外延层漂移区的掺杂浓度进一步降低时器件的导通电阻会显著增大。而本发明通过设置补偿层,显著提高了近器件表明的外延层掺杂浓度,一定程度上补偿了由于外延层漂移区浓度降低带来的导通电阻增大问题,正向特性未受显著影响,器件性能得以保证。因此,本发明可以在保障基本性能的基础上有效提升器件的抗单粒子烧毁能力,有较好的应用前景。

51.应说明的是,以上实施例仅用以说明本发明的技术方案而非限制,尽管参照较佳实施例对本发明进行了详细说明,本领域的普通技术人员应当理解,可以对本发明的技术方案进行修改或者等同替换,而不脱离本发明技术方案的精神和范围,其均应涵盖在本发明的权利要求范围当中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1