封装结构的制作方法

本发明有关于一种利用半导体晶片作为晶片座的封装结构,特别有关于一种利用半导体晶片区隔导线架上不同电位且通过半导体基板上的内连结构进行晶片间的连线的封装结构。

背景技术:

1、智慧型功率模块(intelligent power module,ipm)将多颗功率元件(如,互补金属氧化半导体)、栅极驱动电路以及被动元件集合于一体的高效能且高可靠度封装技术。由于乘载微处理器、栅极驱动电路、功率元件以及自举二极管(bootstrap diode)的载板的电位相互不同,因此必须在导线架上分割为不同电位的晶片座,特别是不同电位的晶片座之间必须保持足够的高压间距,因而造成封装的面积无法缩小、导线架制作困难等问题。此外,功率元件的晶片座必须分割成小尺寸,造成散热能力不佳以及晶片之间的走线变得复杂。

2、为了克服因分割导线架而衍生的各种问题,有必要针对智慧型功率模块的导线架进行优化。

技术实现思路

1、本发明在此提出的封装结构能够避免分割导线架而衍生的各种问题。在维持导线架最大化的前提下提供具有不同电压的晶片座,除了保留了导线架的散热性能外,同时缩小了封装的面积且降低导线架制作的难度。此外,本发明提出的封装结构更提供了额外的走线的自由度,大幅降低焊线的走线难度。再者,晶片座下方可形成各种的主动元件以及被动元件,且晶片座周围也可整合其他外部元件,进而提高了系统单封装(system in apackage,sip)的可行性。

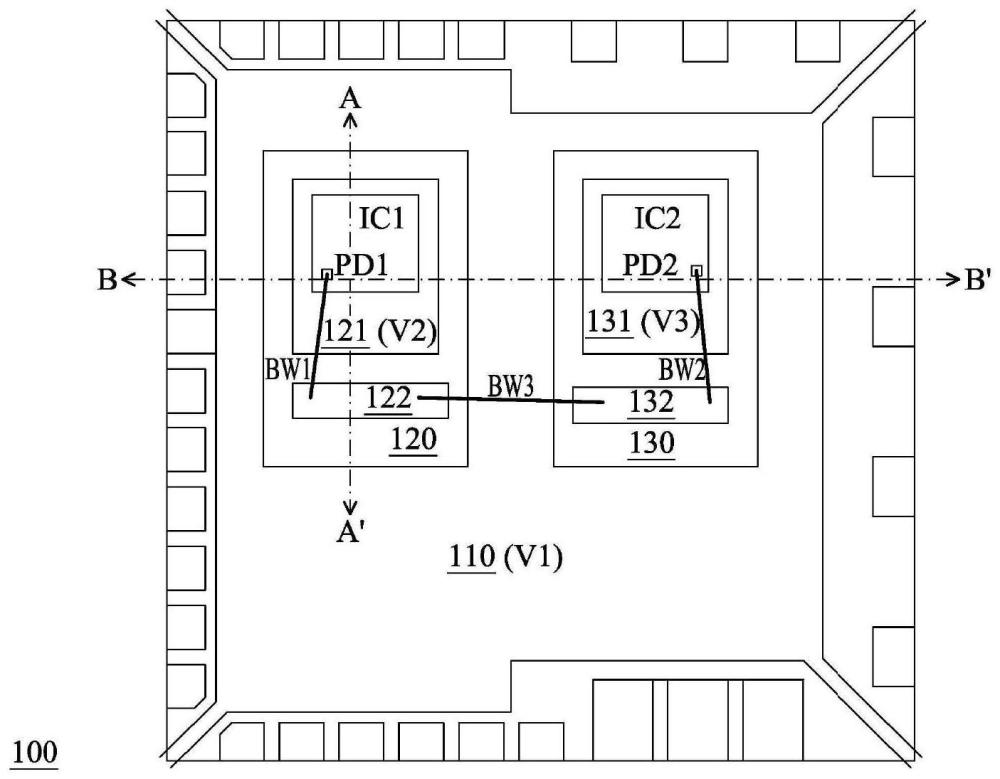

2、有鉴于此,本发明提出一种封装结构,包括一第一载板、一第二载板以及一第一电子装置。上述第一载板耦接至一第一电压。上述第二载板包括一第一基板以及一第一内连结构。上述第一基板与上述第一载板相互接触。上述第一内连结构耦接至一第二电压,其中上述第一内连结构与上述第一载板位于上述第一基板的相异两侧。上述第一电子装置设置于上述第一内连结构之上且远离上述第一载板,其中上述第一电子装置与上述第一内连结构相互接触。

3、根据本发明的一实施例,上述第二载板更包括一第一绝缘层。上述第一绝缘层设置于上述第一基板以及上述第一内连结构之间,其中上述绝缘层的厚度根据上述第一电压以及上述第二电压的电压差所决定。

4、根据本发明的一实施例,一电子元件形成于上述第二载板之中,其中上述电子元件包括一电阻元件或一电感元件。

5、根据本发明的一实施例,一电容元件形成于上述第一内连结构以及上述第一基板之间。

6、根据本发明的一实施例,上述第二载板更包括一第二内连结构,设置于上述第一基板之上。上述第二内连结构与上述第一载板位于上述第一基板的相异两侧,上述第一内连结构以及上述第二内连结构相互电性隔离。

7、根据本发明的一实施例,上述第一电子装置的一第一焊垫通过一第一金属导线电性耦接至上述第二内连结构。上述封装结构更包括一第三载板以及一第二电子装置。上述第三载板包括一第二基板、一第三内连结构以及一第四内连结构。上述第二基板与上述第一载板相互接触。上述第三内连结构耦接至一第三电压且形成于上述第二基板之上,其中上述第三内连结构与上述第一载板位于上述第二基板的相异两侧。上述第四内连结构形成于上述第二基板之上且与上述第一载板位于上述第二基板的相异两侧,其中上述第四内连结构与上述第三内连结构相互电性隔离。上述第二电子装置设置于上述第三内连结构之上且与上述第三内连结构相互接触,其中上述第二电子装置的一第二焊垫耦接至上述第一焊垫。

8、根据本发明的一实施例,上述第二焊垫通过一第二金属导线电性耦接至上述第四内连结构,上述第四内连结构通过一第三金属导线电性耦接至上述第二内连结构。

9、根据本发明的另一实施例,上述第二焊垫通过一第二金属导线电性耦接至上述第二内连结构。

10、根据本发明的一实施例,上述第三载板更包括一第二绝缘层。上述第二绝缘层设置于上述第二基板以及上述第三内连结构之间且设置于上述第二基板以及上述第四内连结构之间。上述第二绝缘层的厚度根据上述第一电压以及上述第三电压的电压差及/或上述第一载板以及上述第四内连结构的电压差所决定。

11、根据本发明的一实施例,上述第一基板以及上述第二基板相互接触而形成一第三基板,其中上述第三基板为一半导体基板。

12、本发明在此提出的封装结构能够避免分割导线架而衍生的各种问题。在维持导线架最大化的前提下提供具有不同电压的晶片座,除了保留了导线架的散热性能外,同时缩小了封装的面积且降低导线架制作的难度。此外,本发明提出的封装结构更提供了额外的走线的自由度,大幅降低焊线的走线难度。再者,晶片座下方可形成各种的主动元件以及被动元件,且晶片座周围也可整合其他外部元件,进而提高了系统单封装(system in apackage,sip)的可行性。

技术特征:

1.一种封装结构,其特征在于,包括:

2.如权利要求1所述的封装结构,其特征在于,上述第二载板更包括:

3.如权利要求1所述的封装结构,其特征在于,一电子元件形成于上述第二载板之中,其中上述电子元件包括一电阻元件或一电感元件。

4.如权利要求1所述的封装结构,其特征在于,一电容元件形成于上述第一内连结构以及上述第一基板之间。

5.如权利要求1所述的封装结构,其特征在于,上述第二载板更包括一第二内连结构,设置于上述第一基板之上,其中上述第二内连结构与上述第一载板位于上述第一基板的相异两侧,上述第一内连结构以及上述第二内连结构相互电性隔离。

6.如权利要求5所述的封装结构,其特征在于,上述第一电子装置的一第一焊垫通过一第一金属导线电性耦接至上述第二内连结构,其中上述封装结构更包括:

7.如权利要求6所述的封装结构,其特征在于,上述第二焊垫通过一第二金属导线电性耦接至上述第四内连结构,上述第四内连结构通过一第三金属导线电性耦接至上述第二内连结构。

8.如权利要求6所述的封装结构,其特征在于,上述第二焊垫通过一第二金属导线电性耦接至上述第二内连结构。

9.如权利要求6所述的封装结构,其特征在于,上述第三载板更包括:

10.如权利要求6所述的封装结构,其特征在于,上述第一基板以及上述第二基板相互接触而形成一第三基板,其中上述第三基板为一半导体基板。

技术总结

一种封装结构,包括第一载板、第二载板以及第一电子装置。第一载板耦接第一电压。第二载板包括第一基板以及第一内连结构。第一基板与第一载板相互接触。第一内连结构耦接至第二电压,其中第一内连结构与第一载板位于第一基板的相异两侧。第一电子装置设置于第一内连结构之上且远离第一载板。第一电子装置与第一内连结构相互接触。

技术研发人员:林容生,黄志丰,杨大勇

受保护的技术使用者:立锜科技股份有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!