一种深槽隔离型抗辐射的高压三极管结构

1.本发明属于半导体功率器件领域,具体涉及一种深槽隔离型抗辐射的高压三极管结构。

技术背景

2.随着功率半导体器件在航空航天的电子系统等的应用越来越广泛,针对电源管理系统和栅驱动电路,抗辐射加固技术成为各个公司和高校的研究重点。而高压三极管作为模块电路中的核心部位,在太空辐射环境下,三极管容易因总剂量辐射的影响而出现发射极与基极之间的表面电流增加现象,导致电流放大系数降低,使得整个电路无法正常工作,因此需要研究抗总剂量辐射的高压三极管。

技术实现要素:

3.为解决高压三极管因总剂量辐射而出现的基区表面复合电流增加的问题,抑制总剂量辐射对器件的影响。本发明提出了一种抗总剂量的高压三极管结构。在太空环境中,三极管受到总剂量效应的影响,会在器件表面氧化层中产生带正电的氧化物陷阱电荷,带正电的氧化物陷阱电荷会改变三极管基区表面的电子浓度上升,增加表面复合,从而使得发射极与基极之间的表面电流增加,三极管的电流放大系数受到影响。本发明通过采用深槽隔离氧化层,改变了电流路径,降低了流经基区/氧化物界面的电流密度,阻止了基区/氧化物界面的复合电流的增加,抑制了三极管共发射极电流放大系数的退化,有效提升了器件的抗总剂量辐射的能力。

4.为了实现上述发明目的,本发明技术方案如下:

5.一种深槽隔离型抗辐射的高压三极管结构,包括位于底部的第一导电类型衬底5、位于第一导电类型衬底5上方的第二导电类型埋层区4、位于第二导电类型埋层区4上方的第二导电类型阱区3、位于第二导电类型埋层区4上方第二导电类型阱区3左侧的第一导电类型阱区2、位于第一导电类型阱区2内左上方的第二导电类型发射区1;深槽隔离氧化层6位于第二导电类型发射区1和第一导电类型阱区2之间,或者位于第二导电类型发射区1内部靠近第一导电类型阱区2的一侧;还包括位于第二导电类型发射区1和第一导电类型阱区2上方发射结上方的一个浅槽隔离氧化层7,位于所述浅槽隔离氧化层7下方的深槽隔离氧化层6,位于第一导电类型阱区2和第二导电类型阱区3上方集电结上方的另一个浅槽隔离氧化层7,位于第二导电类型发射区1上方的第二导电类型发射极注入区8,位于第一导电类型阱区2上方的第一导电类型基极注入区9,位于第二导电类型阱区3上方的第二导电类型集电极注入区10,位于第二导电类型发射极注入区8上方的发射极金属电极11,位于第一导电类型基极注入区9上方的基极金属电极12,位于第二导电类型集电极注入区10上方的集电极金属电极13。

6.作为优选方式,深槽隔离氧化层6下边界超过或相切于第二导电类型发射区1下边界。

7.作为优选方式,深槽隔离氧化层6的上边界与浅槽隔离氧化层7的下边界相切。

8.本发明的有益效果为:本发明提供了一种深槽隔离型抗辐射的高压三极管结构,在第二导电类型发射区1和第一导电类型阱区2之间加入深槽氧化层6,并且使得深槽隔离氧化层6的下界面贴近第一导电类型发射区下界面,改变了电流路径,降低了流经基区/氧化物界面的电流密度,阻止了基区/氧化物界面的复合电流的增加,抑制了三极管共发射极电流放大系数的退化,有效提升了器件的抗总剂量辐射的能力。

附图说明

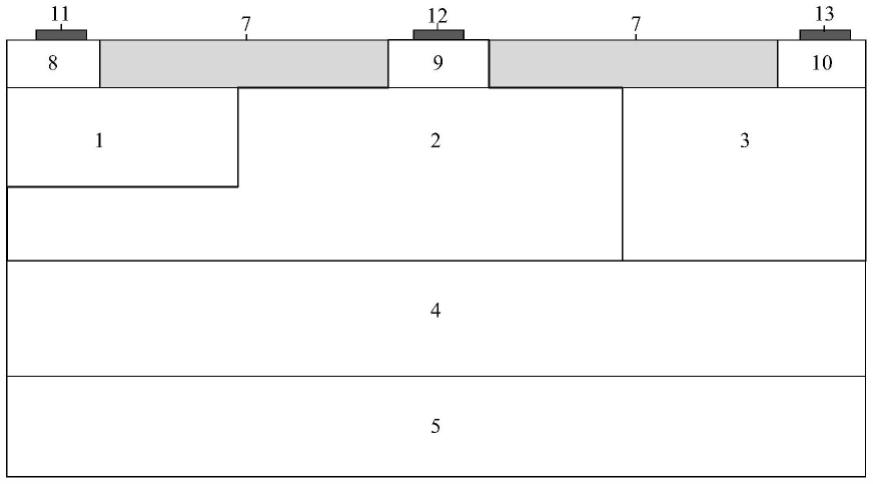

9.图1为常规高压三极管结构图。

10.图2为本发明实施例1的一种深槽隔离型抗辐射的高压三极管结构图。

11.图3为本发明实施例2的一种深槽隔离型抗辐射的高压三极管结构图。

12.图4为本发明实施例3的一种深槽隔离型抗辐射的高压三极管结构图。

13.1为第二导电类型发射区,2为第一导电类型阱区,3为第二导电类型阱区,4为第二导电类型埋层区,5为第一导电类型衬底,6为深槽隔离氧化层,7为浅槽隔离氧化层,8为第二导电类型发射极注入区、9为第一导电类型基极注入区、10为第二导电类型集电极注入区、11为发射极金属电极,12为基极金属电极,13为集电极金属电极。

具体实施方式

14.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻而易举地了解本发明地其他优点与功效。本发明还可以通过不同的具体实施方式加以实施和应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

15.图1为常规高压三极管结构图。当器件受到总剂量辐射效应的影响时,器件表面的氧化层中会产生带正电的氧化层陷阱电荷,正的氧化层陷阱电荷会使得器件轻掺杂基区的表面浓度发生改变,器件表面复合电流增加,最终导致三极管的电流放大系数发生退化。

16.为了避免轻掺杂基区的表面浓度因氧化物陷阱电荷发生改变,使得三极管电流放大系数发生退化,本发明在第二导电类型发射区1和第一导电类型阱区2之间、或者第二导电类型发射区1内部靠近第一导电类型阱区2的一侧加入深槽隔离氧化层6,并且使得深槽隔离氧化层6的下界面超过或相切于第二导电类型发射区下界面,改变了电流路径,降低了流经基区/氧化物界面的电流密度,阻止了基区/氧化物界面的复合电流的增加,抑制了三极管共发射极电流放大系数的退化,有效提升了器件的抗总剂量辐射的能力。

17.实施例1

18.如图2所示,本实施例提供了一种深槽隔离型抗辐射的高压三极管结构,包括位于底部的第一导电类型衬底5、位于第一导电类型衬底5上方的第二导电类型埋层区4、位于第二导电类型埋层区4上方的第二导电类型阱区3、位于第二导电类型埋层区4上方第二导电类型阱区3左侧的第一导电类型阱区2、位于第一导电类型阱区2内左上方的第二导电类型发射区1;深槽隔离氧化层6位于第二导电类型发射区1和第一导电类型阱区2之间;还包括位于第二导电类型发射区1和第一导电类型阱区2上方发射结上方的一个浅槽隔离氧化层7,位于所述浅槽隔离氧化层7下方的深槽隔离氧化层6,位于第一导电类型阱区2和第二导

电类型阱区3上方集电结上方的另一个浅槽隔离氧化层7,位于第二导电类型发射区1上方的第二导电类型发射极注入区8,位于第一导电类型阱区2上方的第一导电类型基极注入区9,位于第二导电类型阱区3上方的第二导电类型集电极注入区10,位于第二导电类型发射极注入区8上方的发射极金属电极11,位于第一导电类型基极注入区9上方的基极金属电极12,位于第二导电类型集电极注入区10上方的集电极金属电极13。

19.所述第一导电类型掺杂杂质为受主型时第二导电类型掺杂杂质为施主型;第一导电类型掺杂杂质为施主型时第二导电类型掺杂杂质为受主型。

20.第二导电类型发射区1和第一导电类型阱区2之间加入深槽氧化层6,且深槽隔离氧化层6下边界相切于第二导电类型发射区2下边界。深槽隔离氧化层6的上边界与浅槽隔离氧化层7的下边界相切。改变了电流路径,降低了流经基区/氧化物界面的电流密度,阻止了基区/氧化物界面的复合电流的增加,抑制了三极管共发射极电流放大系数的退化,有效提升了器件的抗总剂量辐射的能力。

21.实施例2

22.如图3所示,本实施例和实施例1的区别在于;三极管的深槽隔离氧化层6位于第二导电类型发射区1内部靠近第一导电类型阱区2的一侧。

23.实施例3

24.如图4所示,本实例和实施例2的区别在于:三极管的深槽隔离氧化层6下边界超过第二导电类型发射区1下边界。

25.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1