半导体结构及其制造方法与流程

本发明的实施例涉及半导体结构及其制造方法。

背景技术:

1、半导体集成电路(ic)行业经历了指数级增长。ic材料和设计中的技术进步已经产生了多代ic,其中每一代都具有比上一代更小且更复杂的电路。在ic发展的过程中,功能密度(即,每芯片面积的互连器件的数量)普遍增加,而几何尺寸(即,可以使用制造工艺创建的最小组件(或线))已经减小。这种按比例缩小的工艺通常通过提高生产效率和降低相关成本来提供益处。这样的按比例缩小也增加了ic结构(诸如三维晶体管)和处理的复杂性,并且要实现这些进步,需要ic处理和制造方面的类似发展。例如,由于纳米片器件(或全环栅器件)的vdd限制,纳米片器件(或全环栅器件)通常用在低压ic组件中。在设计包括高压应用的基于纳米片器件的ic芯片(例如soc芯片)时,这可能会带来挑战。此外,在高速条件下可能不容易控制纳米片器件。相应地,需要改进纳米片器件的电压容差的方法。

技术实现思路

1、本发明的一些实施例提供了一种半导体结构,该半导体结构包括:衬底;pn结结构的堆叠件,嵌入衬底中;半导体鳍,从衬底突出;源极/漏极结构对,设置在半导体鳍中;以及栅极结构,位于半导体鳍的沟道区域上方,并且介于源极/漏极结构对之间。

2、本发明的另一些实施例提供了一种半导体结构,该半导体结构包括:半导体衬底;结结构,嵌入半导体衬底中,结结构包括成对交替的p型掺杂区域和n型掺杂区域;半导体鳍,从半导体衬底突出,半导体鳍包括沿垂直方向堆叠的半导体层;栅极结构,包裹在每个半导体层的沟道区域周围;以及源极/漏极结构对,设置在栅极结构的相应侧上。

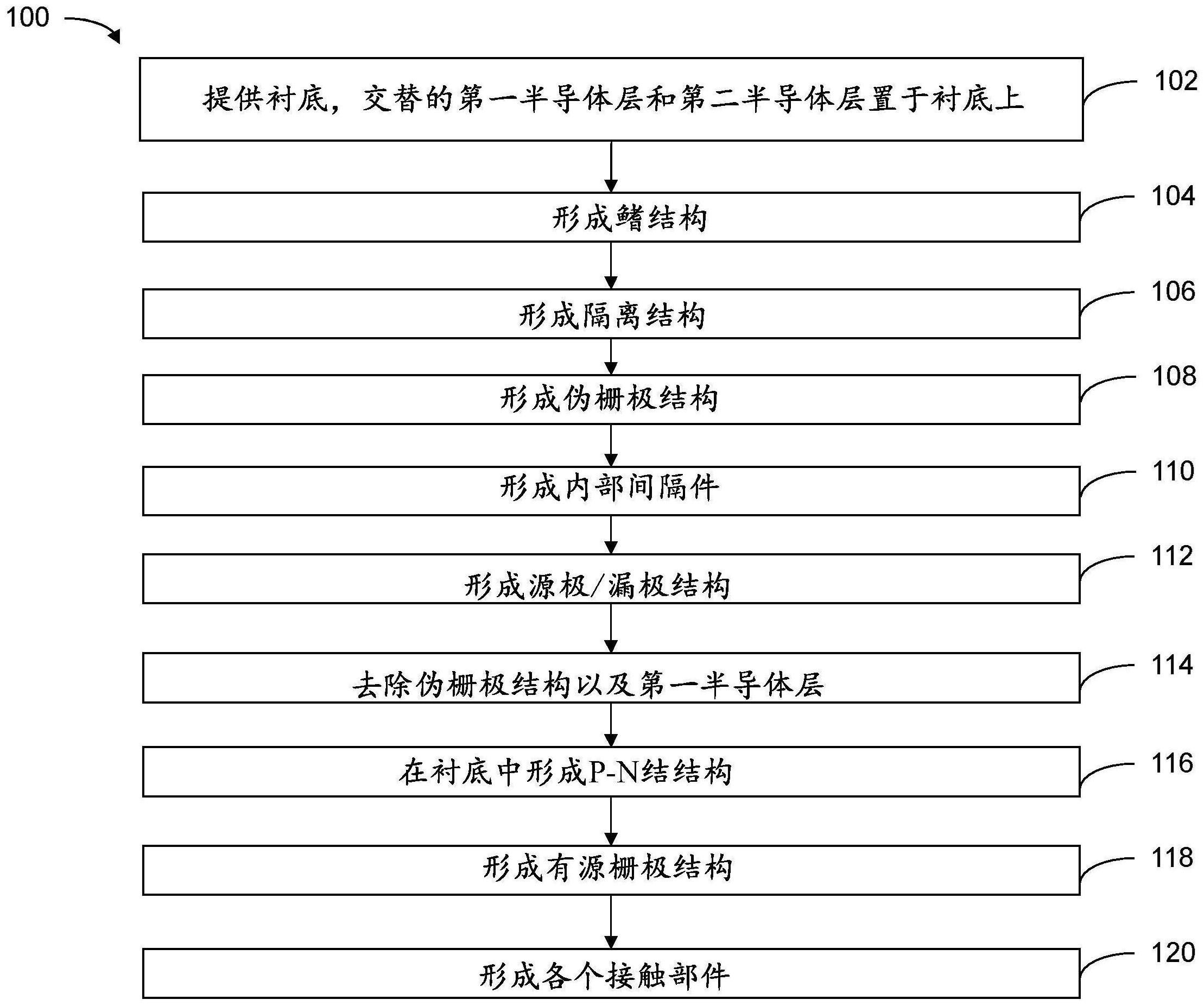

3、本发明的又一些实施例提供了一种制造半导体结构的方法,该方法包括:形成从衬底延伸的半导体鳍,衬底包括p型掺杂层,并且半导体鳍包括交替的第一半导体层和第二半导体层;在半导体鳍的沟道区域上方形成伪栅极结构;在与伪栅极结构相邻的半导体鳍中形成源极/漏极结构;去除伪栅极结构和第一半导体层,以分别形成栅极沟槽和开口;在p型掺杂层中形成彼此垂直间隔开的n型掺杂层的堆叠件;以及在栅极沟槽和开口中形成有源栅极结构。

技术特征:

1.一种半导体结构,包括:

2.根据权利要求1所述的半导体结构,其中,所述pn结结构的堆叠件包括掺杂有n型掺杂剂的所述衬底的第一部分,所述第一部分与掺杂有p型掺杂剂的所述衬底的第二部分交错。

3.根据权利要求2所述的半导体结构,其中,所述源极/漏极结构对包括第一浓度的所述n型掺杂剂,并且所述衬底的所述第一部分包括第二浓度的所述n型掺杂剂,所述第二浓度小于所述第一浓度。

4.根据权利要求1所述的半导体结构,其中,所述衬底包括掺杂有p型掺杂剂的区域。

5.根据权利要求1所述的半导体结构,其中,所述pn结结构的堆叠件以级联配置的方式均横跨对应于所述源极/漏极结构对的区域横向延伸。

6.根据权利要求1所述的半导体结构,其中,所述pn结结构的堆叠件均沿所述半导体鳍的纵向延伸,并且沿垂直于所述衬底的顶表面的方向堆叠。

7.根据权利要求1所述的半导体结构,其中,所述pn结结构的堆叠件沿垂直于所述衬底的顶表面的方向从所述栅极结构的底部部分延伸到10nm至100nm的深度。

8.根据权利要求1所述的半导体结构,其中,所述半导体鳍包括与所述栅极结构交错的多个半导体层。

9.一种半导体结构,包括:

10.一种制造半导体结构的方法,包括:

技术总结

半导体结构包括衬底和嵌入衬底中的pn结结构的堆叠件。半导体结构包括从衬底突出的半导体鳍。半导体结构包括设置在半导体鳍中的源极/漏极结构对。半导体结构包括位于半导体鳍的沟道区域上方并且介于源极/漏极结构对之间的栅极结构。本发明的实施例还提供了制造半导体结构的方法。

技术研发人员:陈家忠,苏子昂,陈柏廷,袁忠盛,郑仪侃

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!