一种电路板双芯片居中抗震加强结构及控制器电路板的制作方法

[0001]

本发明涉及电子舱控制器领域,更具体地说,它涉及一种电路板双芯片居中抗震加强结构及控制器电路板。

背景技术:

[0002]

电子舱在常温进行系统调试时存在上位机采集到的方位、俯仰信号异常跳变的故障现象,通过ansys16.0对当前电子舱使用的控制器进行结构力学分析,结果显示控制器产品在中轴线位置形成应力集中分布区域,在等效加速度66g条件下,控制器中的芯片引脚在该区域局部应力高达4.1mpa。

[0003]

目前,当电子舱处于运行状态时,由于控制器中心集成的旋变解码模块作为板卡重量分布点,振动过程中板卡承受了巨大的冲击;当随机振动频率与旋变解码模块在该处板卡的固有频率重合时形成共振,对板卡造成了巨大的破坏。重量越大,在板卡厚度与加固方式不变的情况下,产品的固有频率越低,受共振影响越严重。所以旋变解码模块在产品中轴线产生强大的破坏应力。受其影响,同样位于中轴线的芯片在该区域的引脚受到旋变解码模块的反复应力冲击,再加上引脚位置的抗剥离强度相对于其他数据线位置处焊盘较弱,当焊点连接处无法承受该交变应力时就发生损伤分离。

[0004]

因此,如何研究设计一种电路板双芯片居中抗震加强结构及控制器电路板是我们目前急需解决的问题。

技术实现要素:

[0005]

为解决现有技术中的不足,本发明的目的是提供一种电路板双芯片居中抗震加强结构及控制器电路板。

[0006]

本发明的上述技术目的是通过以下技术方案得以实现的:第一方面,提供了一种电路板双芯片居中抗震加强结构,包括处于同一平面的第一h型框架、第二h型框架,第二h型框架布设在第一h型框架内作为第一h型框架的横梁;第一h型框架、第二h型框架的布设方向相互垂直;第一h型框架的两开口端与第二h型框架对应的边线梁围合成两个居中分布的供第一芯片、第二芯片对应安装的加强框。

[0007]

进一步的,所述第一h型框架、第二h型框架的边线梁均由多个闭合框架以线性分布方式组合而成。

[0008]

进一步的,所述加强框的边缘设有螺纹通孔,通过螺钉穿过螺纹通孔可将第一芯片、第二芯片与对应的加强框相对固定。

[0009]

进一步的,每个所述加强框对应设置有四个螺纹通孔,四个螺纹通孔分为两组对称设置在第一h型框架的边线梁上。

[0010]

第二方面,提供了一种控制器电路板,包括pcb板和如第一方面中任意一项所述的一种电路板双芯片居中抗震加强结构,pcb板安装有与两个加强框配合的第一芯片、第二芯片。

[0011]

进一步的,所述第一芯片、第二芯片侧面设有与螺纹通孔一一对应设置的安装耳,螺钉依次穿过pcb板、安装耳后与螺纹通孔固定连接。

[0012]

进一步的,所述pcb板还安装有dsp模块、fpga模块、旋变激磁模块、光电隔离模块、电源模块、ad采集模块、da输出模块、jtag接口器、zrm连接器、运放模块、功率振荡模块;第一芯片、第二芯片分别为俯仰旋变解码芯片、方位旋变解码芯片,俯仰旋变解码芯片、方位旋变解码芯片构成旋变解码模块。

[0013]

进一步的,所述旋变激磁模块包括俯仰激磁模块、方位激磁模块;差分模拟信号从zrm连接器进入后经运放模块转为单端模拟信号,模拟信号经ad采集模块转换为数字信号发送到fpga模块;fpga模块发送数据到da输出模块,并通过控制线控制da输出模块,da输出模块输出模拟信号到zrm连接器;俯仰激磁模块、方位激磁模块通过zrm连接器与俯仰旋变解码芯片、方位旋变解码芯片连接,旋变解码模块对输入的模拟信号进行解码转换,将转换后的的数字信号发送到fpga模块,两个解码模块共用数据总线。

[0014]

进一步的,所述dsp模块、fpga模块的jtag接口器分布在第一h型框架一侧开口端,zrm连接器分布在另一侧开口端。

[0015]

进一步的,所述俯仰激磁模块、方位激磁模块对称分布在第一h型框架的两侧边线梁,且位于靠近zrm连接器的一端。

[0016]

与现有技术相比,本发明具有以下有益效果:1、通过求解模态分析,本发明提供的安装有加强结构的控制器电路板的一阶固有频率为769hz,相比于裸板提升近一倍,相对于普通加固框的一阶固有频率提升近50%,加固作用明显,受共振影响较弱;2、本发明提供的安装有加强结构的控制器电路板的正面应力从pcb板过渡集中在加固结构上,pcb板上应力主要集中在板卡外侧边缘,旋变解码模块交界处应力分布大大减少;3、本发明旋变解码模块引脚区域应力由原来的4.11mpa减少到目前的2.59mpa,加强结构对抑制板卡变形作用明显,应力减少36.9%,且小于安全范围3mpa,应力值远远小于焊盘剥离强度10mpa和引线断裂强度250mpa,有效避免疲劳应力裂纹的产生;4、本发明提供的安装有加强结构的控制器电路板应力集中分布区域较现有结构应力区域减少,结构改善有效。

附图说明

[0017]

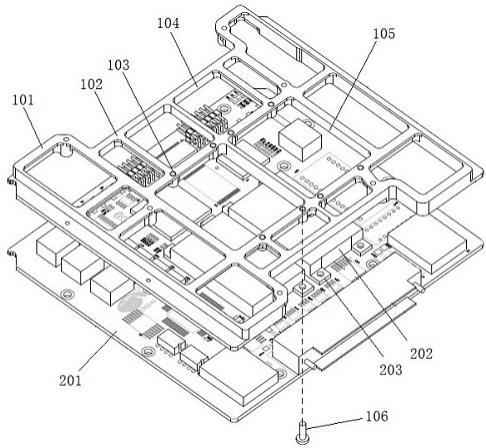

此处所说明的附图用来提供对本发明实施例的进一步理解,构成本申请的一部分,并不构成对本发明实施例的限定。在附图中:图1是本发明实施例中加强结构的安装结构示意图;图2是本发明实施例中pcb板元器件分布结构示意图;图3是本发明实施例中控制器的工作原理框图。

[0018]

附图中标记及对应的零部件名称:101、第一h型框架;102、第二h型框架;103、螺纹通孔;104、闭合框架;105、加强框;106、螺钉;201、pcb板;202、旋变解码模块;203、安装耳;204、jtag接口器;205、zrm连接器;206、

俯仰激磁模块;207、方位激磁模块。

具体实施方式

[0019]

为使本发明的目的、技术方案和优点更加清楚明白,下面结合实施例和附图,对本发明作进一步的详细说明,本发明的示意性实施方式及其说明仅用于解释本发明,并不作为对本发明的限定。

[0020]

需说明的是,当部件被称为“固定于”或“设置于”另一个部件,它可以直接在另一个部件上或者间接在该另一个部件上。当一个部件被称为是“连接于”另一个部件,它可以是直接或者间接连接至该另一个部件上。

[0021]

需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

[0022]

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

[0023]

实施例1:一种电路板双芯片居中抗震加强结构,如图1所示,包括处于同一平面的第一h型框架101、第二h型框架102,第二h型框架102布设在第一h型框架101内作为第一h型框架101的横梁;第一h型框架101、第二h型框架102的布设方向相互垂直;第一h型框架101的两开口端与第二h型框架102对应的边线梁围合成两个居中分布的供第一芯片、第二芯片对应安装的加强框105。在本实施例中,抗震加强结构的材料选用强度较优的al7075。

[0024]

第一h型框架101、第二h型框架102的边线梁均由多个闭合框架104以线性分布方式组合而成。

[0025]

加强框105的边缘设有螺纹通孔103,通过螺钉106穿过螺纹通孔103可将第一芯片、第二芯片与对应的加强框105相对固定。

[0026]

每个所述加强框105对应设置有四个螺纹通孔103,四个螺纹通孔103分为两组对称设置在第一h型框架101的边线梁上。

[0027]

实施例2:一种控制器电路板,如图2所示,包括pcb板201和如实施例1所述的一种电路板双芯片居中抗震加强结构,pcb板201安装有与两个加强框105配合的第一芯片、第二芯片。

[0028]

第一芯片、第二芯片侧面设有与螺纹通孔103一一对应设置的安装耳203,螺钉106依次穿过pcb板201、安装耳203后与螺纹通孔103固定连接。

[0029]

如图2与图3所示,pcb板201还安装有dsp模块、fpga模块、旋变激磁模块、光电隔离模块、电源模块、ad采集模块、da输出模块、jtag接口器204、zrm连接器205、运放模块、功率振荡模块;第一芯片、第二芯片分别为俯仰旋变解码芯片、方位旋变解码芯片,俯仰旋变解码芯片、方位旋变解码芯片构成旋变解码模块202。dsp模块、fpga模块、旋变激磁模块、光电隔离模块、电源模块、ad采集模块、da输出模块、运放模块、功率振荡模块与闭合框架104对应安装,闭合框架104根据具体模块设置为矩形或类矩形。

[0030]

旋变激磁模块包括俯仰激磁模块206、方位激磁模块207;差分模拟信号从zrm连接器205进入后经运放模块转为单端模拟信号,模拟信号经ad采集模块转换为数字信号发送到fpga模块;fpga模块发送数据到da输出模块,并通过控制线控制da输出模块,da输出模块输出模拟信号到zrm连接器205;俯仰激磁模块206、方位激磁模块207通过zrm连接器205与俯仰旋变解码芯片、方位旋变解码芯片连接,旋变解码模块202对输入的模拟信号进行解码转换,将转换后的的数字信号发送到fpga模块,两个解码模块共用数据总线。

[0031]

在本实施例中,dsp模块带有1颗tms320f28335的浮点,最大处理频率为150mhz,并且外扩一个高速flash,与型号为ep3c120f484i7的fpga模块共享外部存储器总线。

[0032]

在本实施例中,ad采集模块为sad7656mq,采用并口方式,有16位数据线、片选、读、写控制等信号。

[0033]

在本实施例中,da输出模块为sda396a,采用并口方式,有8位数据线、两位地址线、写控制和通道选择等信号。

[0034]

在本实施例中,旋变解码模块202为hts18r16-65-6/3-a,共两片,两片解码芯片共用18位数据线接口,经隔离器sm245接到fpga模块,其余控制线分别经过隔离器sm245连接到fpga模块上。

[0035]

在本实施例中,fpga模块与设备1、设备2和设备3之间通过4片sm3490和一片gh0630j进行接口转换。

[0036]

在本实施例中,fpga模块与设备4之间通过sm3490、gh5631z和jt54ls14进行接口转换。

[0037]

在本实施例中,fpga模块与flash芯片sm29lv160控制线进行连接,其余的数据和地址线接到emif总线上。

[0038]

在本实施例中,fpga模块与6路ttl信号通过jt5407驱动之后输出。

[0039]

在本实施例中,fpga模块与dsp模块之间采用并口访问方式,20位地址线,16位数据线,以及读、写、选通、中断信号等,dsp模块与fpga模块之间的信号连接关系如图3所示。

[0040]

dsp模块、fpga模块的jtag接口器204分布在第一h型框架101一侧开口端,zrm连接器205分布在另一侧开口端。在本实施例中,fpga模块和dsp模块的jtag接口器204为2.54mm间距双排弯针,开口向上。

[0041]

俯仰激磁模块206、方位激磁模块207对称分布在第一h型框架101的两侧边线梁,且位于靠近zrm连接器205的一端。在本实施例中,zrm连接器205的型号为zrm452-110-321-9501。

[0042]

实验验证:通过求解模态分析,本发明提供的安装有加强结构的控制器电路板的一阶固有频率为769hz,相比于裸板提升近一倍,相对于普通加固框的一阶固有频率提升近50%,加固作用明显,受共振影响较弱;本发明提供的安装有加强结构的控制器电路板的正面应力从pcb板过渡集中在加固结构上,pcb板上应力主要集中在板卡外侧边缘,旋变解码模块202交界处应力分布大大减少;本发明旋变解码模块202引脚区域应力由原来的4.11mpa减少到目前的2.59mpa,加强结构对抑制板卡变形作用明显,应力减少36.9%,且小于安全范围3mpa,应力值远远小于焊盘剥离强度10mpa和引线断裂强度250mpa,有效避免疲劳应力裂纹的产生;本发明提供的安装有加强结构的控制器电路板应力集中分布区域较现有结构应力区域减少,结构改善有效。

[0043]

以上所述的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1