存储装置的制作方法

存储装置

1.分案申请的相关信息

2.本案是分案申请。该分案的母案是申请日为2017年9月6日、申请号为201710796424.7、发明名称为“存储装置”的发明专利申请案。

3.[相关申请]

[0004]

本技术享有以日本专利申请2017-42675号(申请日:2017年3月7日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

[0005]

实施方式涉及一种存储装置。

背景技术:

[0006]

业界正在推进包含三维配置的存储单元的存储装置的开发。例如,nand(not and,与非)型存储装置具备积层的多个电极层、及设置在将所述多个电极层在积层方向上贯通的存储器孔(memory hole)内的半导体柱。存储单元设置在半导体柱和电极层交叉的部分,沿着半导体柱配置。这种存储装置通过增加电极层的积层数,并通过存储器孔的微细化而增加该存储器孔的数量,能够增大存储容量。但是,在存储装置有限的芯片大小之下,增加存储器孔的数量并增加电极层的积层数存在极限。

技术实现要素:

[0007]

实施方式提供一种能够增大存储容量的存储装置。

[0008]

实施方式的存储装置具备:第1存储单元阵列;第2存储单元阵列,相对于所述第1存储单元阵列配置在第1方向;第1接触插塞,在所述第1存储单元阵列中沿着所述第1方向延伸;及第2接触插塞,在所述第2存储单元阵列中沿着所述第1方向延伸,电连接在所述第1接触插塞。所述第1存储单元阵列包含:多个第1电极层,在所述第1方向上积层;及第1半导体柱,在所述第1方向上贯通所述多个第1电极层。所述第2存储单元阵列包含:多个第2电极层,在所述第1方向上积层;及第2半导体柱,在所述第1方向上贯通所述多个第2电极层。所述第1接触插塞电连接在所述第1半导体柱。所述第2接触插塞电连接在所述第2半导体柱。

附图说明

[0009]

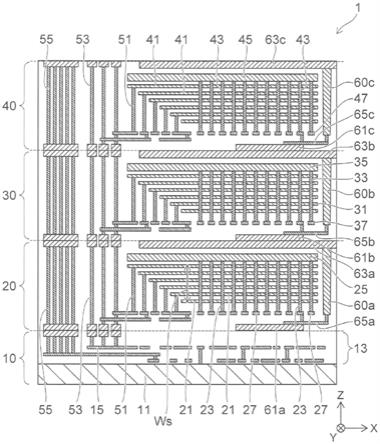

图1是表示第1实施方式的存储装置的示意剖视图。

[0010]

图2a及2b是表示第1实施方式的存储装置的存储单元阵列的构成的示意俯视图。

[0011]

图3是表示第1实施方式的存储装置的存储单元阵列的上表面的示意俯视图。

[0012]

图4是表示第1实施方式的存储装置的存储单元阵列的示意剖视图。

[0013]

图5(a)、(b)、(c)及(d)、6(a)、(b)及(c)、7(a)及(b)、8(a)及(b)、图9及图10是表示第1实施方式的存储装置的存储单元阵列的制造过程的示意剖视图。

[0014]

图11是表示第2实施方式的存储装置的存储单元阵列的构成的示意俯视图。

[0015]

图12a及12b是表示第2实施方式的存储装置的存储单元阵列的示意图。

[0016]

图13a~13c是表示第2实施方式的存储装置的存储单元阵列的制造过程的示意图。

[0017]

图14a~14c是表示第2实施方式的变化例的存储装置的存储单元阵列的制造过程的示意图。

[0018]

图15a~15c是表示第2实施方式的其他变化例的存储装置的存储单元阵列的制造过程的示意图。

[0019]

图16a及16b是表示第3实施方式的存储装置的制造过程的示意剖视图。

[0020]

图17a~17c是表示第3实施方式的变化例的存储装置的制造过程的示意剖视图。

[0021]

图18a及18b是表示第3实施方式的其他变化例的存储装置的制造过程的示意剖视图。

[0022]

图19a及19b是表示第4实施方式的存储装置的示意俯视图。

[0023]

图20是表示第4实施方式的存储装置的其他示意俯视图。

[0024]

图21是表示第4实施方式的存储装置的示意剖视图。

[0025]

图22是表示第4实施方式的存储装置的其他示意剖视图。

[0026]

图23a及23b是表示第4实施方式的变化例的存储装置的示意剖视图。

具体实施方式

[0027]

以下,一边参照附图一边对实施方式进行说明。对附图中的相同部分标注相同编号,并适当省略其详细说明,对不同的部分进行说明。此外,附图为示意图或概念图,各部分的厚度和宽度的关系、部分间的大小的比率等未必与现实相同。另外,即便是表示相同部分的情况下,也有通过附图将相互的尺寸或比率不同地表示的情况。

[0028]

而且,使用各图中所示的x轴、y轴及z轴对各部分的配置及构成进行说明。x轴、y轴、z轴相互正交,分别表示x方向、y方向、z方向。另外,为方便起见,有依照图中的上方、下方进行说明的情况,但并非意图表示全部共通的上下关系。

[0029]

[第1实施方式]

[0030]

图1是表示第1实施方式的存储装置1的示意剖视图。存储装置1例如为nand型闪速存储器装置,具有在驱动电路10之上积层有存储单元阵列20、30及40的构造。此外,图1中,为了表示存储装置1的构造而省略设置在各构成要素间的绝缘膜。

[0031]

驱动电路10例如具有设置有cmos(complementary metal oxide semiconductor,互补金属氧化物半导体)晶体管等电子器件的衬底11、及设置在衬底11之上的配线层13。衬底11例如为硅衬底。在衬底11的上表面侧设置例如cmos型集成电路。

[0032]

存储单元阵列20具有在z方向上积层的多个电极层21、多个半导体柱23及源极线25。半导体柱23分别贯通电极层21而沿着z方向延伸。半导体柱23在一端电连接在源极线25。多个半导体柱23共用1个源极线25。另外,半导体柱23在另一端电连接在配线27。

[0033]

存储单元阵列30具有在z方向上积层的多个电极层31、多个半导体柱33及源极线35。半导体柱33分别贯通电极层31而沿着z方向延伸。半导体柱33在一端电连接在源极线35。多个半导体柱33共用1个源极线35。另外,半导体柱33在另一端电连接在配线37。

[0034]

存储单元阵列40具有在z方向上积层的多个电极层41、多个半导体柱43及源极线

45。半导体柱43分别贯通电极层41而沿着z方向延伸。半导体柱43在一端电连接在源极线45。多个半导体柱43共用1个源极线45。另外,半导体柱43在另一端电连接在配线47。

[0035]

电极层21、31及41在呈阶梯状设置的各端部电连接在接触插塞51。而且,电极层21、31及41经由接触插塞51及接触插塞53电连接在驱动电路10。接触插塞53以贯通各存储单元阵列20、30及40的方式设置。接触插塞53将积层在驱动电路10之上的各存储单元阵列中的电极层21、31及41电连接在配线层13中的配线15。

[0036]

另外,在各存储单元阵列设置贯通各存储单元阵列的其他接触插塞55。接触插塞55例如将驱动电路10和未图示的接口电路电连接。

[0037]

存储装置1还具备在各存储单元阵列中沿着z方向延伸的接触插塞60。接触插塞60在各存储单元阵列中例如以贯通多个电极层21的方式设置。接触插塞60例如相比于在z方向上积层的多个电极层21、31及41的z方向的全宽ws更长地延伸。接触插塞60例如包含钨等金属。

[0038]

如图1所示,在存储单元阵列20设置接触插塞60a,在存储单元阵列30及40分别设置接触插塞60b及60c。本说明书中,有将接触插塞60a、60b及60c统一表达为接触插塞60的情况。关于其他构成要素,也有同样地表达的情况。

[0039]

而且,在各存储单元阵列分别设置连接垫61及63。连接垫61设置在各存储单元阵列的下表面,连接垫63设置在各存储单元阵列的上表面。

[0040]

如图1所示,在存储单元阵列20和存储单元阵列30的边界,连接垫63a和连接垫61b相互连接地配置。在连接垫63a电连接着接触插塞60a。另一方面,在连接垫61b经由配线65b电连接着接触插塞60b。即,接触插塞60a和接触插塞60b经由连接垫63a及61b电连接。

[0041]

同样地,在存储单元阵列20和存储单元阵列30的边界,连接垫63b和连接垫61c相互连接地配置。而且,接触插塞60b和接触插塞60c经由连接垫63b及61c电连接。

[0042]

而且,在存储单元阵列20中,和半导体柱23连接的配线27连接在配线65a,配线65a电连接在接触插塞60a。同样地,在存储单元阵列30中,连接在半导体柱33的配线37经由配线65b电连接在接触插塞60b及连接垫61b。另外,存储单元阵列40中,连接在半导体柱43的配线47经由配线65c电连接在接触插塞60c及连接垫61c。

[0043]

这样,能够经由接触插塞60将积层在驱动电路10之上的各存储单元阵列中所含的半导体柱间相互连接。此外,经由接触插塞60相互连接的半导体柱,经由位于驱动电路10和存储单元阵列20之间的连接垫61a、或设置在存储单元阵列40的上表面的连接垫63c、未图示的上层配线及接触插塞53,连接在例如驱动电路10的未图示的读出放大器。

[0044]

本实施方式中,能够将存储单元阵列20、30及40中分别包含的半导体柱23、33及43相互连接,作为包含例如沿着各半导体柱配置的存储单元mc(参照图4)的1个存储器串动作。

[0045]

例如,若存储单元阵列20、30及40分别包含64层电极层,则存储装置1能够实现和积层有192层电极层的存储单元阵列同等的存储容量。例如,为了在连续地积层有192层电极层的积层体形成存储器孔,并在该存储器孔的内部形成半导体柱,需要极其高度的晶片制程技术。相对于此,存储装置1中,通过积层个别地形成的存储单元阵列20、30及40,并使用接触插塞60及连接垫61、63相互电连接,能够容易地实现和连续地积层有192层电极层的情况同等的存储容量。

[0046]

另外,在形成有贯通192层电极层的半导体柱的情况下,有因该半导体柱的电阻使得单元电流变小,难以从存储单元mc读出数据的担忧。本实施方式中,例如贯通64层电极层的半导体柱23、33及43并联连接,因此各半导体柱的电阻比贯通192层电极层的半导体柱低。因此,存储装置1能够抑制单元电流降低。

[0047]

此外,本实施方式并不限定于所述例,例如积层在驱动电路10之上的存储单元阵列可以是2个,另外,也可以积层4个以上的存储单元阵列。接着,参照图2~图4,对各存储单元阵列的构成进行详细说明。

[0048]

图2a及b是表示第1实施方式的存储装置1的存储单元阵列20的构成的示意俯视图。图2b是表示图2a中所示的区域mp的俯视图。存储单元阵列30及40具有和存储单元阵列20相同的构造。

[0049]

如图2a所示,电极层21在x方向上延伸,在z方向上积层,并且沿着y方向排列配置。在y方向上相邻的电极层21之间设置狭缝st,将电极层21相互电分离。另外,在x方向上的电极层21的端部设置阶梯状的引出部hup。而且,在电极层21的一部分设置接触区域ca。

[0050]

如图2b所示,在电极层21设置多个存储器孔mh。存储器孔mh贯通多个电极层21而沿着z方向延伸,且在该存储器孔mh的内部分别配置半导体柱23(参照图1)。而且,设置沿着y方向延伸的多个配线27。将y方向上相邻的2个电极层21分别贯通的多个半导体柱23中的1个连接在多个配线27中的1个。即,1个配线27由将沿着y方向排列的多个电极层21分别贯通的1个半导体柱23共用。

[0051]

另外,在接触区域ca设置接触孔ph。接触孔ph贯通多个电极层21而沿着z方向延伸。如图2b所示,在接触孔ph的内部设置接触插塞60a。接触插塞60a包含例如钨等金属,利用设置在接触孔ph内的绝缘膜67而与电极层21电绝缘。绝缘膜67例如为氧化硅膜。

[0052]

图3是表示存储单元阵列20的下表面的示意俯视图。如图3所示,在接触区域ca之间,多个配线27沿着x方向排列配置。配线27分别沿着y方向延伸。在接触区域ca,多个接触插塞60a沿着y方向排列配置。而且,在接触区域ca之间配置多个连接垫61a。

[0053]

连接垫61a设置在配线27之上,分别经由配线65a连接在任一个接触插塞60a。例如配置在接触区域ca之间的连接垫61a的数量和配置在其间的配线27的数量相同。配线65a经由接触插塞71连接在接触插塞60a。另外,配线65a经由接触插塞73连接在1个配线27。

[0054]

图4是表示存储单元阵列20的示意剖视图。此外,图4是将图1的上下颠倒的剖视图。另外,图4中,为了明确表示存储单元阵列20的构成,适当省略使各构成要素间电绝缘的绝缘膜。

[0055]

如图4所示,多个电极层21积层在源极线25之上。源极线25例如为沿着x方向及y方向延伸的板状导电层。源极线25例如具有积层有金属层25a和半导体层25b的构造。金属层25a例如为钨层,半导体层25b例如为多晶硅。电极层21例如为含有钨等的金属层。

[0056]

半导体柱23在积层方向(z方向)上贯通电极层21,在该半导体柱23的下端连接在源极线25。另外,半导体柱23的上端经由接触插塞26电连接在配线27。

[0057]

在电极层21和半导体柱23之间设置存储器膜29。存储器膜29具有在从电极层21朝向半导体柱23的方向上依序积层有例如第1氧化硅膜、氮化硅膜及第2氧化硅膜的构造,能够在该存储器膜29的内部保持电荷且从该存储器膜29的内部释放电荷。存储单元mc分别设置在半导体柱23贯通电极层21的部分,包含存储器膜29的一部分作为电荷保持部。

[0058]

如图4所示,接触插塞60a贯通多个电极层21及源极线25而沿着z方向延伸。接触插塞60a通过绝缘膜67与电极层21及源极线25电绝缘。

[0059]

接触插塞60a的下端电连接在连接垫63a。另外,接触插塞60a的上端经由中间配线69及接触插塞71、77电连接在配线65a。中间配线69设置为例如和配线27相同高度(level)。接触插塞77将接触插塞60a和中间配线69连接。接触插塞71将配线65a和中间配线69连接。而且,配线65a经由接触插塞73连接在1个配线27,经由接触插塞75电连接在连接垫61a。

[0060]

另外,存储单元阵列20还包含电连接在源极线25的接触插塞80。接触插塞80贯通多个电极层21而沿着z方向延伸。接触插塞80例如和接触插塞60a一起设置在接触区域ca。

[0061]

接触插塞80的下端电连接在源极线25。另外,接触插塞80的上端经由中间配线85、87、接触插塞91、93及95电连接在连接垫81。中间配线85及87分别设置为和配线65a及27相同高度。接触插塞91将接触插塞80和中间配线87连接。接触插塞93将中间配线85和中间配线87连接。而且,中间配线85经由接触插塞91电连接在连接垫81。另外,源极线25例如经由接触插塞97电连接在连接垫83。

[0062]

存储单元阵列30及40也同样地包含接触插塞80、连接垫81及83。如图1所示,积层存储单元阵列20、30及40时,各源极线25、35及45经由接触插塞80、连接垫81及83而电连接。即,在存储单元阵列20和存储单元阵列30的边界,存储单元阵列20的连接垫83和存储单元阵列30的连接垫81连接。另外,在存储单元阵列30和存储单元阵列40的边界,存储单元阵列30的连接垫83和存储单元阵列40的连接垫81连接。

[0063]

接着,参照图5~图10,对第1实施方式的存储装置1的制造方法进行说明。图5~图10是表示积层在驱动电路10之上的存储单元阵列20、30及40的制造过程的示意剖视图。

[0064]

如图5a所示,形成上表面具有凸部101的衬底110。凸部101例如通过选择性地蚀刻衬底110来形成。衬底110例如为硅衬底。

[0065]

如图5b所示,形成覆盖衬底110的上表面的绝缘膜103。绝缘膜103例如为使用lpcvd(low pressure chemical vapor deposition,低压化学气相沉积)形成的氮化硅膜。

[0066]

如图5c所示,在绝缘膜103之上形成绝缘膜105。绝缘膜105例如为以teos(tetraethyl orthosilicate,正硅酸四乙酯)作为原料的使用cvd(chemical vapor deposition,化学气相沉积)形成的氧化硅膜。

[0067]

如图5d所示,将绝缘膜105平坦化,使形成在凸部101之上的绝缘膜103的一部分露出。绝缘膜105例如使用cmp(chemical mechanical polishing,化学机械抛光)而平坦化。

[0068]

如图6a所示,在绝缘膜105之上、及凸部101之上形成绝缘膜107。绝缘膜107例如为使用teos-cvd形成的氧化硅膜。接着,形成从绝缘膜107的上表面到凸部101的接触插塞111。

[0069]

如图6b所示,在绝缘膜107之上形成绝缘膜109。绝缘膜109例如为使用teos-cvd形成的氧化硅膜。接着,选择性地去除绝缘膜109,形成配线115。配线115例如经由接触插塞111电连接在衬底110。

[0070]

如图6c所示,在绝缘膜109之上形成存储单元阵列20。存储单元阵列20包含在z方向上积层的多个电极层21、在z方向上贯通电极层21的多个半导体柱23、及源极线25。而且,存储单元阵列20包含分别连接在电极层21的接触插塞51、及连接在配线115的接触插塞53。而且,在未图示的部分形成接触插塞60a及80。

[0071]

如图7a所示,在存储单元阵列20之上形成绝缘膜121。绝缘膜121例如为使用teos-cvd形成的氧化硅膜。接着,在绝缘膜121中形成连接垫123。连接垫123例如经由接触插塞125电连接在接触插塞53。另外,在未图示的部分也同时形成连接垫61a及81(参照图4)。连接垫61a、81、123例如包含铜或铜合金。

[0072]

如图7b所示,将驱动电路10和存储单元阵列20贴合。例如使绝缘膜121的上表面和驱动电路10的上表面接触,并在300~400℃的温度及规定压力下接合。此时,连接垫123连接在驱动电路10侧的连接垫127。连接垫127例如也包含铜或铜合金。

[0073]

如图8a所示,去除衬底110。例如对衬底110的背面侧进行研磨或研削而薄膜化后,通过湿式蚀刻而选择性地去除。由此,使绝缘膜103露出,去除凸部101后,形成凹部131。在凹部131的底面,接触插塞111的上表面露出。

[0074]

如图8b所示,通过在凹部131的内部嵌入例如铜或铜合金等金属而形成连接垫133。此时,在未图示的部分也同时形成连接垫63a及83。

[0075]

连接垫133例如连接在接触插塞111。连接垫133例如具有上表面的宽度w

t1

大于下表面的宽度w

b1

的形状。相对于此,接触插塞111具有上表面的宽度w

t2

小于下表面的宽度w

b2

的形状。

[0076]

如图9所示,在存储单元阵列20之上贴合存储单元阵列30。存储单元阵列30是利用和存储单元阵列20相同的方法来形成。在图9中的存储单元阵列30的上表面侧形成连接垫133。在存储单元阵列20和存储单元阵列30的边界,在连接垫133连接连接垫123。另外,在未图示的部分,存储单元阵列20的连接垫63a和存储单元阵列30的连接垫61b连接(参照图1)。而且,存储单元阵列20的连接垫83和存储单元阵列30的连接垫81连接(参照图4),源极线25和源极线35电连接。

[0077]

如图10所示,在存储单元阵列30之上贴合存储单元阵列40。存储单元阵列40是利用和存储单元阵列20及30相同的方法形成。在图10中的存储单元阵列40的上表面侧形成连接垫135。连接垫135例如包含铝。即,连接垫135为最上层的配线,例如以能够通过导线结合连接在外部电路的方式形成。

[0078]

如图10所示,在存储单元阵列30和存储单元阵列40的边界,也在连接垫133连接连接垫123。另外,在未图示的部分,存储单元阵列30的连接垫63b和存储单元阵列40的连接垫61c连接(参照图1)。而且,存储单元阵列30的连接垫83和存储单元阵列40的连接垫81连接(参照图4),源极线35和源极线45电连接。

[0079]

所述制造过程中,通过在衬底110的上表面设置凸部101,能够在贴合后的各存储单元阵列的上表面形成连接垫。另外,只要以具有配线图案的方式形成凸部101,则能够形成连接垫及连结在该连接垫的配线。由此,能够省略贴合后的光刻及绝缘膜的蚀刻,能够简化存储装置1的制造过程。

[0080]

[第2实施方式]

[0081]

图11是表示第2实施方式的存储装置的存储单元阵列50的构成的示意俯视图。存储单元阵列50包含沿着y方向排列的电极层21a、21b及21c。电极层21a、21b及21c分别沿着x方向延伸,电极层21a和电极层21b之间、及电极层21b和电极层21c之间利用狭缝st分离。另外,电极层21a、21b及21c分别在z方向上积层,由沿着z方向延伸的多个存储器孔mh贯通。在各存储器孔mh的内部的设置半导体柱23(未图示)。

[0082]

存储单元阵列50包含在电极层21a、21b及21c之上沿着y方向延伸的多个配线27。配线27例如沿着x方向排列配置。配线27分别电连接在贯通电极层21a延伸的1个半导体柱、贯通电极层21b延伸的1个半导体柱、及贯通电极层21c延伸的1个半导体柱。

[0083]

在该例中,在狭缝st的内部配置接触插塞160。接触插塞160沿着z方向延伸,其长度长于在z方向上积层的各电极层21a、21b及21c的总高度。另外,接触插塞160分别经由接触插塞141电连接在1个配线27。即,数量和配线27相同的接触插塞160设置在狭缝st的内部。

[0084]

图12a及b是表示第2实施方式的存储装置的存储单元阵列50的示意图。图12a是表示存储单元阵列50的上表面的示意俯视图。图12b是表示沿着图12a中所示的12b-12b线的剖面的示意图。

[0085]

如图12a所示,在配线27之上设置多个连接垫140。连接垫140分别电连接在1个配线27。即,数量和配线27相同的连接垫140配置在沿着x方向排列的多个配线27的上方。

[0086]

如图12b所示,接触插塞160在狭缝st的内部沿着z方向延伸。接触插塞160相比于电极层21的积层宽度ws更长地延伸。另外,接触插塞160通过绝缘膜167与电极层21及源极线120电绝缘。

[0087]

接触插塞160在其下端连接在连接垫150。另外,接触插塞160在其上端经由接触插塞141电连接在1个配线27。而且,配线27经由接触插塞143电连接在连接垫140。结果,接触插塞160电连接在1个配线27及1个连接垫140。

[0088]

本实施方式中,多个存储单元阵列50例如积层在驱动电路10之上(参照图1)。存储单元阵列50是将图12b所示的构造的上下颠倒而进行积层。此时,1个存储单元阵列50的连接垫150连接在积层在其上的其他存储单元阵列50的连接垫140。由此,电连接上下积层的存储单元阵列50的半导体柱23。

[0089]

另外,本实施方式中,也经由未图示的接触插塞(例如图4中的接触插塞80)电连接上下积层的存储单元阵列50的源极线120。

[0090]

图13是表示第2实施方式的存储单元阵列50的制造过程的示意图。图13a~c是表示接触插塞160的形成过程的示意俯视图。

[0091]

如图13a所示,在电极层21间的狭缝st嵌入绝缘膜167。绝缘膜167例如为使用cvd形成的氧化硅膜。此时,在存储器孔mh的内部分别形成未图示的半导体柱23及存储器膜29。

[0092]

如图13b所示,以覆盖存储器孔mh及绝缘膜167的方式形成蚀刻掩模181,例如抗蚀膜。蚀刻掩模181具有位于狭缝st上的开口181a。然后,使用蚀刻掩模181将绝缘膜167选择性地去除,形成在狭缝st内沿着z方向延伸,且连通于成为连接垫150的部分(参照图6a及图12b)的接触孔185。

[0093]

如图13c所示,在接触孔185的内部形成接触插塞160。接触插塞160是嵌入接触孔185的内部的金属层,例如包含钨。

[0094]

图14是表示第2实施方式的变化例的存储单元阵列50的制造过程的示意图。图14a~c是表示接触插塞170的形成过程的示意俯视图。接触插塞170在狭缝st内相比于电极层21的积层宽度ws更长地延伸。

[0095]

如图14a所示,形成在电极层21间的狭缝st包含第1部分wp及第2部分np。第1部分wp的y方向的宽度w1大于第2部分np的y方向的宽度w2。

[0096]

如图14b所示,在狭缝st的内部形成绝缘膜167。绝缘膜167例如为使用cvd形成的氧化硅膜。绝缘膜167例如以具有闭合第2部分np,且在第1部分wp残留接触孔187的厚度的方式形成。换句话说,以第1部分wp的宽度w1与第2部分np的宽度w2的差大于接触插塞170的y方向的宽度的方式形成。

[0097]

如图14c所示,在接触孔187的内部形成接触插塞170。接触插塞170为嵌入接触孔187的内部的金属层,例如包含钨。

[0098]

图15是表示第2实施方式的其他变化例的存储单元阵列50的制造过程的示意剖视图。图15a~c是表示接触插塞180的形成过程的示意俯视图。接触插塞180在狭缝st内相比于电极层21的积层宽度ws更长地延伸。

[0099]

如图15a所示,形成在电极层21间的狭缝st例如具有圆形的开口,形成为多个接触孔ch在x方向上连结的形状。接触孔ch例如以沿着z方向延伸且连通于成为连接垫150的部分(参照图6a及图12b)的方式形成。接触孔ch例如以其直径rs大于接触插塞180的直径的方式形成。

[0100]

如图15b所示,在狭缝st的内部形成绝缘膜167。绝缘膜167例如为使用cvd形成的氧化硅膜。绝缘膜167例如以具有在接触孔ch内残留接触空间189的厚度的方式形成。

[0101]

如图15c所示,在接触空间189的内部形成接触插塞180。接触插塞180是嵌入接触空间189的内部的金属层,例如包含钨。

[0102]

[第3实施方式]

[0103]

图16是表示第3实施方式的存储装置1的制造过程的示意剖视图。图16a是表示例如将存储单元阵列20和存储单元阵列30贴合而成的晶片5的示意俯视图(参照图1)。图16b是沿着图16a所示的16b-16b线的示意剖视图。

[0104]

如图16a所示,晶片5例如包含沿着x方向延伸的气隙ag。气隙ag延伸至晶片5的外缘,以在其两端连通于外部的方式设置。

[0105]

如图16b所示,气隙ag设置在存储单元阵列20与存储单元阵列30的边界。即,气隙ag形成在贴合存储单元阵列20与存储单元阵列30的边界,成为残留于两者之间的空气的排出路径。由此,在存储单元阵列20与存储单元阵列30的边界形成所谓空隙,能够防止接合不良。

[0106]

气隙ag是通过在存储单元阵列20及存储单元阵列30中的任一个阵列、或两个阵列形成槽eg,并将两者贴合而形成。

[0107]

气隙ag例如设置在从晶片5切出的芯片之间的所谓切割区域kr。切割区域kr以包围包含存储单元mc及各配线的器件区域dr的方式设置。由此,能够提高器件区域dr的存储单元阵列间的接合面的密接性。

[0108]

图17是表示第3实施方式的变化例的存储装置1的制造过程的示意剖视图。图17a~c是表示相当于沿着图16a所示的16b-16b线的剖面的部分的示意图。

[0109]

如图17a所示,在将存储单元阵列20和驱动电路10贴合后,在存储单元阵列20的上表面形成凹部131及201。凹部131及201例如通过从存储单元阵列20去除衬底110而形成(参照图8a)。

[0110]

如图17b所示,在凹部131及201嵌入金属,形成连接垫133及金属图案205。连接垫133及金属图案205例如使用铜或铜合金形成。

[0111]

在该过程中,例如在存储单元阵列20的上表面形成比凹部131及201的深度厚的金属层。之后,例如使用cmp以残留嵌入凹部131及201的部分的方式去除金属层。

[0112]

此时,若金属图案205的面积相对于切割区域kr的表面积的比率大,则通过所谓凹形变形(dishing)而在切割区域kr形成槽eg。即,以在切割区域kr形成槽eg的方式,使金属图案205的面积相对于切割区域kr的表面积的比率,变得大于例如连接垫133的面积相对于存储单元阵列20的器件区域dr的面积的比率。

[0113]

如图17c所示,将存储单元阵列20和存储单元阵列30贴合。在器件区域dr中,例如将存储单元阵列20的连接垫133和存储单元阵列30的连接垫123连接。另一方面,在切割区域kr中,在槽eg的位置形成气隙ag。由此,能够避免在存储单元阵列间形成空隙,能够提高两者的密接性。

[0114]

而且,通过在晶片上分别呈直线状设置多个槽eg,并使之单向延伸,能够减轻晶片的翘曲。另外,像所述的那样,通过利用cmp时的凹形变形,不使用例如光刻及选择蚀刻等便能形成槽eg。由此,能够简化各存储单元阵列的制造步骤。

[0115]

图18是表示第3实施方式的其他变化例的存储装置1的制造过程的示意剖视图。图18a及b是表示相当于沿着图16a所示的16b-16b线的剖面的部分的示意图。

[0116]

如图18a所示,在气隙ag中,也可以在槽eg的整个内表面露出金属图案215的方式形成。即,金属图案215也可以x方向的宽度变得和槽eg的x方向的宽度大致相同的方式形成。由此,cmp时的凹形变形变大,能够较深地形成槽eg。结果,能够扩大气隙ag的z方向的宽度。金属图案215例如使用铜或铜合金形成。

[0117]

在图18b所示的例中,将存储单元阵列220和存储单元阵列230贴合。存储单元阵列220及230包含接触插塞223及233,接触插塞223及233的端面作为连接垫发挥功能。即,如图18所示,将存储单元阵列220和存储单元阵列230贴合时,也可直接连接存储单元阵列220的接触插塞233和存储单元阵列230的接触插塞223。另外,在形成在两者的边界的气隙ag的内表面露出金属图案215。

[0118]

在所述实施例中,在存储装置1从晶片5被切出并芯片化的情况下,在该芯片的外缘残留气隙ag的一部分。即,在第3实施方式的存储装置1中,在气隙ag的一部分露出的金属图案205相对于绝缘膜105的面积比,大于存储单元阵列间的边界的连接垫133相对于绝缘膜105的面积比。

[0119]

[第4实施方式]

[0120]

图19a及19b是表示第4实施方式的存储装置2的示意俯视图。图19a是表示存储装置2的存储单元mc的配置的俯视图。图19b是表示存储装置2的存储单元mc的俯视图。

[0121]

如图19a所示,存储装置2具备沿着x方向延伸的多个电极层321。电极层321沿着y方向排列配置。另外,电极层321隔着未图示的层间绝缘膜在z方向上积层。在y方向上相邻的电极层321间的空间mt嵌入绝缘体311。绝缘体311例如为氧化硅。

[0122]

存储装置2的存储器孔mh以在z方向上贯通绝缘体311的方式设置。另外,存储器孔mh以将绝缘体311分割成多个部分的方式形成。存储装置2还具备在z方向上贯通绝缘体311的接触孔sth。在接触孔sth的内部配置接触插塞330及340。另外,在接触孔sth的内部设置绝缘膜331,用来使接触插塞330及340与电极层321电绝缘。

[0123]

如图19b所示,在存储器孔mh的内部设置沿着z方向延伸的半导体柱310。半导体柱

310包含绝缘性芯313和半导体层315。绝缘性芯313例如为沿着z方向延伸的氧化硅。半导体层315覆盖绝缘性芯313的侧面,沿着z方向延伸。半导体层315例如为多晶硅。

[0124]

在存储器孔mh的内部还设置绝缘膜317。绝缘膜317设置在存储器孔mh的内壁和半导体柱310之间。绝缘膜317例如为氧化硅膜。

[0125]

如图19b所示,存储装置2的存储单元例如包含浮栅fg。浮栅fg以从覆盖存储器孔mh的内壁的绝缘膜317延伸至电极层321的内部的方式设置。在浮栅fg和电极层321之间设置绝缘膜323。

[0126]

浮栅fg以延伸至在z方向上积层的电极层321各自的内部的方式设置,沿着在z方向上延伸的存储器孔相互隔开配置。1个存储器孔mh设置在y方向上相邻的2个电极层321之间,在2个电极层321分别设置浮栅fg。2个浮栅fg相互独立地发挥功能。即,存储装置2中,针对位于设置在z方向的相同高度的电极层321之间的每个存储器孔mh,能够配置2个存储单元mc。

[0127]

在各存储单元mc中,位于半导体柱310和浮栅fg之间的绝缘膜317的部分作为隧道绝缘膜发挥功能。而且,位于电极层321和浮栅fg之间的绝缘膜323的部分作为阻挡绝缘膜发挥功能。

[0128]

图20是表示存储装置2的其他示意俯视图。如图20所示,在和电极层321交叉的y方向上设置多个位线350。位线350配置在存储器孔mh的上方,经由接触插塞351电连接在半导体柱310。

[0129]

如图20所示,接触孔sth沿着y方向排列配置。位线530未配置在接触孔sth的上方。各位线350经由配线333电连接在设置在接触孔sth的内部的接触插塞330。位线350电连接在多个接触插塞330中的任一个。

[0130]

图21是表示存储装置2的示意剖视图。图21是沿着图20所示的20a-20a线的剖视图,包含接触插塞330。此外,为方便起见,图21中省略使各要素间电绝缘的绝缘膜及绝缘体的图示。

[0131]

如图21所示,存储装置2包含积层在驱动电路10之上的多个存储单元阵列20、例如存储单元阵列20a、20b、20c及20d。存储单元阵列20的积层数为任意,并不限定于该例。

[0132]

各存储单元阵列20包含多个半导体柱310、接触插塞330、位线350及源极线370。各半导体柱310的一端电连接在位线350,另一端电连接在源极线370。为方便起见,图21中省略接触插塞351的图示。

[0133]

源极线370例如为沿着x方向及y方向延伸的板状导电体。电极层321积层在源极线370之上(参照19a)。另外,接触插塞330以通过设置在源极线370的贯通孔sh而沿着z方向延伸的方式设置。接触插塞330通过绝缘膜331与源极线370电绝缘。

[0134]

在各存储单元阵列20中,接触插塞330经由配线333电连接在1个位线350。如图21所示,配线333经由接触插塞339连接在位线350,经由接触插塞337连接在接触插塞330。

[0135]

而且,各存储单元阵列20的接触插塞330在z方向上串联连接。存储单元阵列20b及20c的各接触插塞330经由焊盘343及345分别连接在位于上下的接触插塞330。如图21所示,焊盘343经由接触插塞335电连接在配线333。焊盘345连接在接触插塞330的一端。

[0136]

焊盘343及345的配置并不限定于该例,例如也可以如图1及图3所示般设置在位线350和源极线370之间。

[0137]

存储单元阵列20d的接触插塞330经由焊盘345及接触插塞347而电连接在配线410。配线410例如经由设置在存储单元阵列20的周边的接触插塞53(参照图1)电连接在驱动电路10的读出放大器sa。结果,各存储单元阵列20的位线350经由接触插塞330并联连接在读出放大器sa。由此,不使流经各半导体柱310的单元电流降低,便能多段地积层存储单元阵列20,从而能够增加存储装置2的存储容量。

[0138]

图22是表示存储装置2的其他示意剖视图。图21是沿着图20所示的20b-20b线的剖视图,包含接触插塞340。为方便起见,图21中也省略使各要素间电绝缘的绝缘膜及绝缘体的图示。

[0139]

如图22所示,在各存储单元阵列20中,接触插塞340连接在源极线370。另外,接触插塞340经由配线333、接触插塞335及337电连接在焊盘343。另一方面,源极线370经由接触插塞349电连接在焊盘345。

[0140]

例如,存储单元阵列20b及20c的源极线370经由焊盘343及345电连接在位于上下的存储单元阵列20的源极线370。

[0141]

存储单元阵列20d的接触插塞340经由焊盘345及接触插塞349电连接在配线420。配线420例如经由设置在存储单元阵列20的周边的接触插塞53(参照图1)电连接在驱动电路10的驱动晶体管。结果,各存储单元阵列20的源极线370经由接触插塞340串联连接,电连接在驱动电路10。

[0142]

图23a及23b是表示第4实施方式的变化例的存储装置3的示意剖视图。图23a及23b分别为表示包含接触插塞330的剖面的示意图,图23b是表示与图23a不同的剖面的示意图。

[0143]

在图23a所示的例中,存储单元阵列20b的接触插塞330经由配线333电连接在位线350。另一方面,存储单元阵列20a、20c及20d的各接触插塞330未电连接在位线350。即,1个位线350经由串联连接的接触插塞330电连接在配线410b,进而连接在读出放大器sa。

[0144]

在图23b所示的例中,存储单元阵列20c的接触插塞330经由配线333电连接在位线350。另一方面,存储单元阵列20a、20b及20d的各接触插塞330未电连接在位线350。因此,1个位线350经由串联连接的接触插塞330电连接在配线410c。

[0145]

这样,在存储装置3中,多段地积层的存储单元阵列20中的1个位线350经由串联连接的接触插塞330而连接在1个读出放大器sa。由此,能不降低流经各半导体柱310的单元电流地,多段地积层存储单元阵列20,并且能提高数据从各存储单元mc的读出速度。

[0146]

像所述的那样,在本实施方式中,例示了经由串联连接的接触插塞330将多段地积层的存储单元阵列20的各位线350并联连接在读出放大器sa的例子、及将多段地积层的存储单元20中的1个位线350连接在1个读出放大器sa的例子,但实施方式并不限定于这些。例如可以根据各存储单元阵列20中的位线的数量、及接触孔sth的数量,经由串联连接的接触插塞330将多段地积层的存储单元20中的任意数量的位线350并联连接在读出放大器sa。

[0147]

对本发明的若干种实施方式进行了说明,但这些实施方式是作为例子而提出的,并非意图限定发明的范围。这些新颖的实施方式能够通过其他各种方式来实施,能够在不脱离发明主旨的范围内进行各种省略、替换、变更。这些实施方式或其变化包含在发明的范围或主旨内,并且包含在权利要求书所记载的发明及其均等的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1