一种RFID信号的解调电路的制作方法

一种rfid信号的解调电路

技术领域

1.本发明涉及一种信号解调电路,尤其是一种rfid信号的解调电路。

背景技术:

2.rfid电路中,解调过程是应答器与阅读器进行通讯的一个重要部分,解调效果直接影响双方通讯功能能否正常实现,但是目前的应答器在解调过程中,当阅读器端场强停止后,应答器端电感线圈上的调幅信号并不会立刻降为0v,而是一段时间内缓慢降为0v,这样导致解调出的信号宽度比阅读器发送的调制信号宽度大很多,解调后的信号宽度有时候会超出协议的允许范围,一旦设置超出允许范围,将会导致阅读器上每次发送的调制信号存在精度误差,从而使rfid芯片无法适配相应的阅读器,通常通过在rfid芯片内的cpu上增大辨别解调信号的宽度范围来解决这一问题,但是效果仍然不够理想。

技术实现要素:

3.本发明所要解决的技术问题是提供一种解调后的信号较小、使用可靠性较高的rfid信号的解调电路。

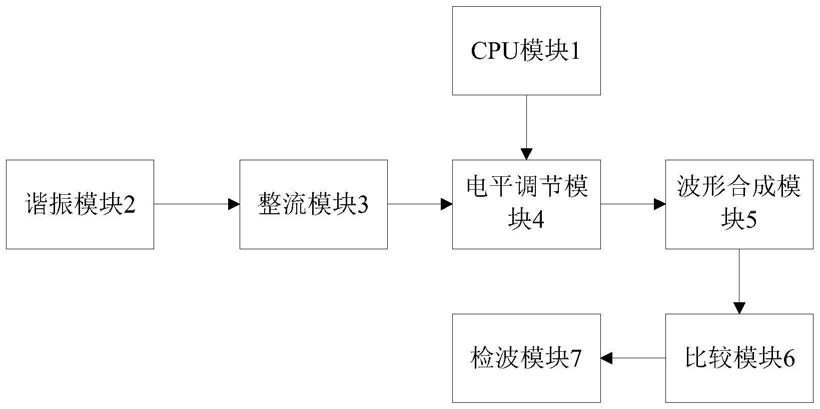

4.本发明解决上述技术问题所采用的技术方案为:一种rfid信号的解调电路,包括用于设置有电平控制信号输出端的cpu模块、谐振模块、整流模块、电平调节模块、波形合成模块、比较模块和检波模块,所述的谐振模块包括第一电感和第一电容,所述的整流模块包括第一pmos管、第二pmos管和第二电容,所述的电平调节模块包括第一nmos管和第一电阻,所述的波形合成模块包括第三pmos管和第四pmos管,所述的比较模块包括第五pmos管、第二nmos管、第六pmos管和第三nmos管,所述的检波模块包括第七pmos管、第二电阻和第三电容,所述的第一电感的一端、所述的第一电容的一端、所述的第一pmos管的源极、所述的第一电阻的一端、所述的第四pmos管的栅极及所述的第三pmos管的源极连接,所述的第一电感的另一端、所述的第一电容的另一端、所述的第二pmos管的源极、所述的第一nmos管的源极、所述的第三pmos管的栅极及所述的第四pmos管的源极连接,所述的第一pmos管的栅极、所述的第一pmos管的漏极、所述的第二pmos管的漏极、所述的第二pmos管的栅极、所述的第二电容的一端连接并形成内部电源端,所述的第二电容的另一端接地,所述的第一电阻的另一端与所述的第一nmos管的漏极连接,所述的第一nmos管的栅极与所述的cpu模块的电平控制信号输出端连接,所述的第三pmos管的漏极、所述的第四pmos管的漏极、所述的第五pmos管的栅极及所述的第二nmos管的栅极连接,所述的内部电源端、所述的第五pmos管是的源极、所述的第六pmos管的源极及所述的第七pmos管的源极连接,第五pmos管的漏极、所述的第二nmos管的漏极、所述的第六pmos管的栅极及所述的第三nmos管的栅极连接,所述的第六pmos管的漏极、所述的第三nmos管的漏极及所述的第七pmos管的栅极连接,所述的第七pmos管的漏极、所述的第二电阻的一端及所述的第三电容的一端连接并作为调制信号输出端,所述的第二nmos管的源极、所述的第三nmos管的源极、所述的第二电阻的另一端及所述的第三电容的另一端分别接地。

5.与现有技术相比,本发明的优点在于外部适配的阅读器发送电磁信号至第一电感,穿过第一电感的磁力线通过感应,在第一电感上产生交流电压,第一电感与第一电容构成谐振回路,第一pmos管和第二pmos管的作用是将双极性的交流电压变换为单极性的交流电压,再经过第二电容滤波,产生芯片内部电路正常工作所需的直流电压;cpu模块的电平控制信号输出端产生电平控制信号,通过电平控制信号控制第一nmos管栅极的电平高低,使解调时第一电阻并联进天线两端,改变第一电感两端的电压大小;第三pmos管和第四pmos管用于将接收到的半波信号转换成全波信号并发送至比较模块;第五pmos管、第二nmos管、第六pmos管和第三nmos管构成一个比较器,其作用为将前端信号转换为方波信号;第七pmos管、第二电阻和第三电容构成一个检波器,其作用为从调幅信号中取出调制信号;通过将对应的rfid阅读器的调幅信号按协议发送至该解调电路,对整体电路进行仿真测试及对取出的调制信号在示波器上进行实际波形显示,结果均表明,整体电路通过降低解调时电感线圈的电压,能够有效实现缩小解调宽度的效果,从而使解调后的信号较小,不容易超出协议允许的范围,增加了产品使用时的可靠性,并且降低了在rfid芯片内的cpu上设置参数范围的难度,有效减小工作量。

附图说明

6.图1为本发明的电路原理框图;图2为本发明的整体电路结构图;图3为测试过程中,电平控制信号端输出的电平信号一直处于低电平时解调信号在示波器上显示的解调结果;图4为测试过程中,电平控制信号端输出的电平信号在第四阶段处于高电平时第一电感的两端在示波器上显示的波形;图5为测试过程中,电平控制信号端输出的电平信号在第四阶段处于高电平时解调信号在示波器上显示的解调结果。

具体实施方式

7.以下结合附图实施例对本发明作进一步详细描述。

8.一种rfid信号的解调电路,包括用于设置有电平控制信号输出端的cpu模块1、谐振模块2、整流模块3、电平调节模块4、波形合成模块5、比较模块6和检波模块7,谐振模块2包括第一电感l1和第一电容c1,整流模块3包括第一pmos管p1、第二pmos管p2和第二电容c2,电平调节模块4包括第一nmos管n1和第一电阻r1,波形合成模块5包括第三pmos管p3和第四pmos管p4,比较模块6包括第五pmos管p5、第二nmos管n2、第六pmos管p6和第三nmos管n3,检波模块7包括第七pmos管p7、第二电阻r2和第三电容c3,第一电感l1的一端、第一电容c1的一端、第一pmos管p1的源极、第一电阻r1的一端、第四pmos管p4的栅极及第三pmos管p3的源极连接,第一电感l1的另一端、第一电容c1的另一端、第二pmos管p2的源极、第一nmos管n1的源极、第三pmos管p3的栅极及第四pmos管p4的源极连接,第一pmos管p1的栅极、第一pmos管p1的漏极、第二pmos管p2的漏极、第二pmos管p2的栅极、第二电容c2的一端连接并形成内部电源端,第二电容c2的另一端接地,第一电阻r1的另一端与第一nmos管n1的漏极连接,第一nmos管n1的栅极与cpu模块1的电平控制信号输出端连接,第三pmos管p3的漏极、第

四pmos管p4的漏极、第五pmos管p5的栅极及第二nmos管n2的栅极连接,内部电源端、第五pmos管p5是的源极、第六pmos管p6的源极及第七pmos管p7的源极连接,第五pmos管p5的漏极、第二nmos管n2的漏极、第六pmos管p6的栅极及第三nmos管n3的栅极连接,第六pmos管p6的漏极、第三nmos管n3的漏极及第七pmos管p7的栅极连接,第七pmos管p7的漏极、第二电阻r2的一端及第三电容c3的一端连接并作为调制信号输出端,第二nmos管n2的源极、第三nmos管n3的源极、第二电阻r2的另一端及第三电容c3的另一端分别接地。

9.对上述实施例的电路进行测试如下:rfid信号的解调电路解调来自rfid阅读器的调幅信号,该调幅信号分六个阶段:第一阶段为rfid阅读器停止场强,从0.0us到500.0us,持续500.0us;第二阶段为rfid阅读器输出调幅信号,从500.0us到900.0us,持续400.0us;第三阶段为rfid阅读器停止场强从900.0us到1500.0us,持续600.0us;第四阶段为rfid阅读器输出调幅信号,从1500.0us到1900.0us,持续400.0us;第五阶段为rfid阅读器停止场强从1900.0us到2500.0us,持续600.0us;第六阶段为rfid阅读器输出调幅信号,从2500.0us到2900.0us,持续400.0us。

10.如图3所示,此时第一电阻r1并未并入第一电感l1两端,不对第一电感l1的电压进行调制,第一电感l1的最高电压为5.0v,当电平控制信号输出端输出的电平控制信号为低电平时,第二阶段、第四阶段、第六阶段解调出的解调信号的脉宽都为500.0us;如图4所示,在应答器解调过程中,电平控制信号在第四阶段处于高电平,即此时第一电阻r1并入第一电感l1的两端,对第一电感l1的电压进行调制,调制后的第一电感l1的最高电压为4.0v;如图5所示,电平控制信号为低电平时的第二阶段、第六阶段解调出的解调信号的脉宽仍为500.0us,而电平控制信号为高电平时的第四阶段解调出的解调信号的脉宽变为400.0us;根据图4、图5可知,由于第四阶段,电平控制信号为高电平,使得第一电阻r1并入第一电感l1两端,引起第一电感l1两端的电压最高电平由原来的5.0v降低到4.0v,进而使得生成的全波信号最高电平也由原来的5.0v降低到4.0v,电平的降低,使得第四阶段的解调信号的脉宽由原来的500.0us降低到400.0us,减小了100.0us,达到了解调脉宽缩小的效果。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1