存储器以及其感测放大装置的制作方法

1.本发明是有关于一种存储器以及其感测放大装置,且特别是有关于一种可在低电源电压下正常工作的存储器以及其感测放大装置。

背景技术:

2.在电子装置的低电源应用中,极低的电源消耗是一个重要的特征,以可有效延长电池的使用时间。在集成电路中,大部分的电源消耗发生在电压泵电路所产生的电压转换动作中。因此,如何有效的减低电压泵电路的使用量,是降低功率消耗的重要关键。

3.在传统的存储器的读取动作中,感测放大装置中的位线调整器为了有效进行参考位线电压的调整动作,在低电源电压的工作条件下,会发生电源电压的电压值不够高的状况。因此,传统技术中,常利用电荷泵电路来在读取动作中以提升电源电压的电压值,以使位线调整器可维持正常动作。但这个电荷泵电路所执行的电压转换动作,却造成过度的功率消耗。

4.公开内容

5.本发明提供一种存储器以及其感测放大装置。其中的感测放大装置可在低电源电压下正常工作。

6.本发明的感测放大装置包括位线偏压调整器以及感测放大电路。位线偏压调整器接收电源电压以作为操作电压。位线偏压调整器包括第一放大器、第一晶体管以及第一电流源。第一放大器接收参考位线电压以及反馈电压,基于电源电压,根据参考位线电压以及反馈电压以产生调整后参考位线电压。第一晶体管具有第一端接收电源电压。第一晶体管的第二端产生反馈电压。第一晶体管的控制端接收调整后参考位线电压。第一电流源耦接在第一晶体的第二端与参考接地端间。感测放大电路接收电源电压以作为操作电压,用以根据调整后参考位线电压以产生感测结果。

7.本发明的存储器包括存储单元阵列以及如上所述的感测放大装置。感测放大装置耦接存储单元阵列,用以感测该存储单元阵列中的选中存储单元的存储单元电流以产生感测结果

8.基于上述,本发明的感测放大装置,通过在位线偏压调整器中设置为具有低阈值电压的第一晶体管,以使位线偏压调整器可基于未被升压的电源电压来产生有效的调整后参考位线电压,并使感测放大电路可根据调整后参考位线电压以产生正确的感测结果。如此一来,感测放大装置可基于低电源电压进行操作,达到节省功耗的需求。

附图说明

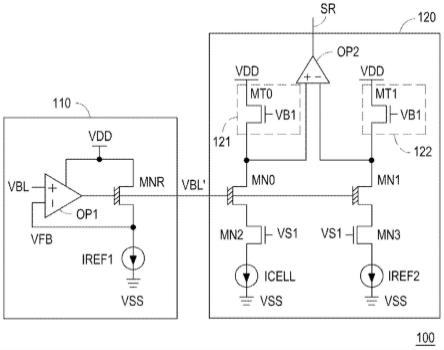

9.图1绘示本发明一实施例的感测放大装置的示意图。

10.图2绘示本发明另一实施例的感测放大装置的示意图。

11.图3绘示本发明实施例的感测放大装置中的感测放大电路的另一实施方式的示意图。

12.图4绘示本发明实施例的感测放大电路的局部剖面结构示意图。

13.图5绘示本发明另一实施例的感测放大装置的示意图。

14.图6绘示本发明一实施例的存储器的实施方式的示意图。

15.附图标记说明

16.100、200、500、630:感测放大装置

17.110、210、510:位线偏压调整器

18.120、220、300、520:感测放大电路

19.121、122、221、222、321、322:电流电压转换器

20.411、412、413、414:掺杂区

21.600:存储器

22.610:存储单元阵列

23.620:多工器

24.cme:共同端

25.de1、de2:差动端

26.g1、g2:栅极结构

27.hvpw:阱区

28.iref1、icell、iref2、ibias:电流源

29.mnr、mno~mn3、mt0、mt1、mpa、mpb、mna、mnb、mt0a、mt1a:晶体管

30.op1、op2、511:放大器

31.ox1、ox2:氧化层

32.r0、r1:电阻

33.sr:感测结果

34.vb1、vbh:偏压电压

35.vbl:参考位线电压

36.vbl’:调整后参考位线电压

37.vdd:电源电压

38.vfb:反馈电压

39.vs1:选择电压

40.vss:参考接地端

具体实施方式

41.请参照图1,图1绘示本发明一实施例的感测放大装置的示意图。感测放大装置100包括位线偏压调整器110以及感测放大电路120。位线偏压调整器110接收电源电压vdd以作为操作电压。位线偏压调整器110包括放大器op1、晶体管mnr以及电流源iref1。放大器op1接收参考位线电压vbl以及反馈电压vfb。放大器op1接收电源电压vdd以作为操作电压。放大器op1基于电源电压vdd,根据参考位线电压vbl以及反馈电压vfb以产生调整后参考位线电压vbl’。细节上,放大器op1可具有正输入端以接收参考位线电压vbl,并具有负输入端以接收反馈电压vfb。晶体管mnr具有第一端接收电源电压vdd;晶体管mnr的第二端产生反馈电压vfb;晶体管mnr的控制端接收调整后参考位线电压vbl’,其中,晶体管mnr的阈值电压

(threshold voltage)小于一般晶体管的阈值电压(等于基准值),例如,晶体管mnr可以为原生晶体管(native transistor)。电流源iref1则耦接在晶体管mnr的第二端与参考接地端vss间。

42.此外,感测放大电路120同样接收电源电压vdd以作为操作电压,用以根据调整后参考位线电压vbl’以产生感测结果sr。在本实施例中,感测放大电路120包括电流电压转换器121、122、放大器op2、晶体管mn0~mn3以及电流源icell、iref2。电流电压转换器121的一端接收电源电压vdd,电流电压转换器121的另一端耦接至晶体管mn0的第一端。电流电压转换器122的一端接收电源电压vdd,电流电压转换器122的另一端耦接至晶体管mn1的第一端。晶体管mn0、晶体管mn2以及电流源icell依序串接在电流电压转换器121以及参考接地端vss间。其中,晶体管mn0的控制端接收调整后参考位线电压vbl’,晶体管mn2作为选择开关,并根据选择电压vs1来被导通。另外,晶体管mn1、晶体管mn3以及电流源iref2依序串接在电流电压转换器122以及参考接地端vss间。其中,晶体管mn1的控制端接收调整后参考位线电压vbl’,晶体管mn3作为选择开关,并根据选择电压vs1来被导通。在本实施例中,电流源icell以及iref2分别提供存储单元电流以及参考电流。

43.电流电压转换器121、122可分别由晶体管mt0以及mt1来建构。晶体管mt0的第一端接收电源电压vdd晶体管mt0的第二端耦接至晶体管mn0的第一端;晶体管mt0的控制端接收偏压电压vb1。晶体管mt1的第一端接收电源电压vdd;晶体管mt1的第二端耦接至晶体管mn1的第一端;晶体管mt1的控制端接收偏压电压vb1。在本实施例中,晶体管mt0、mt1可均工作在线性区。

44.在本实施例中,当晶体管mn2、mn3根据选择电压vs1被导通时(此时选择电压vs1可等于电源电压vdd),电流电压转换器121以及122分别根据存储单元电流以及参考电流来产生第一电压以及第二电压。第一电压以及第二电压分别被提供至放大器op2的正输入端以及负输入端,放大器op2并根据比较第一电压以及第二电压来产生感测结果sr。

45.值得注意的,本实施例中的晶体管mn0以及mn1与晶体管mnr的阈值电压均可小于一般晶体管的阈值电压(等于基准值),例如,晶体管mnr、mno以及mn1可以同样皆为原生晶体管,并相对于其他晶体管,均具有相对低的阈值电压vth。如此一来,调整后参考位线电压vbl’可以等于参考位线电压vbl+vth。因此,本发明实施例中,感测放大装置100可以在具有低电压值的电源电压vdd下进行工作,不需要通过另外设置电荷泵电路来提升电源电压vdd的电压值,在电路成本以及功率消耗上,都可有效的被降低。也就是说,本发明实施例中的电源电压vdd,可以直接由非为电荷泵电路的电源供应器来提供。

46.以下请参照图2,图2绘示本发明另一实施例的感测放大装置的示意图。感测放大装置200包括位线偏压调整器210以及感测放大电路220。位线偏压调整器210包括由晶体管mpa、mpb、mna、mnb以及电流源ibias所构成的放大器、晶体管mnr以及电流源iref1。在细节上,晶体管mna、mnb形成差动对,晶体管mpa、mpb则形成主动负载。晶体管mna、mnb的控制端分别接收参考位线电压vbl以及反馈电压vfb,并分别根据参考位线电压vbl以及反馈电压vfb来产生第一电流以及第二电流。晶体管mpa、mpb所形成的主动负载耦接至差动对的二差动端de1、de2,其中主动负载可在差动端de2上根据第二电流产生调整后参考位线电压vbl’。电流源ibias耦接至差动对的共同端cme。电流源ibias用以提供一共同电流,其中上述的第一电流与第二电流的和等于电流源ibias提供的共同电流。

47.在本实施例中,感测放大电路220包括电流电压转换器221、222、放大器op2、晶体管mno~mn3以及电流源icell、iref2。其中,与图1实施例不相同的,本实施例中的电流电压转换器221、222分别为电阻ro以及r1。电阻ro以及r1可由集成电路中可用来形成电阻的任意材质来构成,例如多晶硅、n型或p型的掺杂区等,没有一定的限制。

48.值得一提的,本实施例中,位线偏压调整器210所包括的晶体管mpa、mpb、mna、mnb以及晶体管mnr均工作在饱和区,并可减低晶体管mpa、mpb、mna、mnb中的每一者的两端间的电压差,并减低电源电压vdd所需的电压值。以晶体管mn2与mn0的耦接端点等于0.7伏特,晶体管mn0的导通电压vth等于0.2伏特,且晶体管mpb第一端与第二端间的电压差等于0.1伏特为范例,电源电压vdd可以略大于1伏特即可使位线偏压调整器210正常工作。并且,位线偏压调整器210中的放大器也可利用不同的电路,但为本领域技术人员所熟知的放大电路来建构,没有特定的限制。例如,位线偏压调整器210中的放大器也可由与图2中由晶体管mpa、mpb、mna、mnb以及电流源ibias所构成的电路的互补型态来建构。

49.感测放大电路220动作细节与图1实施例中的感测放大电路120相类似,在此不多赘述。

50.以下请参照图3,图3绘示本发明实施例的感测放大装置中的感测放大电路的另一实施方式的示意图。感测放大电路300包括电流电压转换器321、322、放大器op2、晶体管mn0~mn3以及电流源icell、iref2。与图2的感测放大电路220的差别,本实施方式中的电流电压转换器321、322分别由晶体管mtoa以及mt1a所建构。其中,晶体管mtoa以及mt1a的电压耐受度,高于感测放大电路220中的晶体管mt0以及mt1的电压耐受度。并且,本实施例中的晶体管mt0a以及mt1a受控于偏压电压vbh。晶体管mtoa以及mt1a所接收的偏压电压vbh,可大于晶体管mt0以及mt1所接收的偏压电压vb1。

51.值得一提的,在本实施方式中,晶体管mtoa、mt1a以及晶体管mn0、mn1可皆设置在相同的阱区中。在此请同步参照图4,图4绘示本发明实施例的感测放大电路的局部剖面结构示意图。在图4中,晶体管mn0以及mt0a均设置在阱区hvpw中。以阱区hvpw为p型阱区为范例,阱区hvpw中可设置掺杂区411、412、413以及414。栅极结构g1以及氧化层ox1分别覆盖在掺杂区411、412间,并形成晶体管mn0。栅极结构g2以及氧化层ox2分别覆盖在掺杂区413、414间,并形成晶体管mt0a。掺杂区411可以为晶体管mn0的源极(或漏极),掺杂区412可以为晶体管mn0的漏极(或源极)。掺杂区413可以为晶体管mtoa的源极(或漏极),掺杂区414可以为晶体管mtoa的漏极(或源极)。

52.在本实施例中,氧化层ox2的厚度可以大于氧化层ox1的厚度。本发明实施例中,通过将晶体管mt0a、mt1a以及晶体管mn0、mn1设置在相同的阱区中,可以有效降低电路布局所需要的面积。

53.以下请参照图5,图5绘示本发明另一实施例的感测放大装置的示意图。感测放大装置500包括位线偏压调整器510以及感测放大电路520。在本实施例中,感测放大电路520的电路架构与图2中的感测放大电路220的电路架构相同,在此不多赘述。本实施例中的位线偏压调整器510包括放大器511、晶体管mnr以及电流源iref1。放大器511包括晶体管mna以及mnb。晶体管mna的第一端接收电源电压vdd,晶体管mna的控制端接收偏压电压vbias,晶体管mna的第二端耦接至晶体管mnb的第一端,并产生调整后参考位线电压vbl’。晶体管mnb的第二端耦接至参考接地电压vss,晶体管mnb的控制端接收反馈电压。在本实施例中,

偏压电压vbias相关于参考位线电压。

54.调整后参考位线电压vbl’被提供至晶体管mnr的控制端。晶体管mnr的第一端接收电源电压vdd,电流源iref1则串接在晶体管mnr的第二端与参考接地端vss间。

55.在本实施例中,晶体管mnr可以为原生晶体管,其中晶体管mnr的阈值电压可低于晶体管mna、mnb的阈值电压。

56.请参照图6,图6绘示本发明一实施例的存储器的实施方式的示意图。存储器600包括存储单元阵列610、多工器620以及感测放大装置630。存储单元阵列610通过多工器620以耦接至感测放大装置630。感测放大装置630可应用前述实施例的感测放大装置100、200或500来实施。存储单元阵列610则可以为静态随机存取存储单元阵列、动态随机存取存储单元阵列、闪存存储单元阵列、电阻式存储单元(resistive random-access memory,reram)阵列、相变化存储单元(phase change random-accessmemory,pcram)阵列或磁阻式随机存取存储单元(magnetoresistive random-access memory,mram)阵列。

57.本发明实施例的感测放大装置630,可直接接收非电压泵电路的电源产生器所提供的电源电压来作为操作电压,并正确的感测出存储单元阵列610的读出资讯,可有效降低所需的功率消耗。

58.综上所述,本发明提供利用具有低阈值电压的晶体管来建构位线偏压调整器。以使位线偏压调整器可接收不需升压的电源电压来作为操作电压,并有效产生调整后参考位线电压。感测放大电路则可根据调整后参考位线电压来执行存储单元电流的感测动作,并产生感测结果。如此一来,感测放大装置可在低电源电压的条件下正常动作,有效降低所需的功率消耗。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1