具有沟槽栅极的碳化硅器件的制作方法

[0001]

本公开涉及碳化硅器件,特别地涉及具有晶体管单元的碳化硅开关。

背景技术:

[0002]

用于变换电能的电路,例如在dc/ac转换器、ac/ac转换器或ac/dc转换器中以及在驱动电感负载的电路中,例如在电机驱动器电路中,可以包括作为开关的功率半导体器件。切换重电感负载可能触发lc振荡。另一方面,碳化硅(sic)的电介质击穿场强与硅相比为高。对于相同的标称阻塞电压(blocking voltage)能力,sic器件可以比等效硅器件显著薄,并且因此,sic器件的导通状态电阻可以显著更低。

[0003]

存在增加碳化硅器件的可能应用的范围的需要。

技术实现要素:

[0004]

本公开的实施例涉及一种碳化硅器件。该碳化硅器件包括从第一表面延伸到碳化硅本体中的条形沟槽栅极结构。该栅极结构具有沿着横向第一方向的栅极长度。该栅极结构的底表面和第一栅极侧壁经由该栅极结构的第一底部边缘连接。该碳化硅器件还包括第一导电类型的至少一个源极区。第二导电类型的屏蔽区跨栅极长度的至少20%与栅极结构的第一底部边缘接触。

附图说明

[0005]

附图被包括以提供对实施例的进一步理解,并且被并入本说明书中并构成本说明书的一部分。附图示出了碳化硅器件的实施例,并且与描述一起用于解释实施例的原理。在以下详细描述和权利要求书中描述了进一步的实施例。

[0006]

图1a-1d示出了根据实施例的具有源极区和屏蔽区的碳化硅器件的一部分的示意性平面图和竖直截面图。

[0007]

图2a-2d示出了具有包括以矩阵布置的深子区段的屏蔽区的根据实施例的碳化硅器件的一部分的示意性平面图和竖直截面图。

[0008]

图3a-3d示出了具有包括条形深区段的屏蔽区的根据实施例的碳化硅器件的一部分的示意性平面图和竖直截面图。

[0009]

图4a-4d示出了具有包括网格状深区段的屏蔽区的根据实施例的碳化硅器件的一部分的示意性平面图和竖直截面图。

[0010]

图5a-5b示出了具有包括横向分离的深子区段的屏蔽区的根据另一个实施例的碳化硅器件的一部分的示意性透视图。

[0011]

图6a-6c示出了根据另外的实施例的碳化硅器件的部分的示意性水平截面图。

具体实施方式

[0012]

在以下详细描述中,参考了附图,附图形成详细描述的一部分,并且其中通过图示

的方式示出了其中可以实践碳化硅器件的具体实施例。应当理解,在不脱离本公开的范围的情况下,可以利用其他实施例并且可以进行结构或逻辑改变。例如,针对一个实施例示出或描述的特征可以用在其他实施例上或与其他实施例结合使用,以产生另外的实施例。本公开旨在包括这样的修改和变化。使用具体语言描述了示例,所述具体语言不应被解释为限制所附权利要求的范围。附图没有按比例并且仅用于说明性目的。如果没有另外说明,则相应的元素在不同的附图中由相同的附图标记表示。

[0013]

术语“具有”、“含有”、“包括”、“包含”以及诸如此类是开放的,并且术语指示所述结构、元素或特征的存在,但不排除附加的元素或特征的存在。冠词“一”、“一个”和“该”旨在包括复数以及单数,除非上下文另有明确指示。

[0014]

术语“电连接的”描述了电连接的元件之间的永久性低电阻连接,例如相关元件之间的直接接触或经由金属和/或重掺杂半导体材料的低电阻连接。术语“电耦合的”包括适于信号和/或功率传输的一个或多个中间元件可以连接在电耦合的元件之间,例如,可控制以在第一状态中临时提供低电阻连接并且在第二状态中临时提供高电阻电解耦合的元件。欧姆接触是具有线性或几乎线性的电流-电压特性的非整流电学结。

[0015]

附图通过在掺杂类型“n”或“p”旁边指示

“-”

或“+”来说明相对掺杂浓度。例如,“n

-”

意味着比“n”掺杂区的掺杂浓度低的掺杂浓度,而“n+”掺杂区具有比“n”掺杂区高的掺杂浓度。相同的相对掺杂浓度的掺杂区不一定具有相同的绝对掺杂浓度。例如,两个不同的“n”掺杂区可以具有相同或不同的绝对掺杂浓度。

[0016]

相同导电类型且具有不同掺杂剂浓度的两个邻接掺杂区形成单极结,例如,沿着两个掺杂区之间的边界表面的n/n+或p/p+结。在单极结处,与单极结正交的掺杂剂浓度分布可以显示阶梯(step)或转折点,在该处,掺杂剂浓度分布从凹(concave)改变为凸(convex),或反之亦然。

[0017]

针对物理尺寸给定的范围包括边界值。例如,参数y从a到b的范围表示为。这也适用于具有如“至多”和“至少”之类的一个边界值的范围。

[0018]

来自化学化合物或合金的层或结构的主要成分是其原子形成化学化合物或合金的这样的元素。例如,镍和硅是硅化镍层的主要成分,并且铜和铝是铜铝合金的主要成分。

[0019]

术语“上方”不被解释为意味着“直接在其上”。而是,如果一个元素位于另一个元素“上方

”ꢀ

(例如,层在另一层“上方”或在衬底“上方”),则另外的部件(例如,另外的层)可以位于两个元素之间(例如,如果层在衬底“上方”,则另外的层可以位于层和所述衬底之间)。

[0020]

关于在碳化硅本体中形成的结构和掺杂区,如果在碳化硅本体的前侧处的第一表面和第二区之间的最小距离大于第一区和第一表面之间的最大距离,则第二区在第一区“下方”。第二区“直接”在第一区的“下方”,其中第一和第二区到第一表面中的垂直投影重叠。垂直投影是与第一表面正交的投影。

[0021]

区和/或结构可以在相同水平层中彼此横向分离。横向分离的区和/或结构也可以竖直分离(即,位于不同的水平层中)。在后一种情况下,分离的区和/或结构到水平投影平面中的正交投影横向分离。如果相关区和/或结构到水平投影平面中的正交投影横向重叠,则区和/或结构横向重叠。

[0022]

术语“功率半导体器件”是指具有至少30 v,例如100 v、600 v、3.3 kv或更多的高

电压阻塞能力并且具有至少1 a,例如10 a或更多的标称导通状态电流或正向电流(forward current)的半导体器件。

[0023]

根据实施例,碳化硅器件可以包括从第一表面延伸到碳化硅本体中的条形沟槽栅极结构。

[0024]

碳化硅本体可以具有相同形状和大小的两个基本上平行的主表面以及连接两个主表面的边缘的侧表面区域。例如,碳化硅本体可以是具有或不具有圆形边缘的多边形(例如,矩形或六边形)棱柱,或者是圆柱体。碳化硅本体可以具有沿着两个水平方向的表面延伸并且可以具有沿着垂直于水平方向的竖直方向的厚度。在下文中,水平方向也被称为横向方向。

[0025]

举例来说,碳化硅本体的材料可以是15r-sic(15r多型(polytype)的碳化硅),或者具有六边形多型的碳化硅,如2h-sic、4h-sic或6h-sic。除了主要成分硅和碳之外,碳化硅本体可以包括掺杂剂原子,例如氮(n)、磷(p)、铍(be)、硼(b)、铝(al)和/或镓(ga)。此外,碳化硅本体可以包括不想要的杂质,例如氢、氟和/或氧。

[0026]

条形沟槽栅极结构可以从碳化硅本体的前侧处的第一表面延伸到碳化硅本体中。栅极结构具有沿着横向第一方向的栅极长度和沿着横向第二方向的栅极宽度,横向第二方向与第一方向正交。栅极结构可以包括导电栅极电极。栅极结构还可以包括形成在栅极电极和碳化硅本体之间的栅极电介质。两个相对的第一和第二栅极侧壁可以是竖直的,或者可以相对于竖直方向稍微倾斜。第一和第二栅极侧壁可以逐渐变窄(taper)或者可以是平行的。

[0027]

通常,至少第一栅极侧壁可以基本上沿着碳化硅本体的晶体平面伸展,其中电荷载流子迁移率高(例如{11-20}或{1-100}晶体平面之一)。第一栅极侧壁可以是有源(active)侧壁,也就是说,晶体管沟道可以沿着第一栅极侧壁伸展。在一些实施例中,第二栅极侧壁也可以是有源侧壁(例如,在比如竖直沟槽栅极结构之类的平行的第一和第二栅极侧壁的情况下)。在其他实施例中,(例如在锥形(tapering)沟槽栅极结构的情况下),第二栅极侧壁可以是无源(inactive)侧壁。从碳化硅本体的前侧看,第一栅极侧壁在栅极结构的第一侧处并且第二栅极侧壁在栅极结构的相对的第二侧处。

[0028]

栅极结构的底部处的底表面经由第一和第二底部边缘连接第一和第二栅极侧壁。底表面可以包括水平部分。第一栅极侧壁可以包括直的区段。第一底部边缘可以连接底表面的水平部分和第一栅极侧壁的直的区段。因此,第二底部边缘可以连接底表面的水平部分和第二栅极侧壁的直的区段。底表面与第一栅极侧壁之间的第一底部边缘可以是锐角的或可以是圆形的和/或斜角的(beveled)(例如,具有钝角)。底表面与第二栅极侧壁之间的第二底部边缘可以是锐角的或可以是圆形的和/或斜角的(例如,具有钝角)。

[0029]

碳化硅器件还可以包括至少一个源极区。该至少一个源极区可以是第一导电类型的掺杂区。该源极区可以与栅极结构的第一栅极侧壁接触,或者可以与另外的栅极结构的第一栅极侧壁接触。换句话说:没有源极区、一个单个源极区或多个源极区可以沿着栅极结构的第一栅极侧壁形成。在没有源极区沿着栅极结构的第一栅极侧壁形成的情况下,至少一个源极区可以沿着另外的栅极结构形成。沿着相同栅极结构形成的源极区可以沿着第一方向彼此分离。沿着第一方向的每个源极区的长度可以是至少500 nm,例如至少1μm。

[0030]

碳化硅器件还可以包括屏蔽区。该屏蔽区可以是第二导电类型的掺杂区。第一导

电类型和第二导电类型是互补导电类型。第一导电类型可以是n型并且第二导电类型可以是p型。替代地,第一导电类型可以是p型并且第二导电类型可以是n型。

[0031]

屏蔽区跨栅极结构的栅极长度的至少20%与第一底部边缘接触。例如,屏蔽区可以沿着栅极结构的整个长度延伸。屏蔽区可以至少部分地沿着第一栅极侧壁延伸。根据其他实施例,屏蔽区跨越第一栅极侧壁的至少20%延伸。沿着第一底部边缘,屏蔽区可以至少在竖直地在源极区下方的区段中不存在。在屏蔽区与第一底部边缘接触的情况下,屏蔽区可以沿着第一栅极侧壁从第一表面竖直延伸到第一底部边缘。

[0032]

根据另一示例,屏蔽区可以跨相邻源极区之间的距离的至少30%延伸。

[0033]

屏蔽区还可以与第二栅极侧壁、与第二底部边缘和/或栅极结构的底表面接触。屏蔽区可以跨栅极结构的整个栅极长度与第二栅极侧壁和第二底部边缘接触。屏蔽区可以跨栅极结构的整个栅极长度沿着第二底部边缘与底表面的全屏蔽区段接触。屏蔽区可以在相邻源极区之间的区段中沿着第一底部边缘与底表面的部分屏蔽区段接触。

[0034]

在屏蔽区与第一底部边缘的大量区段接触的情况下,栅极结构的大量部分可以完全嵌入在屏蔽区中。由于屏蔽区可以针对施加到例如漏极电势之类的后侧电势的电势屏蔽栅极结构,所以屏蔽区沿着第一栅极侧壁的增加部分可以减少栅极到漏极电容c

gd

。屏蔽区可以电连接到前侧电势,例如源极电势。在该情况下,屏蔽部分相对于源极区的增加部分可以增加栅极到源极电容c

gs

。增加的c

gs

和减少的c

gd

显著地减少了关断振荡趋势。

[0035]

沿着第一表面的屏蔽区的较大部分可以提供形成在第一表面上的前侧电极与屏蔽区之间的较大的接触区域。较大的接触区域可以减少前侧电极和屏蔽区之间的欧姆接触电阻。另外,沿着第一表面的屏蔽区的较大区域部分可以进一步简化屏蔽区与前侧电极之间的可靠的低电阻欧姆接触的形成。结果,可以显著地改进本体二极管的浪涌电流强度(surge-current ruggedness),屏蔽区形成有漂移结构。较大的接触区域和前侧电极与屏蔽部分之间的接触的减少的欧姆电阻还可以对于减少接通期间的电流过冲、减少本体二极管损耗有贡献和/或在减少关断振荡趋势中有贡献。

[0036]

沿着第一栅极侧壁的屏蔽区的形成可以减少源极区的区域部分,并且因此减少总晶体管沟道宽度。减少的晶体管沟道宽度与相对于沿着第一方向形成在源极区之间的屏蔽区的这样的部分的晶体管沟道的改进的屏蔽相组合可以对于减少晶体管饱和电流有贡献并且因此可以改进短路鲁棒性。另外,底表面的完全屏蔽部分增加并且底表面的不完全屏蔽部分可以针对所有四个横向侧被有效地屏蔽。两种效果都可以进一步对增加栅极电介质可靠性有贡献。

[0037]

由于在高压器件中,例如在具有至少600 v、例如至少3 kv的电压阻塞能力的器件中,电压维持层的电阻主导导通状态损耗,所以晶体管沟道的可能略微增加的导通状态电阻可以忽略不计是可能的。另一方面,沿着第一栅极侧壁的大量部分的屏蔽区的形成可以显著地软化开关行为,可以改进本体二极管特性和/或可以增加短路耐用性。特别地,具有至少600 v,例如至少3 kv的电压阻塞能力的高电压器件可以受益于跨第一栅极侧壁的大量部分延伸的屏蔽区。

[0038]

根据实施例,屏蔽区可以跨栅极长度的至少30%,例如至少50%与第一底部边缘接触。屏蔽区的较大部分可以进一步减少c

gd

,可以进一步增加c

gs

和/或可以进一步改进器件可靠性。

[0039]

根据实施例,屏蔽区可以包括顶部屏蔽部分和深屏蔽部分。顶部屏蔽部分位于第一表面与深屏蔽部分之间。顶部屏蔽部分可以邻接(例如,直接邻接)第一表面。顶部屏蔽部分的竖直延伸可以大于栅极结构的竖直延伸。顶部屏蔽部分可以例如至少在一些位置处与第一底部边缘接触。

[0040]

顶部屏蔽部分可以沿着栅极结构的整个长度与栅极结构的第二底部边缘接触。深屏蔽部分可以形成在栅极结构的底表面和碳化硅本体的后侧处的第二表面之间的碳化硅本体的层中。

[0041]

深屏蔽部分的水平截面区域可以与顶部屏蔽部分的水平截面相同或基本上相同,其中相同注入掩模(implant mask)可以用于形成深屏蔽部分和顶部屏蔽部分。替代地,水平截面区域或顶部屏蔽部分和深屏蔽部分可以相当不同。在后一种情况下,不同的注入掩模可以限定深屏蔽部分和顶部屏蔽部分。

[0042]

顶部屏蔽部分和深屏蔽部分可以沿着竖直方向直接连接到彼此。顶部屏蔽部分和深屏蔽部分可以在如下意义上彼此重叠,限定深屏蔽部分的注入物(implant)的一个或多个范围末端(end-of-range)峰值可以位于顶部屏蔽部分内。深屏蔽部分可以沿着竖直方向连续。

[0043]

深屏蔽部分可以改进对晶体管沟道和对未直接嵌入屏蔽区中的栅极电介质的这种部分的屏蔽效果。晶体管沟道的改进的屏蔽可以减少dibl(漏极引起的势垒降低)。

[0044]

改进的横向屏蔽效果可以促进充分屏蔽,甚至在例如深屏蔽部分之类的屏蔽区的相对低的竖直延伸处。例如,通过省略具有大于1.3 mev的注入能量的(一个或多个)注入物,改进的横向屏蔽可以至少部分地补偿深屏蔽部分的竖直延伸的减少。例如,栅极底表面与深屏蔽部分的下边缘之间的竖直距离可以减少到至少50nm,例如至少300nm。

[0045]

根据实施例,顶部屏蔽部分和第一栅极侧壁之间的第一距离可以小于深屏蔽部分和第一栅极侧壁之间的第二距离。例如,顶部屏蔽部分的表面区段可以直接邻接源极区。深屏蔽部分可以具有沿着至少一个横向方向到源极区的横向距离和/或可以沿着至少一个横向方向与源极区横向重叠。

[0046]

根据实施例,顶部屏蔽部分可以包括分离区段。分离区段可以与第一栅极侧壁接触。分离区段可以从第一表面向下延伸至第一底部边缘。分离区段可以横向分离沿着栅极结构沿着第一方向形成的源极区。在该情况下,顶部屏蔽部分可以相对于所有四个横向侧屏蔽每个晶体管沟道。

[0047]

根据实施例,顶部屏蔽部分可以包括分离区段。分离区段可以位于源极区之间。例如,分离区段可以与第一栅极侧壁接触。沿着第一表面,分离区段和源极区可以覆盖沿着第一方向的栅极结构的第一栅极侧壁的连续部分。分离区段和源极区可以沿着第一表面完全覆盖第一栅极侧壁。

[0048]

分离区段和源极区可以具有沿着第二方向的相同的宽度。沿着第一表面,顶部屏蔽部分的分离区段和源极区可以彼此互补成第一连续区域而没有间隙。沿着第一栅极侧壁或在第一栅极侧壁的附近的另外的掺杂区的缺少可以通过使用相对简单的光掩模(photomask)来促进形成顶部屏蔽部分和源极区。

[0049]

根据实施例,碳化硅器件可以包括第一栅极结构和相邻的第二栅极结构。第一栅极结构和第二栅极结构中的每个可以被实现为前述栅极结构。第一栅极结构或第二栅极结

构甚至可以对应于前述栅极结构。

[0050]

分配给第一栅极结构的顶部屏蔽部分和源极区可以布置在第一栅极结构的第一栅极侧壁和第二栅极结构的第二栅极侧壁之间。

[0051]

特别地,没有具有源极区的导电类型并且通过欧姆路径与电压维持层电连接的另外的掺杂区与第一栅极结构和第二栅极结构之间的区域中的第一表面邻接是可能的。

[0052]

在第一表面处,第一栅极侧壁和第二栅极侧壁之间的区域可以填充有顶部屏蔽部分和源极区。特别地,第一栅极结构和第二栅极结构之间的区域可以被屏蔽部分和源极区的暴露表面完全填充。

[0053]

换言之,在第一栅极结构的第一栅极侧壁与第二栅极结构的第二栅极侧壁之间,顶部屏蔽部分与源极区可以沿着第一表面彼此互补成第二连续区域。第二连续区域包括第一表面中的顶部屏蔽部分的顶表面的另外的条形部分和第一连续区域。在相邻栅极结构之间的另外的掺杂区的缺少可以进一步简化顶部屏蔽部分和源极区的形成。

[0054]

根据实施例,沿着第一方向,通过在分离区段中的一个与源极区中的一个之间的过渡的横向掺杂剂分布可以包括平顶(plateau)区段。平顶区段可以反映沿着第一方向,用于源极区注入物的注入掩模中的开口可以比用于顶部屏蔽部分注入物的注入掩模的掩模列的长度窄。平顶区段的长度对应于用于顶部屏蔽部分注入物的掩模列的延伸与用于源极区注入物的掩模开口的延伸之间沿着第一方向的差。每个平顶区段的长度可以是至少50nm、200nm或甚至500nm。例如,在平顶区段中,掺杂剂浓度可以跨50nm或200nm或甚至500nm的距离改变不超过一个数量级。在平顶区段中,导电类型可以是分离区段的导电类型或源极区的导电类型,或者是本征的。平顶区段可以简化用于源极区和/或分离区段的形成的注入掩模的对准。

[0055]

根据实施例,碳化硅器件可以包括第一栅极结构和相邻的第二栅极结构。第一栅极结构和第二栅极结构可以体现为前述的栅极结构。第一栅极结构或第二栅极结构甚至可以对应于前述栅极结构。

[0056]

深屏蔽部分可以包括深区段。沿着第二方向,深区段可以与第一栅极结构的第一栅极侧壁横向分离。此外,每个深区段可以与第二栅极结构的第二栅极侧壁横向重叠。

[0057]

例如,碳化硅器件可以包括多个栅极结构。深屏蔽部分可以包括至少沿着第二方向彼此分离的多个深区段。沿着第二方向,每个深区段可以与两个相邻栅极结构中的第一栅极结构的第一栅极侧壁横向分离,并且可以与两个相邻栅极结构中的第二栅极结构的第二栅极侧壁横向重叠。

[0058]

根据实施例,深区段可以形成具有平行于第一方向的纵轴的连续条。深区段可以跨栅极长度的至少90%或跨整个栅极长度延伸。

[0059]

例如,碳化硅器件可以包括多个栅极结构和多个深区段。深区段可以沿着第二方向横向地分离。深区段可以形成具有平行于第一方向的纵轴的连续条。例如,每个深区段可以跨栅极长度的至少90%或跨整个栅极长度延伸。对于条形深区段,在没有沿着第一方向精细调整光掩模的情况下形成深区段进展可能是可能的。每个条形深区段可以对屏蔽形成在条形深区段的相对的纵向侧上的晶体管沟道有贡献。

[0060]

根据另一示例,深区段可以包括多个深子区段。深子区段可以沿着第一方向横向地分离。深子区段可以以排(line)和行(row)的矩阵状布置,其中行可以与排正交地伸展。

深子区段中的两个深子区段沿着第二方向形成在每个源极区的相对侧上。这样,每个晶体管沟道可以由形成在相对横向侧上的至少两个深子区段来屏蔽。

[0061]

在分配给相邻栅极结构的源极区彼此移位例如相邻源极区之间的中心到中心距离的一半的情况下,每个晶体管沟道可以由形成在四个相对横向侧上的四个深子区段屏蔽。在屏蔽区仅具有小的或可忽略不计的屏蔽效果的区中,可以不存在深子区段。利用矩阵状布置的深区段,保持导通状态电流的高的横向扩展可以是可能的。矩阵状布置的深子区段可以保持深子区段对碳化硅器件的例如导通状态电阻之类的其他电特性的小的可能的不利影响。

[0062]

根据另一实施例,深屏蔽部分的水平截面可以包括具有网格开口的网格。每个网格开口可以横向地包围一个源极区的至少一部分。例如,每个网格开口可以横向地包围一个完整的源极区。根据另一示例,每个网格开口可以包围沟道侧壁区段。例如,深屏蔽部分的水平截面可以或多或少地与多个栅极沟槽下方的顶部屏蔽部分的水平截面相同,并且可以通过使用相同的注入掩模来形成。网格状深屏蔽部分可以促进高屏蔽效果。

[0063]

根据另一实施例,碳化硅器件可以包括第一栅极结构和相邻的第二栅极结构。第一栅极结构和第二栅极结构可以体现为前述的栅极结构。第一栅极结构或第二栅极结构甚至可以对应于前述的栅极结构。

[0064]

屏蔽区可以跨第一栅极结构的栅极长度与第一底部边缘接触。不需要屏蔽区沿着第一方向的对准是可能的。因此,制造过程可以是高效的。

[0065]

根据实施例,源极区可以沿着第二栅极结构的栅极长度延伸。不需要源极区沿着第一方向的对准是可能的。因此,制造过程可以是高效的。

[0066]

根据另一实施例,碳化硅器件可以包括第二导电类型的本体区和第一导电类型的电流扩散区。本体区和电流扩散区可以形成在碳化硅本体中。本体区可以将源极区和电流扩散区分离。

[0067]

在碳化硅器件的导通状态下,可以在本体区中形成晶体管沟道。晶体管沟道可以是沿着栅极结构形成的反型层(inversion layer)。反型层促进在导通状态下在源极区与电流扩散区之间的单极电荷载流子流。

[0068]

根据另一实施例,碳化硅器件可以包括在碳化硅本体的第二表面和栅极结构之间的漂移结构。漂移结构可以包括电压维持结构。电压维持结构可以包括具有至少4μm、12μm、20μm或甚至至少100μm的竖直延伸的轻掺杂漂移区带。最小竖直延伸可以取决于碳化硅器件的期望阻塞能力。例如,对于650v(或1.2 kv或1.7 v或3.3 kv或6.5 kv)的期望阻塞能力,漂移区带的竖直延伸可以是至少4μm(或分别是至少8μm或至少12μm或至少20μm或至少40μm)。替代地或者此外,电压维持结构可以包括补偿结构,例如超级结(superjunction)结构。

[0069]

屏蔽区和漂移结构可以形成pn结。pn结作为本体二极管或作为本体二极管的部分可以是有效的,当碳化硅器件被反向偏置时,其处于正向传导模式中。沿着第一表面的屏蔽区的大接触区域可以促进屏蔽区与前侧电极之间的低欧姆接触,并且可以改进本体二极管的电特性。

[0070]

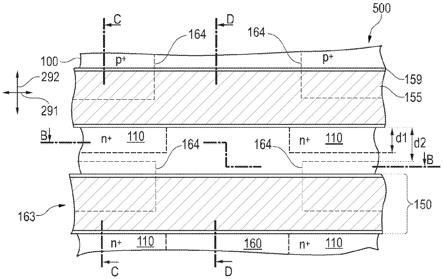

图1a-1d示出了具有碳化硅本体100的碳化硅器件500的一部分。例如,碳化硅器件500可以是或可以包括igfet(绝缘栅极场效应晶体管),例如mosfet(金属氧化物半导体

fet),或mcd(mos控制二极管)或igbt(绝缘栅极双极晶体管)。

[0071]

碳化硅本体100可以包括单晶碳化硅或由单晶碳化硅组成,例如包括主要成分硅和碳的碳化硅晶体。碳化硅晶体可能包括不想要的杂质,如氢和/或氧和/或预期的杂质,例如掺杂剂原子。碳化硅晶体的多型可以是15r,或者可以是六方晶系(hexagonal),例如2h、6h或4h。碳化硅本体100可以包括通过外延生长生长的碳化硅层或由其组成。

[0072]

碳化硅本体100的前侧处的第一表面101可以是平面的或有棱纹的(ribbed)。第一表面101的平均平面(mean plane)沿着水平方向延伸。平面的第一表面101的平均平面与平面的第一表面101相同。在非平面的第一表面101的情况下,例如在有棱纹的第一表面101的情况下,平均平面可以是平面最小二乘(least square)平面。平面最小二乘平面的位置和取向被限定为使得有棱纹的第一表面101的表面点与平面最小二乘平面的偏差的平方的和具有最小值。竖直方向104与水平方向正交,例如平行于垂直于(normal onto)平均平面的表面。在下文中,水平方向也被称为横向方向。

[0073]

竖直方向104可以与主晶格(lattice)方向一致或者可以相对于主晶格方向倾斜偏轴(off-axis)角,其中偏轴角可以在从2

°

至8

°

的范围内,特别是4

°

。在碳化硅本体100的后侧处,第二表面可以平行于平面的第一表面101或平行于有棱纹的第一表面101的最小二乘平面延伸。

[0074]

晶体管单元tc形成在碳化硅本体100的前侧处。漂移结构130在晶体管单元tc和第二表面之间横向延伸通过碳化硅本体100。漂移结构130可以包括电压维持结构,例如轻掺杂漂移区带和/或补偿结构,例如超级结结构。

[0075]

每个晶体管单元tc包括第一导电类型的源极区110和第二导电类型的本体区120。本体区120和漂移结构130形成第一pn结pn1。本体区120和源极区110形成第二pn结pn2。本体区120的竖直延伸对应于晶体管单元tc的沟道长度并且可以在从0.2μm到1.5μm的范围内。

[0076]

条形沟槽栅极结构150沿着横向第一方向291延伸。至少一个栅极结构150与晶体管单元tc的源极区110和本体区120接触。栅极结构150包括导电栅极电极155,其可以包括重掺杂多晶硅层和/或含金属层或者由重掺杂多晶硅层和/或含金属层构成。栅极电介质159沿着栅极结构150的至少一侧将栅极电极155与碳化硅本体100分离。栅极电介质159可以包括热生长或沉积的氧化硅、氮化硅、氮氧化硅、另一沉积的电介质材料或其任意组合或由热生长或沉积的氧化硅、氮化硅、氮氧化硅、另一沉积的电介质材料或其任意组合构成。栅极电介质159的厚度可以被选择为获得具有在从1.0 v到8 v的范围内的阈值电压的晶体管单元tc。栅极结构150可以排他地包括栅极电极155和栅极电介质159,或可以包括除栅极电极155和栅极电介质159之外的另外的导电的和/或电介质结构。

[0077]

栅极结构150可以是等间隔的和/或可以具有均匀的栅极宽度w0。相邻栅极结构150之间的中心到中心距离可以在从0.5μm到10μm的范围内,例如在从1μm到5μm的范围内。栅极结构150的栅极长度l0可以高达若干毫米。栅极结构150的竖直栅极延伸v0可以在从0.3μm至5μm的范围内,例如在从0.5μm至2μm的范围内。

[0078]

栅极结构150中的每个的相对的第一和第二栅极侧壁151、152可以基本上沿着竖直方向104伸展或可以相对于竖直方向104倾斜倾斜角。在后一种情况下,栅极结构150可以具有平行的第一和第二栅极侧壁151、152,或者栅极结构150可以随着到第一表面101的逐

渐增加的距离而逐渐变窄。栅极侧壁151、152与竖直方向104之间的倾斜角可以根据晶轴的对准和/或根据偏轴角来选择。

[0079]

例如,第一栅极侧壁151和竖直方向104之间的倾斜角的绝对值可以偏离偏轴角的绝对值不超过

±1°

(例如,在4h-sic的情况下,倾斜角可以从至少3

°

变动到至多5

°

)。然而,倾斜角在取向上可以偏离偏轴角。与第一栅极侧壁151相对的第二栅极侧壁152与竖直方向104之间的倾斜角可以与第一栅极侧壁151的倾斜角相等或相对地定向。倾斜角越大,从第一表面101开始的锥形的栅极结构150变得越窄。

[0080]

通常,至少第一栅极侧壁151可以基本上沿着碳化硅本体100的晶体平面伸展,其中电荷载流子迁移率是高的(例如{11-20}或{1-100}晶体平面之一)。第一栅极侧壁151可以是有源侧壁,也就是说,晶体管沟道可以沿着第一栅极侧壁151伸展。在一些实施例中,第二栅极侧壁152也可以是有源侧壁(例如,在竖直沟槽栅极结构150的情况下)。在其他实施例中,(例如在锥形沟槽栅极结构150的情况下),第二栅极侧壁152可以是无源侧壁。

[0081]

栅极结构150的底部处的底表面158连接第一和第二栅极侧壁151、152或形成第一栅极侧壁151和第二栅极侧壁152之间的连接的至少部分。底表面158可以包括水平部分。每个栅极结构151的底表面158和第一栅极侧壁151可以经由第一底部边缘156连接。每个栅极结构150的底表面158和第二栅极侧壁152可以经由第二底部边缘157连接。第一底部边缘156可以是锐角的或者可以是圆形的和/或斜角的。第二底部边缘157可以是锐角的或可以是圆形的和/或斜角的。

[0082]

在图1a中,在两个相邻栅极结构150之间的碳化硅本体100的一部分中形成多个隔离的(德语:voneinander separierten)源极区110。沿着第一方向291的源极区110的横向长度l1可以是至少500nm,例如至少1μm。

[0083]

屏蔽区160的分离区段161可以沿着第一方向291在第一表面101处横向分离相邻的源极区110。分离区段161的横向宽度w2和源极区110的横向宽度w1可以相等。在相同的两个栅极结构150之间形成的分离区段161和源极区110可以在第一表面101的平面中彼此互补成第一连续区域410。第一连续区域410不包括间隙。

[0084]

图1b示出了形成在两个相邻的栅极结构150之间的一个单个源极区110。源极区110可以沿着整个栅极长度l0延伸而没有任何中断。换句话说,源极区110可以从栅极结构150的一个纵向端延伸到相对的纵向端。沿着没有源极区110的另一个栅极结构150,屏蔽区160可以沿着整个栅极长度l0延伸而没有任何中断。

[0085]

屏蔽区160可以沿着一个或多个另外的栅极结构150从相关栅极结构150的一个纵向端延伸到相对的纵向端。

[0086]

第一栅极侧壁151的沟道侧壁区段153从源极区110向下延伸到第一底部边缘156。

[0087]

屏蔽区160从第一表面101延伸到碳化硅本体100中,如图1c和1d中所示。屏蔽区160可以跨栅极长度l0和跨竖直栅极延伸v0与无源第二栅极侧壁152直接接触。沿着第二栅极侧壁152,屏蔽区160从第一表面101向下延伸到栅极结构150下方。屏蔽区160的第一竖直延伸v1大于竖直栅极延伸v0。例如,屏蔽区160的下边缘与栅极底表面158之间的竖直距离v3可以是至少50nm,例如至少300nm。

[0088]

屏蔽区160包括本体区120和无源第二栅极侧壁152之间的区段。本体区120和屏蔽区160可以形成单极结。屏蔽区160可以包括沿着第一方向291分离相邻的源极区120的分离

区段161。分离区段161在沟道侧壁区段153外部与第一栅极侧壁151直接接触。

[0089]

屏蔽区160中的最大掺杂剂浓度可以高于本体区120中的最大掺杂剂浓度。屏蔽区160中的竖直掺杂剂浓度分布可以在栅极结构150下方的位置处具有局部最大值。沿着第二栅极侧壁152,屏蔽区160中的掺杂剂浓度可以更高,即是沿着第一栅极侧壁151的本体区120中的掺杂剂浓度的至少十倍高。

[0090]

在图2a-2d中,屏蔽区160包括顶部屏蔽部分168和深屏蔽部分169。深屏蔽部分169和顶部屏蔽部分168沿着竖直方向104彼此连接。

[0091]

顶部屏蔽部分168的竖直延伸v2大于竖直栅极延伸v0。深屏蔽部分169包括多个深子区段164,其沿着平行排和平行行布置,其中行与排正交地伸展。沿着水平第二方向292,每个深子区段164形成在两个相邻的源极区110之间。深子区段164可以与源极区110横向地分离。沿着水平第一方向291,相同行的相邻的深子区段164横向地分离。沿着第一方向291的深子区段164的水平长度可以等于、小于或大于沿着第一方向291的源极区110的长度。

[0092]

例如,顶部屏蔽部分168可以将栅极电介质和晶体管沟道的横向屏蔽改进到如下程度:使得如所示的参考源极区110的边缘沿着第一方向291对称地撤回(withdraw)深子区段164是可能的。在该情况下,深子区段164的水平长度小于源极区110的长度。

[0093]

顶部屏蔽部分和第一栅极侧壁151之间的第一距离d1可以小于深屏蔽部分168和第一栅极侧壁151之间的第二距离d2。

[0094]

漂移结构130可以包括第一导电类型的漂移区带131。漂移区带131形成电压维持结构,其中漂移区带131中的掺杂剂浓度和竖直延伸可以被选择为使得碳化硅器件500在碳化硅器件500的关断状态中提供标称阻塞电压能力。漂移区带131可以形成在通过外延生长生长的层中。漂移区带131中的平均净掺杂剂浓度可以例如在从1e15 cm-3

至5e16 cm-3

的范围内。根据另一示例,漂移结构130可以包括补偿结构,例如超级结结构。

[0095]

重掺杂接触部分139可以形成在漂移结构130和直接邻接碳化硅本体100的第二表面102的后侧电极之间。重掺杂接触部分139和后侧电极形成低电阻欧姆接触。接触部分139可以具有与漂移区带131相同的导电类型、相反的导电类型,或者可以包括两种导电类型的区带。

[0096]

漂移结构130可以包括电流扩散区137。电流扩散区137可以形成在本体区120和例如漂移区带131之类的电压维持结构之间。电流扩散区137可以与本体区120接触。电流扩散区137可以横向分离相邻的深子区段164。电流扩散区137的部分可以直接形成在深屏蔽部分169下方。电流扩散区137具有比漂移区带131高的平均掺杂剂浓度并且可以促进导通状态电流的更好的横向扩散。

[0097]

限定深子区段164和/或源极区110的注入掩模可以具有圆形开口,例如,椭圆形或圆形开口。因此,深子区段164和/或源极区110的水平截面区域可以包括圆形段、椭圆形段、圆形和/或椭圆形。限定顶部屏蔽部分168的注入掩模可以包括圆形柱,例如椭圆形或圆形柱。因此,顶部屏蔽部分168中的开口的水平截面区域可以是圆形段、椭圆形段、圆形和/或椭圆形。

[0098]

碳化硅本体100的前侧处的第一负载电极310与源极区110、本体区120和屏蔽区160电连接。栅极电极155可以电连接到碳化硅本体100的前侧处的栅极金属化。栅极金属化形成或电连接或耦合到栅极端子。

[0099]

层间电介质210的部分将栅极结构150中的栅极电极155和第一负载电极310分离。第一负载电极310可以形成第一负载端子或者可以与第一负载端子电连接或电耦合到第一负载端子,第一负载端子可以是mcd的阳极端子或mosfet的源极端子。

[0100]

第二负载电极320与接触部分139形成低电阻欧姆接触。第二负载电极320可以形成第二负载端子或者可以与第二负载端子电连接或电耦合到第二负载端子,第二负载端子可以是mcd的阴极端子或mosfet的漏极端子。

[0101]

所示的碳化硅器件500是n沟道sic tmosfet,其中第一负载电极310形成或电连接或耦合到源极端子s,并且其中第二负载电极320形成或电连接或耦合到漏极端子d。碳化硅器件500包括多个晶体管单元tc和多个栅极结构150。晶体管单元tc可以并联地电连接。

[0102]

在图3a-3d中,深屏蔽部分169的深区段163形成具有平行于水平第一方向291的纵轴的连续条带。

[0103]

在图4a-4d中,深屏蔽部分169的水平截面区域形成具有网格开口167的网格。每个栅极开口167形成在源极区110的周围。

[0104]

图5a-5b示出了具有沿着第一栅极侧壁151的沟道侧壁区段153形成的源极区110的碳化硅器件500的透视图。深屏蔽部分169包括点状深子区段164。屏蔽区160包括沿着第一表面101形成的重掺杂接触区段162。

[0105]

图6a和6b涉及具有多个栅极结构150的碳化硅器件500。多个源极区110沿着栅极结构150的第一栅极侧壁151形成。沿着第一表面101,屏蔽区的顶部屏蔽部分168与源极区110彼此互补成两个相邻的栅极结构150之间的第二连续区域400。

[0106]

在图6a中,源极区110以排和行的矩阵状布置,其中行与排正交地伸展。换句话说,源极区110形成在棋盘的黑色中和白色域中。

[0107]

在图6b中,相邻栅极结构150的源极区110彼此位移沿着第一方向291的相邻源极区110之间的中心到中心距离的一半。换句话说,源极区110可以仅形成在棋盘的“白色”域中。

[0108]

在图6c中,每个源极区110沿着第一类型的栅极结构150的整个栅极长度延伸,并且沿着第二类型的栅极结构150的第一栅极侧壁151完全不存在。第一类型的和第二类型的栅极结构150可以形成规则图案。例如,可以在每对第二类型的栅极结构150之间(不接触源极区110)形成一个、两个、三个或更多第一类型的栅极结构150(与源极区110接触)。

[0109]

为了说明,已经关于碳化硅器件描述了各种情形。类似的技术可以在基于用于半导体本体的其他种类和类型的化合物半导体材料的半导体器件中实现,其他种类和类型的化合物半导体材料例如是氮化镓(gan)或砷化镓(gaas)等。

[0110]

为了说明,已经关于没有集成的肖特基二极管的碳化硅器件描述了各种情况。一些实施例可以与前侧电极和第一导电类型的二极管区之间的肖特基接触组合。二极管区可以在相邻的栅极结构之间从第一表面延伸到漂移结构。替代地或附加地,分离区段可以横向地分离肖特基接触与源极区。例如,p掺杂的分离区段可以横向地将n掺杂的二极管区与n掺杂的源极区分离。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1