半导体装置及半导体系统的制作方法

1.本发明涉及一种作为功率器件等有用的半导体装置及具备该半导体装置的半导体系统。

背景技术:

2.氧化镓作为新一代半导体材料备受关注。氧化镓作为带隙较大且能够实现高耐压强电流半导体器件的材料而备受期待,以加大反向耐压且进一步降低正向上升电压等为目的,进行各种研究。

3.近年来,正在研究具有沟槽的半导体器件。作为β-ga2o3的沟槽型半导体器件,例如公开有专利文献1~3所记载的半导体器件。另外,作为α-ga2o3的沟槽型半导体器件,例如公开有专利文献4及5所记载的半导体器件。

4.然而,在对氧化镓等的结晶性氧化物半导体形成沟槽的情况下,由于具有与其他半导体材料不同的蚀刻特性,因此难以在沟槽底面上形成能够期待电场缓和的曲率半径为100nm以上的圆弧部。例如,当在现有的干蚀刻条件下强制地对结晶性氧化镓进行蚀刻时,因在沟槽底面上形成凹凸或沟槽内部的宽度比沟槽的开口部的宽度宽而无法充分发挥电场缓和效果,存在例如导通电阻上升等问题。

5.专利文献1:日本专利公开2019-036593号公报

6.专利文献2:日本专利公开2019-079984号公报

7.专利文献3:日本专利公开2019-153645号公报

8.专利文献4:wo2016/013554

9.专利文献5:wo2019/013136

技术实现要素:

10.本发明的目的是提供一种具备沟槽的半导体装置,该沟槽具有优异的半导体特性。

11.本发明人等为了实现上述目的进行了深入研究,其结果发现:通过使用特定的高压干蚀刻对结晶性氧化物半导体层形成沟槽,从而成功创制了如下的半导体装置:包括:结晶性氧化物半导体层;和与所述结晶性氧化物半导体层电连接的至少一个电极,在所述结晶性氧化物半导体层的第一面具有至少一个沟槽,所述沟槽包括底面、侧面及所述底面与所述侧面之间的至少一个圆弧部,所述圆弧部的曲率半径在100nm~500nm的范围内,所述侧面和所述结晶性氧化物半导体层的第一面所成的角度为90

°

以上,并且该半导体装置能够一并解决上述的现有问题。

12.另外,本发明人在得到上述见解之后,进一步进行重复研究而完成了本发明。

13.[1]一种半导体装置,包括:结晶性氧化物半导体层;和与所述结晶性氧化物半导体层电连接的至少一个电极,在所述结晶性氧化物半导体层的第一面具有至少一个沟槽,所述沟槽包括底面、侧面及所述底面与所述侧面之间的至少一个圆弧部,所述圆弧部的曲

率半径在100nm~500nm的范围内,所述侧面和所述结晶性氧化物半导体层的第一面所成的角度为90

°

以上。

[0014]

[2]根据上述[1]所述的半导体装置,其中,所述侧面和所述结晶性氧化物半导体层的第一面所成的角度为150

°

以下。

[0015]

[3]根据上述[1]或[2]所述的半导体装置,其中,所述沟槽的宽度朝向所述沟槽的底面变窄。

[0016]

[4]根据上述[1]~[3]中任一项所述的半导体装置,其中,所述沟槽的侧面有倾斜。

[0017]

[5]根据上述[4]所述的半导体装置,其中,所述侧面和所述结晶性氧化物半导体层的第一面所成的角度在大于90

°

且135

°

以下的范围内。

[0018]

[6]根据上述[1]~[5]中任一项所述的半导体装置,其中,所述结晶性氧化物半导体层至少包含镓。

[0019]

[7]根据上述[1]~[6]中任一项所述的半导体装置,其中,所述结晶性氧化物半导体层具有刚玉结构。

[0020]

[8]根据上述[1]~[7]中任一项所述的半导体装置,其中,所述结晶性氧化物半导体层包括两个以上的所述沟槽。

[0021]

[9]根据上述[1]~[8]中任一项所述的半导体装置,其中,所述沟槽的宽度为2μm以下。

[0022]

[10]根据上述[9]所述的半导体装置,其中,所述结晶性氧化物半导体层包括四个以上的所述沟槽。

[0023]

[11]根据上述[1]~[10]中任一项所述的半导体装置,其中,所述半导体装置为功率器件。

[0024]

[12]根据上述[1]~[11]中任一项所述的半导体装置,其中,所述半导体装置为纵型器件。

[0025]

[13]根据上述[1]~[12]中任一项所述的半导体装置,其中,所述半导体装置为二极管。

[0026]

[14]根据上述[1]~[12]中任一项所述的半导体装置,其中,所述半导体装置为晶体管。

[0027]

[15]根据上述[1]~[12]中任一项所述的半导体装置,其中,所述半导体装置为结势垒肖特基二极管。

[0028]

[16]一种半导体系统,具备半导体装置,所述半导体装置为上述[1]~[15]中任一项所述的半导体装置。

[0029]

本发明的半导体装置在所述沟槽的底面与侧面之间具有至少一个圆弧部,所述圆弧部的曲率半径在100nm~500nm的范围内,从而半导体特性优异。

附图说明

[0030]

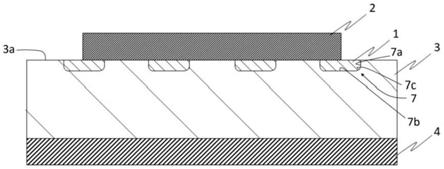

图1是作为本发明的半导体装置的实施方式的一例而示意性地表示结势垒肖特基二极管(jbs)的一方式的图。

[0031]

图2是用于说明本发明的实施方式中的圆弧部的曲率半径的图。

[0032]

图3是示意性地表示电源系统的一例的图。

[0033]

图4是示意性地表示系统装置的一例的图。

[0034]

图5是示意性地表示电源装置的电源电路图的一例的图。

[0035]

图6是在本发明的实施例中使用的成膜装置(雾化cvd(化学气相沉积)装置)的大致结构图。

[0036]

图7是表示实施例1的沟槽的剖面照片。

[0037]

图8是表示实施例2的沟槽的剖面照片。

[0038]

图9是作为本发明的半导体装置的实施方式的一例而示意性地表示肖特基势垒二极管(sbd)的一方式的图。

[0039]

图10是作为本发明的半导体装置的实施方式的一例而示意性地表示沟槽mos型肖特基势垒二极管(sbd)的一方式的图。

[0040]

图11是作为本发明的半导体装置的实施方式的一例而示意性地表示结势垒肖特基二极管(jbs)的一方式的图。

[0041]

图12是作为本发明的半导体装置的实施方式的一例而示意性地表示mosfet的一方式的图。

[0042]

图13是作为本发明的半导体装置的实施方式的一例而示意性地表示mosfet的一方式的图。

[0043]

图14是用于说明本发明的实施方式中的沟槽的侧面和结晶性氧化物半导体层的第一面所成的角度的图。

[0044]

图15是用于说明本发明的实施方式中的沟槽的侧面有倾斜的情况的倾斜角的图。

[0045]

图16-a是表示实施例3的沟槽的剖面照片的图。

[0046]

图16-b是表示实施例3的沟槽的结构的说明图。

具体实施方式

[0047]

本发明的实施方式中的半导体装置的特征在于,包括:结晶性氧化物半导体层;和与所述结晶性氧化物半导体层电连接的至少一个电极,在所述结晶性氧化物半导体层的第一面具有至少一个沟槽,所述沟槽包括底面、侧面及所述底面与所述侧面之间的至少一个圆弧部,所述圆弧部的曲率半径在100nm~500nm的范围内,所述侧面和所述结晶性氧化物半导体层的第一面所成的角度为90

°

以上。

[0048]“曲率半径”是指在所述沟槽剖面中相对于所述圆弧部的曲线的接触圆的半径。“圆弧部”不仅是正圆的一部分,还包含椭圆的一部分,整体可以呈圆弧状,例如也可以是如多边形的角部分变圆这样的形状的一部分。即,所述圆弧部在所述沟槽剖面中可以是具有曲线形状的部分,只要设置于所述侧面与所述底面之间的至少一部分即可。例如,将圆弧部的例子示于图2。图2所记载的结晶性氧化物半导体具备具有两个曲率半径的圆弧部7c。在图2中,r1及r2的曲率半径均在100nm~500nm的范围内。在本发明的实施方式中,通过设为这种曲率半径的范围,从而能够实现优异的电场缓和效果,其结果还能够降低导通电阻。另外,在本发明的实施方式中,所述沟槽也可以在所述沟槽的底面7b与侧面7a之间的整个部分具有圆弧部。另外,在本发明的实施方式中,优选位于所述沟槽7的底面7b与第一侧面7aa之间的第一圆弧部7ca的曲率半径r1、和位于所述沟槽的底面7b与第二侧面7ab之间的第二

圆弧部7cb的曲率半径r2之差在0~200nm的范围内,更优选在0~50nm的范围内。在本发明的实施方式中,最优选第一圆弧部7ca的曲率半径r1与第二圆弧部7cb的曲率半径r2相等。

[0049]“所述侧面和所述结晶性氧化物半导体层的第一面所成的角度”是指在所述沟槽7的剖面中,设置于所述结晶性氧化物半导体层3的第一面3a侧的所述沟槽的侧面7a和所述结晶性氧化物半导体层的第一面3a所成的角度,在本发明的实施方式中,通常为约90

°

以上。作为这种“所述侧面和所述结晶性氧化物半导体层的第一面所成的角度”例如列举了由图14及图16-b的θ(θ1、θ2)表示的角度。在本发明中,通过具有这种所述沟槽7的第一侧面7aa和所述结晶性氧化物半导体层3的第一面3a所成的角度θ1、及所述沟槽7的第二侧面7ab和所述结晶性氧化物半导体层3的第一面3a所成的角度θ2,能够实现优异的电场缓和效果,其结果还能够降低导通电阻。另外,所述“所述侧面和所述结晶性氧化物半导体层的第一面所成的角度”的上限只要不阻碍本发明的目的等则没有限定,优选为150

°

。另外,在本发明的实施方式中,优选在所述沟槽的剖面中,所述沟槽7的第一侧面7aa和所述结晶性氧化物半导体层的第一面3a所成的角度(θ1)与所述沟槽的第二侧面7ab和所述结晶性氧化物半导体层的第一面3a所成的角度(θ2)相等。

[0050]

所述沟槽被形成在所述结晶性氧化物半导体层上,只要不阻碍本发明的目的则不受特别限定。所述沟槽的深度等也不受特别限定,但在本发明中,所述沟槽剖面中的所述沟槽的深度通常为200nm以上,优选为500nm以上,更优选为1μm以上。此外,所述沟槽的深度的上限不受特别限定,优选为100μm,更优选为10μm。另外,所述沟槽剖面中的所述沟槽的宽度也不受特别限定,通常为200nm以上,优选为500nm以上。此外,所述沟槽的宽度的上限不受特别限定,优选为100μm,更优选为10μm。根据这种优选范围的沟槽,作为功率器件等半导体装置而能够发挥更优异的半导体特性。另外,在所述沟槽剖面中,作为本发明的一个实施方式,所述沟槽的宽度朝向底面变窄的沟槽剖面被列举为合适的例子,根据这种合适的例子,能够形成良好的界面,并且能够得到更良好的电气特性,因此优选。另外,优选所述沟槽的侧面有倾斜,所述侧面相对于所述结晶性氧化物半导体层的第一面具有倾斜角。此外,所述倾斜角是指,在所述沟槽剖面中设定所述结晶性氧化物半导体层的第一面和与所述第一面垂直的假想面(因不具有倾斜而倾斜角为0

°

)的情况下,所述假想面和所述沟槽的侧面(具有倾斜)所成的角度。作为所述倾斜角,例如可列举由图15的θ(θ3、θ4)表示的角度。在本发明中,优选所述倾斜角在大于0

°

且为45

°

以下的范围内。即,优选所述侧面和所述结晶性氧化物半导体层的第一面所成的角度(例如,由图14及图16-b所示的θ1、θ2)在大于90

°

且135

°

以下的范围内。由于具有这种优选的倾斜角,因此能够形成更良好的沟道,其结果能够进一步降低导通电阻。

[0051]

另外,所述电极可以是公知的电极,例如也可以是肖特基电极、欧姆电极、栅电极、漏电极及源电极等中的任一种电极。所述电极可以是根据所述半导体装置的种类等适当设定的公知的电极,作为所述电极材料,例如可列举d块金属等。另外,所述电极例如也可以是称为势垒电极的电极。所述势垒电极只要对所述半导体领域的界面形成具有规定的势垒高度的肖特基势垒则不受特别限定。所述势垒电极的电极材料只要是能够用作势垒电极的材料则不受特别限定,也可以是导电性无机材料,还可以是导电性有机材料。在本发明中,优选所述电极材料为金属。作为所述金属,不受特别限定,但适宜可列举例如选自元素周期律表第4族~第11族中的至少一种金属等。作为元素周期律表第4族的金属,例如可列举钛

(ti)、锆(zr)、铪(hf)等,其中优选ti。作为元素周期律表第5族的金属,例如可列举钒(v)、铌(nb)、钽(ta)等。作为元素周期律表第6族的金属,例如可列举选自铬(cr)、钼(mo)及钨(w)等中的一种或两种以上的金属等,但在本发明中,cr为开关特性等的半导体特性更良好的金属,因此优选。作为元素周期律表第7族的金属,例如可列举锰(mn)、锝(tc)、铼(re)等。作为元素周期律表第8族的金属,例如可列举铁(fe)、钌(ru)、锇(os)等。作为元素周期律表第9族的金属,例如可列举钴(co)、铑(rh)、铱(ir)等。作为元素周期律表第10族的金属,例如可列举镍(ni)、钯(pd)、铂(pt)等,其中优选pt。作为元素周期律表第11族的金属,例如可列举铜(cu)、银(ag)、金(au)等。作为所述势垒电极的形成方法,例如可列举公知的方法,更具体而言,可列举干法或湿法等。作为干法,例如可列举溅射、真空蒸镀、cvd等的公知的方法。作为湿法,例如可列举丝网印刷或模涂等。

[0052]

关于所述结晶性氧化物半导体层,只要在所述半导体装置中形成半导体区域则不受特别限定。所述结晶性氧化物半导体层(以下,简称为“半导体区域”)只要以半导体为主成分,则不受特别限定,在本发明中,优选所述半导体区域包含结晶性氧化物半导体作为主成分,更优选为包含n型半导体作为主成分的n型半导体区域。所述结晶性氧化物半导体优选具有β-gallia结构或刚玉结构,更优选具有刚玉结构。另外,所述半导体区域优选至少包含镓,更优选作为主成分包含镓化合物,进一步优选以inalgao类半导体为主成分,最优选包含作为主成分的α-ga2o3或其混晶。此外,在例如结晶性氧化物半导体为α-ga2o3的情况下,“主成分”是指,以所述半导体区域中的金属元素中的镓的原子比为0.5以上的比率包含α-ga2o3即可。在本发明中,优选所述半导体区域中的金属元素中的镓的原子比为0.7以上,更优选为0.8以上。另外,所述半导体区域通常为单相区域,只要不阻碍本发明的目的,也可以进一步具有由不同的半导体相构成的第二半导体区域或其他相等。另外,所述半导体区域通常呈膜状,可以是半导体膜。所述半导体区域的半导体膜的厚度不受特别限定,也可以是1μm以下,还可以是1μm以上,但在本发明中,优选为1μm~40μm,更优选为1μm~25μm。结晶性氧化物半导体层例如通过设为厚膜或降低载流子浓度而提高耐压。另一方面,具有因加大厚度或降低载流子浓度而导通电阻也变高这一类的折衷选择问题。根据本发明的实施方式,由于包含α-ga2o3或β-ga2o3的氧化镓类的结晶性氧化物半导体层具有沟槽,该沟槽包含曲率半径在100nm~500nm的范围内的圆弧部,并且所述沟槽的侧面和所述结晶性氧化物半导体层的第一面所成的角度在大于90

°

且135

°

以下的范围内,因此能够充分得到电场缓和效果。根据本发明的实施方式,由于如上述那样能够充分得到电场缓和效果,因此能够减小所述氧化镓类的结晶性氧化物半导体层(包含漂移区域)的厚度(例如,10μm以下),即使在这种厚度的情况下,也能够实现高耐压(例如,3000v以上)的半导体装置。另外,根据本发明的实施方式,能够进一步减小所述氧化镓类的结晶性氧化物半导体层(包含漂移区域)的厚度(例如,2.0μm以下),即使在这种厚度的情况下,也能够实现高耐压(例如,600v以上)的半导体装置。另外,在本发明的实施方式中,能够将所述氧化镓类的结晶性氧化物半导体层(包含漂移区域)的载流子浓度设为5.0

×

10

16

/cm3以上,优选能够设为3.0

×

10

17

/cm3以上。虽然根据需要的耐压适当调整所述结晶性氧化物层的厚度或所述载流子浓度,但在本发明的实施方式中,如上述那样在比以往薄的厚度或比以往高的载流子浓度下也能够实现高耐压化,因此其结果能够降低导通电阻。另外,所述半导体膜的表面积不受特别限定,也可以是1mm2以上,还可以是1mm2以下。此外,所述结晶性氧化物半导体通常为单结晶,但也可以是

多结晶。另外,所述半导体膜也可以是单层膜,还可以是多层膜。在所述半导体膜为多层膜的情况下,优选所述多层膜的膜厚为40μm以下,另外,在所述半导体膜为至少包括第一半导体层和第二半导体层的多层膜,并且在第一半导体层上设置有肖特基电极的情况下,优选为第一半导体层的载流子浓度小于第二半导体层的载流子浓度的多层膜。此外,在该情况下,第二半导体层通常包含掺杂物,通过调节掺杂量,能够适当设定所述半导体层(包括所述第一半导体层和第二半导体层)的载流子浓度。

[0053]

所述半导体膜优选包含掺杂物。所述掺杂物不受特别限定,可以是公知的掺杂物。作为所述掺杂物,例如可列举锡、锗、硅、钛、锆、钒或铌等的n型掺杂物或p型掺杂物等。在本发明中,优选所述掺杂物为sn、ge或si。掺杂物的含量在所述半导体膜的组成中优选为0.00001原子%以上,进一步优选为0.00001原子%~20原子%,最优选为0.00001原子%~10原子%。此外,在本发明中,第一半导体层中使用的掺杂物为锗、硅、钛、锆、钒或铌,第二半导体层中使用的掺杂物为锡,由于半导体特性进一步格外良好而不损害密合性,因此优选。

[0054]

例如,使用雾化cvd法等方法形成所述半导体膜,更具体而言,例如对原料溶液进行雾化使之产生雾化液滴(雾化工序),利用载气将得到的雾化液滴(包含雾)运送至基体上(运送工序),接着通过在成膜室内使所述雾化液滴进行热反应,在基体上层叠包含结晶性氧化物半导体作为主成分的半导体膜(成膜工序),从而适当形成半导体膜。

[0055]

(雾化工序)

[0056]

关于雾化工序,通过对所述原料溶液进行雾化、并使雾化后的液滴悬浮而产生雾化液滴。所述原料溶液的雾化方法只要能够对所述原料溶液进行雾化,则不受特别限定,可以是公知的方法,但在本发明中,优选使用超声波的雾化方法。使用超声波得到的雾化液滴的初始速度为零,雾化液滴在空中悬浮,因此优选,由于并非像例如喷射那样吹出雾化液滴,而是雾化液滴向空间悬浮并能够作为气体运送,因此不存在因碰撞能量导致的损伤,因此合适。液滴尺寸不受特别限定,也可以是几毫米左右的液滴,优选为50μm以下,更优选为100nm~10μm。

[0057]

(原料溶液)

[0058]

所述原料溶液能够实现雾化,只要包含能够形成半导体区域的原料则不受特别限定,可以是无机材料,也可以是有机材料,但在本发明中,优选所述原料为金属或金属化合物,更优选包含选自镓、铁、铟、铝、钒、钛、铬、铑、镍、钴、锌、镁、钙、硅、钇、锶及钡中的一种或两种以上的金属。

[0059]

在本发明中,作为所述原料溶液,可适当使用通过将所述金属以络合物或盐的形态在有机溶剂或水中溶解或分散而成的溶液。作为络合物的形态,例如可列举乙酰丙酮络合物、羰基络合物、胺络合物、氢化物络合物等。作为盐的形态,例如可列举有机金属盐(例如,乙酸金属盐、草酸金属盐、柠檬酸金属盐等)、金属硫化物盐、硝化金属盐、金属磷酸盐、金属卤化物盐(例如,金属氯化物盐、金属溴化物盐、金属碘化物盐等)。

[0060]

另外,优选在所述原料溶液中混合氢卤酸盐和氧化剂等添加剂。作为所述氢卤酸盐,例如可列举氢溴酸、盐酸、氢碘酸等,但从得到更优质的膜的理由来看,优选氢溴酸或氢碘酸。作为所述氧化剂,例如可列举过氧化氢(h2o2)、过氧化钠(na2o2)、过氧化钡(bao2)或过氧化苯甲酰(c6h5co)2o2等过氧化物、次氯酸盐(hclo)、高氯酸、硝酸、臭氧水、过氧乙酸和硝

基苯等有机过氧化物等。

[0061]

所述原料溶液也可以包含掺杂物。由于原料溶液包含掺杂物,能够良好的进行掺杂。所述掺杂物只要不阻碍本发明的目的,则不受特别限定。作为所述掺杂物,例如可列举锡、锗、硅、钛、锆、钒或铌等n型掺杂物或p型掺杂物等。掺杂物的浓度通常也可以是约1

×

10

16

/cm3~1

×

10

22

/cm3,并且还可以将掺杂物的浓度例如设为约1

×

10

17

/cm3以下的低浓度。此外,进一步根据本发明的实施方式,也可以以约1

×

10

20

/cm3以上的高浓度包含掺杂物。在本发明的实施方式中,优选以1

×

10

17

/cm3以上的载流子浓度含有掺杂物。另外,作为本发明的一个实施方式,能够在具有600v的耐压的半导体装置中,将氧化镓类的结晶性氧化物半导体层的载流子浓度设为1

×

10

17

/cm3以上且3

×

10

17

/cm3以下。

[0062]

原料溶液的容剂不受特别限定,也可以是水等的无机溶剂,也可以是乙醇等的有机溶剂,还可以是无机溶剂和有机溶剂的混合溶剂。在本发明中,优选所述溶剂包含水,更优选为水或水和乙醇的混合溶剂。

[0063]

(运送工序)

[0064]

在运送工序中,利用载气向成膜室内运送所述雾化液滴。所述载气只要不阻碍本发明的目的则不受特别限定,例如作为合适的例子,可列举氧、臭氧、氮或氩等惰性气体、或者氢气和合成气体等还原气体。另外,载气的种类可以是一种,也可以是两种以上,还可以将降低流量的稀释气体(例如,10倍稀释气体等)等进一步用作第二载气。另外,载气的供给部位也可以不只是一个部位,还可以是两个部位以上。载气的流量不受特别限定,优选为0.01~20l/分钟,更优选为1~10l/分钟。在稀释气体的情况下,优选稀释气体的流量为0.001~2l/分钟,更优选为0.1~1l/分钟。

[0065]

(成膜工序)

[0066]

在成膜工序中,通过使所述雾化液滴在成膜室内进行热反应,从而在基体上形成所述半导体膜。关于热反应,只要利用热使所述雾化液滴进行反应即可,只要不阻碍本发明的目的则反应条件等也不受特别限定。在该工序中,通常在溶剂的蒸发温度以上的温度进行所述热反应,但优选为不过高的温度(例如,1000℃)以下,更优选650℃以下,最优选300℃~650℃。另外,只要不阻碍本发明的目的,也可以在真空下、无氧气氛下、还原气体气氛下及氧气氛下中的任一气氛下进行热反应,但优选在无氧气氛下或氧气氛下进行热反应。另外,也可以在大气压下、加压下及减压下中的任一条件下进行热反应,但在本发明中,优选在大气压下进行热反应。此外,能够通过调整成膜时间来设定膜厚。

[0067]

(基体)

[0068]

所述基体只要能够支撑所述半导体膜则不受特别限定。所述基体的材料只要不阻碍本发明的目的则也不受特别限定,可以是公知的基体,也可以是有机化合物,还可以是无机化合物。作为所述基体的形状,也可以是任何形状,对所有形状有效,例如可列举平板或圆板等板状、纤维状、棒状、圆柱状、方柱状、筒状、螺旋状、球状、环状等,但在本发明的实施方式中优选基板。基板的厚度在本发明中不受特别限定。

[0069]

所述基板呈板状,只要成为所述半导体膜的支撑体则不受特别限定。所述基板也可以是绝缘体基板,也可以是半导体基板,还可以是金属基板或导电性基板,但优选所述基板为绝缘体基板,并且优选在表面具有金属膜的基板。作为所述基板,例如可列举将具有刚玉结构的基板材料作为主成分来包含的基底基板、或者将具有β-gallia结构的基板材料作

为主成分来包含的基底基板、将具有六方晶结构的基板材料作为主成分来包含的基底基板等。在此,“主成分”是指相对于基板材料的所有成分,以原子比计优选包含50%以上、更优选70%以上、进一步优选90%以上的具有上述特定的结晶结构的基板材料,也可以为100%。

[0070]

基板材料只要不阻碍本发明的目的则不受特别限定,可以是公知的基板材料。作为具有所述刚玉结构的基板材料,例如可适当列举α-al2o3(蓝宝石基板)或α-ga2o3,作为更合适的例子,可列举a面蓝宝石基板、m面蓝宝石基板、r面蓝宝石基板、c面蓝宝石基板或α型氧化镓基板(a面、m面或r面)等。作为以具有β-镓结构的基板材料为主成分的基底基板,例如可列举β-ga2o3基板、或包含ga2o3和al2o3且al2o3为大于0重量%且60重量%以下的混晶体基板等。另外,作为以具有六方晶结构的基板材料为主成分的基底基板,例如可列举sic基板、zno基板、gan基板等。

[0071]

在本发明中,也可以在所述成膜工序之后进行退火处理。退火处理温度只要不阻碍本发明的目的则不受特别限定,通常为300℃~650℃,优选为350℃~550℃。另外,退火处理时间通常为1分钟~48小时,优选为10分钟~24小时,更优选为30分钟~12小时。此外,只要不阻碍本发明的目的,则也可以在任何气氛下进行退火处理,优选为无氧气氛下,更优选为氮气氛下。

[0072]

另外,在本发明的实施方式中,也可以在所述基体上直接设置所述半导体膜,还可以经由缓冲层(buffer layer)或应力松弛层等其他层设置所述半导体膜。各层的形成方法不受特别限定,可以是公知的方法,但在本发明的实施方式中,优选雾化cvd法。

[0073]

此外,作为本发明的一个实施方式,优选所述结晶性氧化物半导体层至少包含镓。另外,作为本发明的一个适当的实施方式,优选所述结晶性氧化物半导体层具有刚玉结构。在本发明的实施方式中,也可以在使用从所述基体等剥离所述半导体膜等公知的方法之后,将所述半导体膜作为所述半导体区域而用于半导体装置,还可以直接作为所述半导体区域使用于半导体装置。此外,作为本发明的一个适当的实施方式,优选所述结晶性氧化物半导体层包括两个以上的所述沟槽。另外,作为本发明的一个适当的实施方式,优选所述沟槽的宽度为2μm以下,优选所述结晶性氧化物半导体层包括四个以上的所述沟槽。多个所述沟槽彼此隔开间隔而配置在所述结晶性氧化物半导体的第一面侧。根据这种实施方式,成为更适合作为功率器件的半导体装置,能够得到更优异的半导体特性。另外,即使面向半导体装置的小型化也变得更有效。此外,所述结晶性氧化物半导体层在所述沟槽的底面与侧面之间具有至少一个圆弧部,所述圆弧部的曲率半径在100nm~500nm的范围内,但在所述结晶性氧化物半导体层具有两个以上的圆弧部的情况下,只要至少一个圆弧部的曲率半径在100nm~500nm的范围内即可。在本发明中,在所述结晶性氧化物半导体层具有两个以上的圆弧部的情况下,优选两个以上的圆弧部的曲率半径在100nm~500nm的范围内,更优选所有圆弧部的曲率半径在100nm~500nm的范围内。

[0074]

例如,能够通过高压干蚀刻法等来形成所述沟槽。更具体而言,例如至少包括使用经等离子体化的蚀刻气体对结晶性氧化物进行蚀刻的方法,可列举所述蚀刻气体的压力在1pa以上且10pa以下的范围内的蚀刻方法等。在所述蚀刻方法中,优选所述蚀刻气体的压力为2pa以上。另外,优选经等离子体化的所述蚀刻气体至少包含卤素。另外,还优选经等离子体化的所述蚀刻气体至少包含镓。另外,还优选在惰性气体的气氛下进行所述蚀刻。另外,

优选所述惰性气体为氩。另外,还优选在卤素气体的气氛下进行所述蚀刻。还优选所述蚀刻气体的等离子体的偏压为25w以上。由于使用这种优选的高压蚀刻方法,因此能够容易形成所述沟槽。

[0075]

下面,使用附图对本发明的实施方式进行更详细说明,但本发明并不限定于这些实施方式。

[0076]

在本发明的实施方式中,在结晶性氧化物半导体层3(还称为半导体区域)的第一面3a侧具有至少一个沟槽7。所述沟槽7包括底面、侧面及所述底面与所述侧面之间的至少一个圆弧部。另外,结晶性氧化物半导体层3与电极电连接。本发明的实施方式可应用于包括沟槽的半导体装置。例如,图1表示作为本发明的一个实施方式的结势垒肖特基二极管(jbs)。图1的半导体装置包括:半导体区域3;势垒电极2,设置在所述半导体区域上且能够在该势垒电极2与所述半导体区域之间形成肖特基势垒;和势垒高度调整区域1,设置在势垒电极2与半导体区域3之间,且能够在该势垒高度调整区域与所述半导体区域3之间形成势垒高度大于势垒电极2的肖特基势垒的势垒高度的肖特基势垒。此外,势垒高度调整区域1被埋入到沟槽7中,该沟槽7设置于半导体区域3的第一面3a侧。在本发明的实施方式中,优选多个沟槽7及配置在多个沟槽7内的多个势垒高度调整区域1按规定间隔设置,更优选在所述势垒电极的两端与所述半导体区域之间分别设置有所述势垒高度调整区域。此外,图1为jbs的剖面图,所述多个势垒高度调整区域在例如平面图中被连接。根据这种优选的方式,以热稳定性及密合性更优异、进一步减轻漏电流、并且耐压等半导体特性更优异的方式构成jbs。此外,图1的半导体装置在半导体区域3的第二面3b侧具备欧姆电极4。图1的半导体装置在所述沟槽7的底面7a与侧面7b之间具有圆弧部7c,所述圆弧部的曲率半径在100nm~500nm的范围内,电场缓和效果优异,其结果能够降低导通电阻。

[0077]

图1的半导体装置的各层的形成方法只要不阻碍本发明的目的则不受特别限定,可以是公知的方法。例如,可列举如下的方法:即,在通过真空蒸镀法、cvd法、溅射法或各种涂覆技术等进行成膜之后,通过光刻法并使用图案化方法或印刷技术等直接进行图案化。

[0078]

图9表示本发明的实施方式的肖特基势垒二极管(sbd)的一例。图9的sbd具备n-型半导体层101a、n+型半导体层101b、电介体层104、肖特基电极105a及欧姆电极105b。另外,图9的sbd具有具备所述圆弧部的沟槽7,在这种沟槽7内埋入有p型半导体层102。

[0079]

肖特基电极及欧姆电极的材料也可以是公知的电极材料,作为所述电极材料,例如可列举al、mo、co、zr、sn、nb、fe、cr、ta、ti、au、pt、v、mn、ni、cu、hf、w、ir、zn、in、pd、nd或ag等金属或者它们的合金、氧化锡、氧化锌、氧化铟、氧化锡铟(ito)、氧化铟锌(izo)等金属氧化物导电膜、聚苯胺、聚噻吩或聚吡咯等有机导电性化合物或它们的混合物等。

[0080]

例如,能够通过真空蒸镀法或溅射法等公知方法来形成肖特基电极及欧姆电极。更具体而言,例如在形成肖特基电极的情况下,通过层叠由mo构成的层和由al构成的层,并且对由mo构成的层及由al构成的层实施利用光刻法的图案化来形成肖特基电极。

[0081]

在对图9的sbd施加反向偏压的情况下,由于空乏层(未图示)通过沟槽7的所述圆弧部的应力松弛作用而向作为结晶性氧化物半导体层的n-型半导体层101a中良好地扩展,因此成为高耐压的sbd。另外,在施加正向偏压的情况下,电子从位于结晶性氧化物半导体层的与第一面侧相反的第二面侧的欧姆电极105b向位于结晶性氧化物半导体层的第一面侧的肖特基电极105a流动。如此使用所述半导体结构的sbd在用于高耐压/强电流时优异,

转换速度也快,并且耐压性及可靠性也优异。

[0082]

作为电介体层104的材料,例如可列举gao、algao、inalgao、alinzngao4、aln、hf2o3、sin、sion、al2o3、mgo、gdo、sio2或si3n4等。通过将这种绝缘体使用于绝缘体层,能够良好地发现界面中的半导体特性的功能。电介体层104设置在n-型半导体层101a与肖特基电极105a之间。例如,能够通过溅射法、真空蒸镀法或cvd法等的公知方法来形成绝缘体层。

[0083]

图10表示沟槽型肖特基势垒二极管(sbd)的一例,其具备:n-型半导体层101a,作为结晶性氧化物半导体层且具有配置在所述n-型半导体层101a的第一面侧的两个以上的沟槽7;n+型半导体层101b;电介体层104;肖特基电极105a及欧姆电极105b。图10的沟槽型sbd具有具备所述圆弧部的沟槽结构。根据这种沟槽型sbd,在维持更高的耐压性的状态下,能够大幅降低漏电流,其结果还能够实现大幅的低导通电阻化。

[0084]

图11表示具备n-型半导体层101a、n+型半导体层101b、p型半导体层102、电介体层104、肖特基电极105a及欧姆电极105b的结势垒肖特基二极管(jbs)的一例。图11的jbs具有具备所述圆弧部的沟槽7,在这种沟槽7内埋入有p型半导体层102。根据这种jbs,在维持比图10的沟槽型sbd更高的耐压性的状态下,能够大幅降低漏电流,其结果还能够实现更大幅的低导通电阻化。

[0085]

将本发明的半导体装置为mosfet的情况的一例示于图12。图12的mosfet为沟槽型mosfet,并具备:n-型半导体层131a,作为结晶性氧化物半导体层且包括沟槽7;n+型半导体层131b及131c;栅极绝缘膜134;栅电极135a;源电极135b以及漏电极135c。

[0086]

在漏电极135c上形成有例如厚度为100nm~100μm的n+型半导体层131b,在所述n+型半导体层131b上形成有例如厚度为100nm~100μm的n-型半导体层131a。并且,进一步在所述n-型半导体层131a上形成有n+型半导体层131c,在所述n+型半导体层131c上形成有漏电极135b。

[0087]

另外,在所述n-型半导体层131a及所述n+型半导体层131c内贯通有所述n+型半导体层131c,作为到达所述n-型半导体层131a的中途的深度的多个沟槽7形成有槽。这种沟槽7在沟槽7的底面与侧面之间均具备所述圆弧部。在所述沟槽7内,例如经由厚度为10nm~1μm的栅极绝缘膜134埋入形成栅电极135a。

[0088]

在图12的mosfet的开启状态下,如果对所述源电极135b与所述漏电极135c之间施加电压,并且对所述栅电极135a施加相对于所述源电极135b为正的电压,则在所述n-型半导体层131a的侧面上形成沟道层,电子被注入到所述n-型半导体层,进行开启。由于将所述栅电极的电压设为0v,因此不可能形成沟道层,关闭状态成为n-型半导体层被空乏层填满的状态,处于关闭。

[0089]

在图12的mosfet的制造时,可适当使用公知方法。例如,在n-型半导体层131a及n+型半导体层131c的规定区域上设置蚀刻掩膜,通过上述优选的高压干蚀刻法进行蚀刻,与所述圆弧部一同形成深度从所述n+型半导体层131c的表面到达所述n-型半导体层131a的中途的沟槽7的槽。接着,在使用热氧化法、真空蒸镀法、溅射法、cvd法等的公知方法,对所述沟槽7的槽的侧面及底面形成例如50nm~1μm厚的栅极绝缘膜134之后,使用cvd法、真空蒸镀法、溅射法等,在所述沟槽7的槽中,将例如多晶硅等的栅电极材料形成为n-型半导体层的厚度以下。并且,通过使用真空蒸镀法、溅射法、cvd法等公知方法,在n+型半导体层131c上形成源电极135b,在n+型半导体层131b上形成漏电极135c,从而能够制造功率

mosfet。此外,源电极及漏电极的电极材料也可以是分别公知的电极材料,作为所述电极材料,例如可列举al、mo、co、zr、sn、nb、fe、cr、ta、ti、au、pt、v、mn、ni、cu、hf、w、ir、zn、in、pd、nd或ag等金属或它们的合金、氧化锡、氧化锌、氧化铟、氧化铟锡(ito),氧化锌铟(izo)等金属氧化物导电膜、聚苯胺、聚噻吩或聚吡咯等有机导电性化合物、或者它们的混合物等。

[0090]

如此得到的mosfet与现有的沟槽型mosfet相比耐压性进一步优异。此外,图12表示沟槽型的纵型mosfet的例子,但本发明并不限定于此,可应用于各种沟槽型mosfet的形态。例如,也可以通过将图12的沟槽7的深度深挖至到达n-型半导体层131a的底面的深度,从而降低串联电阻。另外,将其他沟槽型mosfet的一例示于图13。

[0091]

图13表示具备n-型半导体层131a、第一n+型半导体层131b、第二n+型半导体层131c、p型半导体层132、p+型半导体层132a、栅极绝缘膜134、栅电极135a、源电极135b及漏电极135c的金属氧化膜半导体电场效果晶体管(mosfet)的一例。此外,p+型半导体层132a也可以是p型半导体层,还可以与p型半导体层132相同。

[0092]

所述半导体装置尤其对功率器件有用。另外,作为本发明的一个实施方式,所述半导体装置优选为纵型器件。作为所述半导体装置,例如可列举二极管或晶体管(例如,mesfet等)等,但其中优选二极管,更优选结势垒肖特基二极管(jbs)。

[0093]

关于本发明的半导体装置,在上述事项的基础上,进一步使用公知方法,适合用作功率模块、变频器或转换器,进而能够适当用于例如使用电源装置的半导体系统等。所述电源装置通过使用公知方法与布线图案等连接等,从而能够由所述半导体装置制作或制作为所述半导体装置。图3使用多个所述电源装置171、172和控制电路173来构成电源系统170。如图4所示,所述电源系统能够组合电子电路181和电源系统182并用于系统装置180。此外,将电源装置的电源电路图的一例示于图5。图5表示由功率电路和控制电路构成的电源装置的电源电路,在通过变频器192(由mosfeta~d构成)且利用高频波转换dc电压并变换为ac之后,利用变压器193实施绝缘及变压,并且在利用整流mosfet194(a~b')进行整流之后,通过dcl195(平滑用线圈l1、l2)实现平滑,输出直流电压。此时,利用电压比较器197将输出电压与基准电压进行比较,并且以成为期望的输出电压的方式利用pwm控制电路196来控制变频器192及整流mosfet194。

[0094]

[实施例]

[0095]

(实施例1)

[0096]

1.半导体层的形成

[0097]

1-1.成膜装置

[0098]

使用图6,对在实施例中使用的雾化cvd装置19进行说明。图6的成膜装置19具备:用于供给载气的载气源22a;用于调节从载气源22a送出的载气的流量的流量调节阀23a;用于供给载气(稀释)的载气(稀释)源22b;用于调节从载气(稀释)源22b送出的载气(稀释)的流量的流量调节阀23b;用于收纳原料溶液24a的雾化发生源24;用于装入水25a的容器25;安装在容器25的底面上的超声波振子26;成膜室30;用于连接从雾化发生源24至成膜室30之间的石英制的供给管27;和设置在成膜室内的热板(加热器)28。在热板28上设置有基板20。

[0099]

1-2.原料溶液的制作

[0100]

使0.1m的溴化镓水溶液以体积比含有10%的氢溴酸,并且将其设为原料溶液。

[0101]

1-3.成膜准备

[0102]

将在上述1-2.中得到的原料溶液24a收纳到雾化发生源24内。接着,作为基板20,将蓝宝石基板设置在热板28上,通过使热板28工作而将成膜室30内的温度升温至630℃。接着,在打开流量调节阀23a、23b,将载气从作为载气源的载气供给机构22a、22b供给到成膜室30内,并且利用载气充分置换成膜室30的气氛之后,分别将载气的流量调节为1l/分钟,将载气(稀释)的流量调节为2l/分钟。此外,作为载气使用氮。

[0103]

1-4.半导体膜的形成

[0104]

接着,通过使超声波振子26以2.4mhz振动,并且将该振动经由水25a传播至原料溶液24a,从而使原料溶液24a雾化以生成雾。该雾通过载气导入到成膜室30内,在大气压、630℃下,使雾在成膜室30内进行反应,从而在基板20上形成半导体膜。此外,膜厚为4.1μm,成膜时间为105分钟。

[0105]

1-5.评价

[0106]

使用xrd衍射装置,进行在上述1-4.中得到的膜的相的分析,其结果得到的膜为α-ga2o3。

[0107]

2、蚀刻

[0108]

在下述表1的条件下使用icp-rie装置对半导体膜形成沟槽。实施例的沟槽均具有圆弧部,圆弧部的曲率半径均在100nm以上且500nm以下的范围内。将作为实施例1形成的沟槽的剖面照片示于图7。关于实施例1的曲率半径,如图7那样,r1(左侧)为140nm,r2(右侧)为160nm。另外,沟槽的侧面具有倾斜角,倾斜角为60

°

。如从图7明确看到那样,形成有良好的沟槽。

[0109]

[表1]

[0110][0111]

(实施例2)

[0112]

除通过表1所示的条件进行蚀刻以外,以与实施例1同样的方式形成沟槽。将得到的沟槽的剖面照片示于图8。关于沟槽的圆弧部的曲率半径,如图8所示,r1(左侧)为125nm,r2(右侧)为298nm。如从图8明确看到那样,形成有具有优质的圆弧部的沟槽。

[0113]

[表2]

[0114]

[0115]

(实施例3)

[0116]

除通过表2所示的条件进行蚀刻以外,以与实施例1同样的方式对半导体膜(称为结晶性氧化物半导体层)形成沟槽。将得到的沟槽的剖面照片示于图16-a。另外,图16-b表示使用相同的剖面照片的说明图。沟槽7的第一圆弧部7ca的曲率半径r1(左侧)为220nm,第二圆弧部7cb的曲率半径r2(右侧)也为220nm。虽然在结晶性氧化物半导体层3上形成有多个沟槽7,但任一个沟槽7均形成有第一圆弧部7ca和第二圆弧部7cb的曲率半径相等的沟槽7。所述沟槽7的宽度朝向底面变窄。在沟槽的剖面中,所述沟槽的侧面7a(第一侧面7aa)和所述结晶性氧化物半导体层3的第一面3a所成的角度(图16-b所示的θ1)在大于90

°

且135

°

以下的范围内,所述沟槽的侧面7a(第二侧面7ab)和所述结晶性氧化物半导体层3的第一面3a所成的角度(图16-b所示的θ2)在大于90

°

且135

°

以下的范围内。此外,图16-b所示的sio2为掩膜,是为了进行蚀刻来形成沟槽而设置在结晶性氧化物半导体层3上,因此最终被去除。另外,改变bcl3的流量来得到结晶性氧化物半导体层,其结果可知通过将bcl3的流量设定在50sccm~100sccm的范围内,能够得到具有更良好的圆弧部的沟槽。

[0117]

根据本发明的实施例1~3,在沟槽剖面中,具有包括曲率半径在100nm~500nm的范围内的圆弧部的沟槽,并且所述沟槽的侧面和所述结晶性氧化物半导体层的第一面所成的角度在大于90

°

且135

°

以下的范围内,能够充分得到电场缓和效果。其结果,能够降低具有氧化镓类的结晶性氧化物半导体层的半导体装置的导通电阻。另外,根据实施例3,由于能够对氧化镓类的结晶性氧化物半导体层形成具有圆弧部的沟槽,该圆弧部具有左右对称的曲率半径,因此能够期待进一步降低半导体装置的导通电阻。

[0118]

(比较例1)

[0119]

除通过表1所示的条件进行蚀刻以外,以与实施例1同样的方式形成沟槽。得到的沟槽的底面呈凸状,底面与侧面之间也具有角落部等,形成有非优质的沟槽。

[0120]

(比较例2)

[0121]

除通过表1所示的条件进行蚀刻以外,以与实施例1同样的方式形成沟槽。得到的沟槽的侧面成为以逆倾斜状挖开的状态,导致沟槽内部的宽度比沟槽的开口部的宽度更宽。另外,虽然在底面与侧面之间形成有圆弧部,但导致圆弧部大量膨出,曲率半径也成为1μm以上等,形成有非优质的沟槽。

[0122]

产业上的可利用性

[0123]

本发明的半导体装置能够在半导体(例如,化合物半导体电子器件等)、电子部件及电气机器部件、光学电子照片相关装置及工业部件等的所有领域中使用,尤其对功率器件有用。

[0124]

附图标记说明

[0125]1ꢀꢀꢀꢀ

势垒高度调整区域

[0126]2ꢀꢀꢀꢀ

势垒电极

[0127]3ꢀꢀꢀꢀ

结晶性氧化物半导体层(半导体区域)

[0128]

3a

ꢀꢀꢀ

第一面

[0129]

3b

ꢀꢀꢀ

第二面

[0130]4ꢀꢀꢀꢀ

欧姆电极

[0131]7ꢀꢀꢀꢀ

沟槽

[0132]

7a

ꢀꢀꢀ

沟槽的侧面

[0133]

7aa

ꢀꢀ

沟槽的第一侧面

[0134]

7ab

ꢀꢀ

沟槽的第二侧面

[0135]

7b

ꢀꢀꢀ

沟槽的底面

[0136]

7c

ꢀꢀꢀ

沟槽的圆弧部

[0137]

7ca

ꢀꢀ

沟槽的第一圆弧部

[0138]

7cb

ꢀꢀ

沟槽的第二圆弧部

[0139]

19

ꢀꢀꢀ

雾化cvd装置(成膜装置)

[0140]

20

ꢀꢀꢀ

基板

[0141]

22a

ꢀꢀ

载气供给机构

[0142]

22b

ꢀꢀ

载气(稀释)供给机构

[0143]

23a

ꢀꢀ

载气流量调节阀

[0144]

23b

ꢀꢀ

载气(稀释)流量调节阀

[0145]

24

ꢀꢀꢀ

雾化发生源

[0146]

24a

ꢀꢀ

原料溶液

[0147]

25

ꢀꢀꢀ

容器

[0148]

25a

ꢀꢀ

水

[0149]

26

ꢀꢀꢀ

超声波振子

[0150]

27

ꢀꢀꢀ

供给管

[0151]

28

ꢀꢀꢀ

加热器

[0152]

29

ꢀꢀꢀ

排气口

[0153]

30

ꢀꢀꢀ

成膜室

[0154]

101a n-型半导体层

[0155]

101b n+型半导体层

[0156]

102

ꢀꢀ

p型半导体层

[0157]

103

ꢀꢀ

金属层

[0158]

104

ꢀꢀ

电介体层

[0159]

105a 肖特基电极

[0160]

105b 欧姆电极

[0161]

131a n-型半导体层

[0162]

131b 第一n+型半导体层

[0163]

131c 第二n+型半导体层

[0164]

132

ꢀꢀ

p型半导体层

[0165]

132a p

+

型半导体层

[0166]

134

ꢀꢀ

栅极绝缘膜

[0167]

135a 栅电极

[0168]

135b 源电极

[0169]

135c 漏电极

[0170]

170

ꢀꢀ

电源系统

[0171]

171

ꢀꢀ

电源装置

[0172]

172

ꢀꢀ

电源装置

[0173]

173

ꢀꢀ

控制电路

[0174]

180

ꢀꢀ

系统装置

[0175]

181

ꢀꢀ

电子电路

[0176]

182

ꢀꢀ

电源系统

[0177]

192

ꢀꢀ

变频器

[0178]

193

ꢀꢀ

变压器

[0179]

194

ꢀꢀ

整流mosfet

[0180]

195

ꢀꢀ

dcl

[0181]

196

ꢀꢀ

pwm控制电路

[0182]

197

ꢀꢀ

电压比较器

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1