半导体装置的制作方法

本发明涉及半导体装置。

背景技术:

1、以往,已知有具备在单一的基板上一体形成且并联连接的mosfet(metal oxidesemi-conductor field effect transistor:金属氧化膜半导体场效应型晶体管)和bjt(bipolar junction transistor:双极结型晶体管)的半导体装置(例如,参照日本国特开昭61-180472号公报及日本国特开昭61-225854号公报)。

技术实现思路

1、在上述的现有技术的半导体装置中,希望在漏电极与源电极之间确保所希望的耐压且同时使通态电阻等的损失减少。例如,在相当于bjt的结构中,希望通过抑制少数载流子的电流向基电极流入来使电流密度及电流放大系数提高。

2、本发明的方案的目的在于提供一种半导体装置,其能够确保所希望的耐压且同时使电流密度及电流放大系数提高,并实现能量效率的改善。

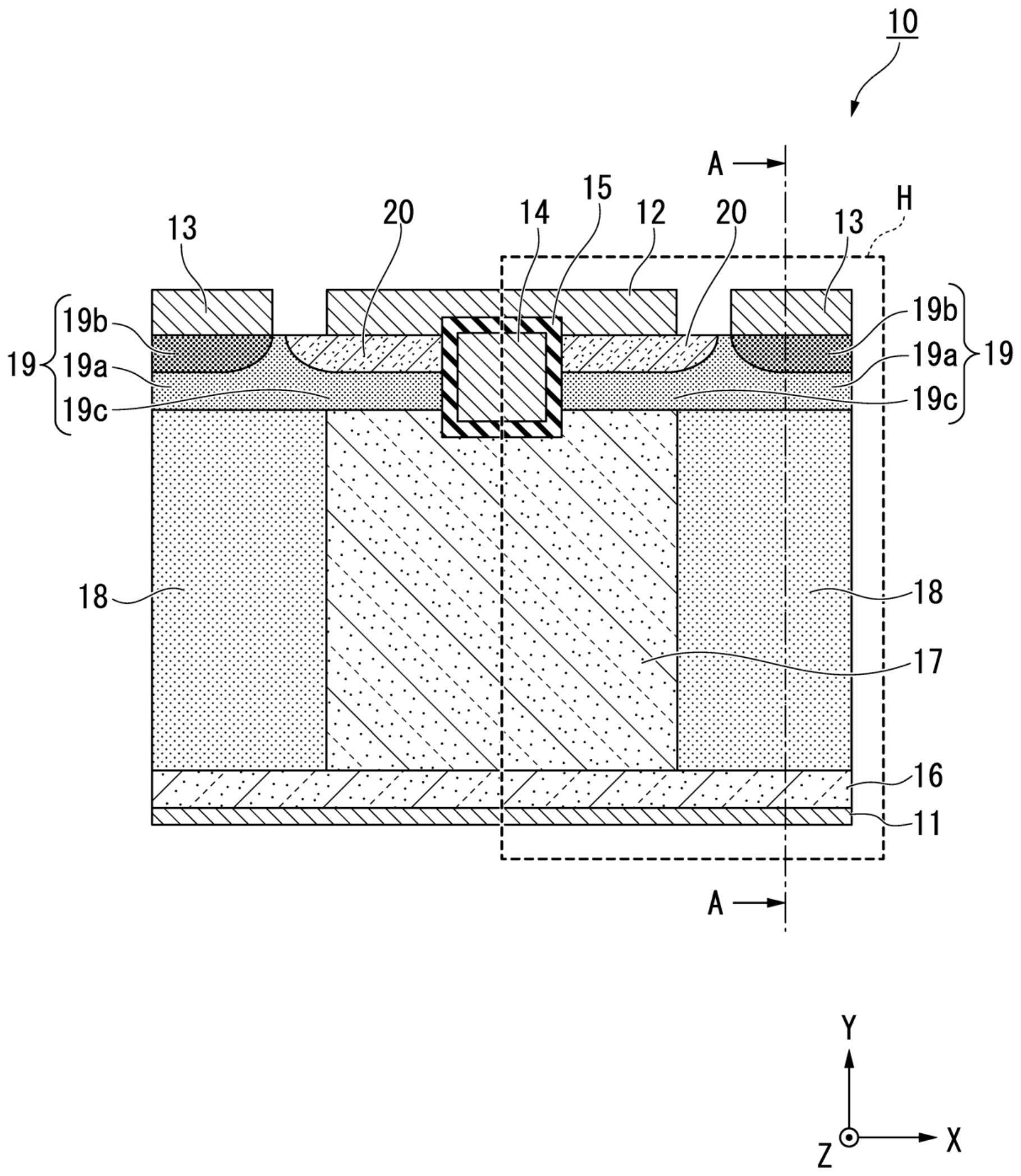

3、本发明的第一方案的半导体装置具备:第一导电型的第一半导体区域;第一电极,其与所述第一半导体区域接合;所述第一导电型的第二半导体区域;第二电极,其与所述第二半导体区域接合;第二导电型的第三半导体区域,其具有将所述第一半导体区域与所述第二半导体区域分隔的沟道部;以及第三电极,其与所述第三半导体区域接合,其中,所述第三半导体区域具备接点部,所述接点部与所述第三电极相邻,并且所述接点部的杂质浓度比所述第三半导体区域的其他的部位的杂质浓度相对大。

4、第二方案在上述第一方案所记载的半导体装置的基础上,也可以是,所述半导体装置具备所述第二导电型的第四半导体区域,所述第四半导体区域沿着所述第一半导体区域、所述沟道部及所述第二半导体区域顺次排列的方向与所述第三半导体区域相邻,并且沿着所述排列的方向的正交方向与所述第二半导体区域相邻。

5、第三方案在上述第一或第二方案所记载的半导体装置的基础上,也可以是,所述接点部的大小比与所述接点部的杂质浓度对应的少数载流子的扩散长度大。

6、根据上述第一方案,具备接点部,该接点部与第三电极相邻,并且杂质浓度比第三半导体区域的其他的部位的杂质浓度相对大,由此能够促进接点部的少数载流子的再耦合,抑制少数载流子向第三电极流入的情况。通过使向第三电极流动的电流中的载流子成分的比率增大,由此能够确保所希望的耐压且同时使电流密度及电流放大系数提高。

7、在上述第二方案的情况下,通过第一导电型的第二半导体区域与第二导电型的第四半导体区域以相邻的方式配置的所谓超结结构,由此确保所希望的耐压,且同时通过使第二半导体区域的杂质浓度增大而能够使电流密度提高。

8、通过具备接点部,由此能够抑制少数载流子经由超结结构中的第二导电型的第四半导体区域向第三电极流入的情况,能够使电流密度及电流放大系数提高。

9、在上述第三方案的情况下,接点部的大小比与接点部的杂质浓度对应的少数载流子的扩散长度大,由此能够促进接点部处的少数载流子的再耦合。

技术特征:

1.一种半导体装置,其中,

2.根据权利要求1所述的半导体装置,其中,

3.根据权利要求1或2所述的半导体装置,其中,

技术总结

本发明提供一种半导体装置。半导体装置(10)具备:n<supgt;+</supgt;源极层(20)及源电极(12);n<supgt;+</supgt;漏极层(16)、n<supgt;‑</supgt;漂移层(17)及漏电极(11);以及p基极层(19)及基电极(13)。p基极层(19)具有将n<supgt;+</supgt;源极层(20)与n<supgt;‑</supgt;漂移层(17)分隔的沟道部(19c)。半导体装置(10)具备第二接点部(19b),该第二接点部(19b)与基电极(13)相邻,并且杂质浓度比p基极层(19)的其他的部位的杂质浓度相对大。

技术研发人员:中村研贵,塚田能成,米田真也,前田康宏,根来佑树,小堀俊光

受保护的技术使用者:本田技研工业株式会社

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!